Устройство для синхронизации кодового сигнала

Иллюстрации

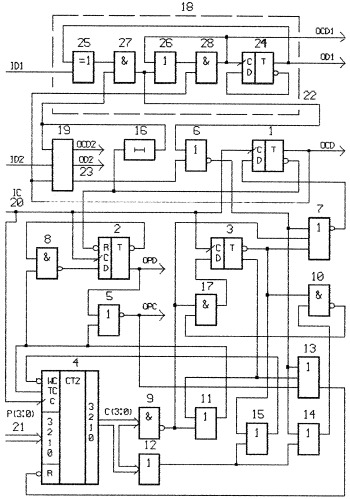

Показать всеУстройство для синхронизации кодового сигнала относится к импульсной цифровой технике, предназначено для выполнения полной функции синхронизации входного асинхронного кодового сигнала разрядности М≥2 (формирования на разрядных выходах синхронизированного кодового сигнала и его кодового синхросигнала и формирования на первом, втором и третьем выходах соответственно синхросигналов кодового сигнала, паузы и начала паузы) с заградительной фильтрацией синхронизации входного кодового сигнала как помехи при длительности его изменения, не превышающей пороговой длительности, отсчитываемой с помощью входной непрерывной последовательности тактовых импульсов, и может быть использовано при построении синхронных устройств для помехоустойчивого ввода асинхронных кодовых или разовых команд или данных и обмена информацией (командами и данными), например, между двумя синхронными устройствами, каждое из которых имеет собственную тактовую частоту синхронизации. Техническим результатом является повышение помехоустойчивости устройства и расширение его функциональных возможностей за счет выполнения с помощью входных тактовых импульсов IC полной функции синхронизации входного асинхронного кодового сигнала ID(1:M) разрядности М≥2 (формирования на разрядных выходах синхронизированного кодового сигнала OD(1:M) и его кодового синхросигнала OCD(1:M) и формирования на первом, втором и третьем выходах соответственно синхросигнала OCD кодового сигнала OD(1:M), синхросигнала паузы OPD и синхросигнала начала паузы ОРС) с заградительной фильтрацией синхронизации входного асинхронного кодового сигнала как помехи при длительности его изменения, не превышающей пороговой длительности P·Tic при Р≥2, где Tic - период тактовых импульсов, Р - пороговое число. Устройство содержит три триггера (1-3), двоичный синхронный счетчик (4), три элемента ИЛИ-НЕ (5-7), три элемента И-НЕ (8-10), пять элементов ИЛИ (11-15), элемент задержки (16), элемент И (17), разрядные входы асинхронного кодового сигнала ID(1:M) разрядности М≥2, М формирователей сигналов, в частности, при М=2 формирователи (18) и (19), тактовый вход (20), кодовый вход (21) порога обнаружения синхросигнала кодового сигнала, три выхода, являющиеся выходами триггеров (1), (2), элемента ИЛИ-НЕ (5) и выходами синхросигналов OCD кодового сигнала, паузы OPD, начала паузы ОРС соответственно, и разрядные выходы синхронизированного кодового сигнала OD(1:M) и его кодового синхросигнала OCD(1:M), являющиеся соответственно информационными выходами и выходами синхросигналов формирователей (18) и (19). 1 ил.

Реферат

Изобретение относится к импульсной цифровой технике, предназначено для выполнения полной функции синхронизации входного асинхронного кодового сигнала ID(1:M) разрядности M≥2 (формирования на разрядных выходах синхронизированного кодового сигнала OD(1:M) и его кодового синхросигнала OCD(1:M) и формирования на первом, втором и третьем выходах соответственно синхросигналов OCD кодового сигнала, паузы OPD и начала паузы ОРС, означающего обнаружение неизменности входного кодового сигнала в течение некоторого времени) с заградительной фильтрацией синхронизации входного кодового сигнала как помехи при длительности его изменения, не превышающей пороговой длительности, отсчитываемой с помощью входной непрерывной последовательности тактовых импульсов, и может быть использовано при построении синхронных устройств для помехоустойчивого ввода асинхронных кодовых или разовых команд или данных и обмена информацией (командами и данными), например, между двумя синхронными устройствами, каждое из которых имеет собственную тактовую частоту синхронизации.

Известно [1; 2, с.251, с.252], что при обмене информацией корректная синхронизация одноразрядного входного цифрового сигнала ID с помощью входных тактовых импульсов IC, по отношению к которым сигнал ID асинхронен, возможна при определении частоты 1/Tic тактовых импульсов IC исходя из условия

при выборе k≥4 с учетом быстродействия элементной базы устройства и реальных допусков на фазовое дрожание переходов (джиттер) сигнала ID, в определенных пределах периода сигнала ID,

где

T0id и T1id - длительность нулевой и единичной фаз неискаженного сигнала ID при ID=0 и ID=1 соответственно;

Tic - длительность периода входного тактового сигнала IC;

T0ic и Т1ic - длительность нулевой и единичной фаз тактового сигнала IC при IC=0 и IC=1 соответственно.

Принимая во внимание условие (1), для дальнейшего описания выполнение полной функции синхронизации кодового сигнала ID(1:M) с помощью тактовых импульсов IC определим как формирование выходного синхронизированного кодового сигнала OD(1:M) длительностью

и формирование выходных синхросигналов (синхронизирующих сигналов) OCD и OCD(1:M) длительностью

так, что OCD формируется при обнаружении любого изменения кодового сигнала ID(1:M), a OCDj формируется при обнаружении перехода j-го разряда IDj кодового сигнала ID(1:M) в противоположное состояние,

где

j - изменяется от 1 до М и является индексом j-го разряда любого из кодов (кодовых сигналов): ID(1:M), OD(1:M), OCD(1:M);

К - целое число, не меньшее 2.

Известно [3, с.41], что практически никакие методы экранирования и разнесения проводов линий цифровой связи от энергетических проводов не могут гарантировать отсутствие в линии связи (ЛС) помех (наводок). Это означает, что в общем случае входной асинхронный сигнал ID(1:M) маскируется помехами и задача его полной синхронизации должна решаться с учетом возможного искажения различными помехами каждой его компоненты IDj, в частности фазовыми помехами [4, с.103]: джиттером (jitter - дрожание) и вандером (wander - странствие), обусловленными, например, перекрестными помехами от других ЛС, пульсациями напряжений питания, дневными - ночными перепадами температуры и т.п.

Известно также [5], что в любом микроэлектронном устройстве можно выделить каналы связи для передачи сигналов, каждый из которых содержит источник сигнала, ЛС и приемник сигнала. Любой канал связи может быть как источником, так и приемником помех. В реальных условиях на каналы связи могут воздействовать несколько источников внешних индустриальных или естественных помех и внутренних помех с различными видами паразитных связей: емкостной, индуктивной, резистивной, комплексной.

Таким образом, при построении современных цифровых систем обработки информации и управления и их составных частей проблема учета помех практически всегда актуальна вследствие наличия различных внешних и внутренних помех, снижения энергетического уровня информационных сигналов, усложнения систем и их составных частей.

Кроме того, в отдельных случаях каждый переход компоненты IDj в противоположное состояние принципиально сопровождается переходным процессом длительностью Тпп≤Рп·Tic при некотором целом пороговом числе Рп, например, в случае передачи сигнала IDj по несогласованной ЛС для снижении энергетического уровня обмена информацией при Rjd>R (см., например, [6, с.117, рис.4.7]), где Rjd и R - входное сопротивление приемника сигнала IDj и волновое сопротивление ЛС соответственно. Описанный случай возможен, в частности, при обмене информацией по несогласованной ЛС импульсными сигналами трехуровневого кода RZ с возвратом к нулю по ГОСТ 18977-79 и РТМ 1495-75 (см., например, [3, с.27-40]. Подобная ситуация возникает при вводе команд от механических ключей, длительность Тпп упругих колебаний механических контактов которых лежит обычно в диапазоне 1...10 мс [7, с.117-119].

С учетом (1)-(3) в процессе синхронизации сигнала ID(1:M) в зависимости от длительности TXid перехода его из одного состояния в другое «X» определим на временной оси этот сигнал как помеху при

как корректный информационный сигнал при

или как сигнал с неопределенным (искаженным) временным параметром

который в процессе синхронизации может быть отнесен к помехе (4) или к корректному сигналу (5),

где

Р - пороговое целое число, не меньшее 1, выбираемое с учетом (1) и (2);

X=ID1+ID2·2+ID3·4+...+IDM·2(М-1) - число, изменяющееся от 0 до 2М-1 включительно.

Очевидно, что при искажении сигнала ID(1:M) всевозможными помехами наличие интервала неопределенности типа (6) длительностью Tic принципиально неустранимо, так как обусловлено асинхронностью любых изменений сигнала ID(1:M) относительно тактовых импульсов IC.

Известно [2; 7, с.119-120; 8, с.135-137; 9, с.205-207], что при проектировании любой цифровой системы (как совокупности асинхронных и/или синхронных автоматов с памятью) постоянно возникает необходимость синхронизировать входные асинхронные сигналы системы с работой ее устройств, функционирующих по тактовым импульсам одного или нескольких генераторов. В этой связи в цифровой технике задача синхронизации асинхронных сигналов является традиционной и известно большое число разнообразных устройств для синхронизации асинхронных цифровых сигналов по тактовым импульсам, например, [2, с.248, рис.8.3; 6, с.171, рис.5.27; 7, с.120, рис.3.19; 8, с.135, рис.4.10 б; 9, с.206, рис.6.26; 10, с.265, рис.14-3; 11] из технической литературы и [12-37] по патентной информации, которые работают по входным тактовым импульсам IC и синхронизируемому одноразрядному цифровому сигналу ID.

Основным недостатком любого из указанных выше устройств синхронизации является ограниченность функциональных возможностей, поскольку каждое из них является одноразрядным и явно не ориентировано на выполнение полной функции тактовой синхронизации одноразрядного цифрового сигнала ID (формирование OD и OCD соответственно с длительностями (2) и (3) и учетом определений (4)-(6)) при Х=0 (или 1) для помехоустойчивого ввода команд и/или данных в синхронное устройство или для обмена информацией между двумя синхронными устройствами, каждое из которых имеет собственную тактовую частоту синхронизации.

Здесь следует отметить, что при установленных входных информационных сигналах синхронизация (изменение состояния автомата с памятью) в асинхронной системе производится с помощью соответствующих синхроимпульсов (при формировании синхроимпульса с помощью IC, его длительность совпадает с длительностью T0ic нулевой или длительностью T1ic единичной фазы периода Tic=(T0ic+T1ic) тактовых импульсов IC), а в синхронной системе синхронизация осуществляется логически по функции «И», т.е. по фронтам (переходам из «0» в «1») или срезам (переходам из «1» в «0») тактовых импульсов IC и соответствующим синхросигналам, установленным до прихода фронта или среза IC, причем длительность каждого синхросигнала обычно кратна целому числу периодов Tic.

Кроме того, в настоящее время и на длительную перспективу основным методом обработки информации в цифровых системах является синхронный метод тактирования по фронтам или срезам одного или нескольких генераторов тактовых импульсов с помощью синхросигналов [7, с.121-123: 3.5. Введение в проблематику и методику проектирования автоматом с памятью].

На основании изложенного выше можно сказать, что для построения синхронных цифровых систем создание простого помехоустойчивого устройства для синхронизации кодового сигнала, реализующего полную функцию синхронизации сигнала ID(1:M), описанную с помощью соотношений (1)-(6), является актуальной технической задачей.

Из указанных выше устройств синхронизации цифровых сигналов лишь три технических решения [27; 29; 30] ориентированы на выполнение соответствующей функции синхронизации с учетом искажения помехами входного одноразрядного синхронизируемого цифрового сигнала ID.

Известно устройство [27], содержащее три триггера, элемент И-НЕ, вход синхронизируемого сигнала ID, соединенный с входом сброса и информационным входом первого триггера, прямой выход которого соединен с информационным входом второго триггера, прямой выход которого соединен с первым входом элемента И-НЕ и информационным входом и входом сброса третьего триггера, тактовый вход, соединенный с тактовыми входами первого и второго триггеров и вторым входом элемента И-НЕ, и выход инверсного синхроимпульса NOC1, соединенный с выходом элемента И-НЕ и тактовым входом третьего триггера, инверсный выход которого соединен с третьим входом элемента И-НЕ, причем входы сброса и установки всех триггеров являются асинхронными и инверсными, а неиспользуемые из них соединены с шиной Логической «1» устройства.

Обозначив сигналы на выходах первого, второго и третьего триггеров соответственно через Х1, Х2 и NX3 (где NX3=!X3 - инверсное значение Х3), функционирование устройства [27] как автомата с памятью опишем в виде последовательности переходов его из нулевого состояния (НС)

в переходное состояние

из ПС (8) обратно в НС (7) или в единичное состояние (ЕС)

из ЕС (9) в ПС (8) и т.д., причем функция «Q» является признаком ПС (8) устройства [27] и определяется логической формулой

где

«!=N», «&», «#» и «$» - здесь и везде далее на языке ABEL операторы операций «НЕ», «И» и «ИЛИ» и «Исключающее ИЛИ» соответственно;

Z - здесь и везде далее двоичная переменная, равная «0» или «1».

Каждый переход из НС (7) в ПС (8) инициируется переключением ID из «0» в «1», и при ID=1 по ближайшему фронту тактового сигнала 1C через время dT первый триггер устанавливается в Х1=1 и дальнейшее функционирование устройства [27] в зависимости от величины (T1id-dT) определится одним из двух случаев поведения сигнала ID в течение текущего периода Tic.

В первом случае при (T1id-dT)>Tic по следующему фронту сигнала IC второй триггер устанавливается в Х2=1, и по текущему значению IC=1 элемент И-НЕ генерирует выходной синхроимпульс NOC1=!IC=0 согласно логической формуле NOC1=!(X2&IC&NX3). Далее по фронту сигнала NOC1=0 третий триггер устанавливается в NX3=0, и устройство переходит в ЕС (9), в котором сигналом NX3=0 запрещена работа элемента И-НЕ по третьему входу.

Во втором случае при (T1id-dT)<Tic сигнал ID переключится из «1» в «0» и асинхронно сбросит первый триггер в течение текущего периода Tic (т.е. до первого фронта IC после установки первого триггера в Х1=1), т.е. устройство [27] из ПС (8) асинхронно перейдет в НС (7) и проигнорирует как помеху изменение во времени сигнала ID(t)=0→1→0 при (T1id-dT)<Tic.

Каждый переход из ЕС (9) в ПС (8) происходит по переключению ID из «1» в «0» так, что по ID=0 первый триггер асинхронно сбрасывается в Х1=0. При Х1=0 по ближайшему фронту тактового сигнала IC второй триггер переключается в Х2=0, асинхронно сбрасывает третий триггер в NX3=1, и устройство [27] переходит в НС (7).

Если устройство [27] находится в ЕС (8) и возникает кратковременная помеха ID=0 длительностью Tr≥2·Тз<<Tic (где Тз - средняя задержка распространения сигнала ID=0 через элемент первого триггера по входу сброса), то первый триггер асинхронно сбрасывается в Х1=0. После исчезновения этой помехи устройство [27] при ID=1 оказывается в помеховом ПС (8) при ID=1, X1=0, Х2=1 и NX3=0, и по ближайшему фронту тактового сигнала IC устройство [27] переходит в ПС (8) при ID=1, X1=1, Х2=0 и NX3=1. Далее, при ID=1 по следующему фронту сигнала IC второй триггер устанавливается в Х2=1 и по текущему значению IC=1 элемент И-НЕ генерирует помеховый выходной синхроимпульс NOC1=!IC=0, после окончания которого устройство [27] возвращается в ЕС (9).

Таким образом, по каждому корректному изменению асинхронного сигнала ID(t)=0→1→0 при ID(t)=1 в течение T1id≥2·Tic устройство [27] регулярно генерирует выходной синхроимпульс NOC1=!IC=0 в процессе перехода по графу НС (8)→ПС (8)→ЕС (9), а также попутно формирует синхронизированный сигнал X2=OD.

Кроме того, по каждому даже кратковременному помеховому переключению асинхронного сигнала ID(t) из «1» в «0» при ID(t)=0 в течение T0id≥2·Тз<<Tic в процессе перехода по графу ЕС (8)→ПС (8)→ЕС (8) устройство [27] генерирует помеховый выходной синхроимпульс NOC1=!IC=0.

Легко видеть, что устройство [27] целесообразно применять только в том случае, когда после перехода в ЕС (9) входной сигнал ID=1 устойчив, т.е. во времени отсутствуют помеховые изменения сигнала ID(t) из «1» в «0».

Основным недостатком устройства [27] является низкая помехоустойчивость в ЕС (9) и ограниченность функциональных возможностей (устройство тактовый синхросигнал OCD не формирует, а синхронизированный сигнал OD=X2 вырабатывает попутно), поскольку оно предназначено для помехоустойчивого формирования командного синхроимпульса NOC1 с заградительной фильтрацией синхронизации цифрового сигнала ID как помехи только для единичной фазы помехи при условии T1id≤Tic.

Известно устройство [29], содержащее пять триггеров с инверсными асинхронными входами сброса и установки, элементы И-НЕ с первого по 12-й, два элемента НЕ, вход синхронизируемого сигнала ID, вход тактового сигнала IC и выход инверсного синхроимпульса NOC1.

Обозначим сигналы на прямых и инверсных выходах триггеров с первого по пятый через Х1 и NX1, ..., Х5 и NX5 соответственно, на выходах элементов И-НЕ с первого по 12-й через Х6, ..., Х17 соответственно, а на выходах первого и второго элементов НЕ соответственно через X18=NID и X19=NIC.

С учетом принятой системы обозначений в процессе работы устройства [29] функционирование элементов И-НЕ описывается следующими формулами:

Введем переменную «Y» как признак переходного состояния устройства [29], определенный согласно логической формуле

В процессе функционирования устройства [29] его триггеры функционируют так, что первый устанавливается в Х1=1 по (Х6&Х7)=0 или сбрасывается в Х1=0 по Х8=0, второй устанавливается в Х2=1 по Х9=0 или сбрасывается в Х2=0 по Х10=0, третий устанавливается в Х3=1 по (Х11&Х12)=0 или сбрасывается в Х3=0 по Х13=0, четвертый устанавливается в Х4=1 по Х14=0 или сбрасывается в Х4=0 по Х15=0, пятый устанавливается в Х5=1 по Х16=0 или сбрасывается в Х5=0 по Х17=0.

С учетом (11)-(23) функционирование устройства [29] как автомата с памятью можно описать в виде последовательности переходов его из нулевого состояния (НС)

в переходное состояние (ПС)

по изменению ID из «0» в «1», а затем, возможно, в ПС (25) при ID=0, и из ПС (25) обратно в НС (24) или в единичное состояние (ЕС)

и из ЕС (26) в ПС (25) по изменению ID из «1» в «0», а из ПС (25) в НС (24) или обратно в ЕС (25).

Начальный переход устройства [29] из НС (24) (или ЕС (26)) в ПС (25) инициируется переключением ID из «0» в «1» (или из «1» в «0»), и при ID=1 (или ID=0) по ближайшему тактовому сигналу IC=1 формируется сигнал Х6=0 (или Х7=0), по которому первый триггер устанавливается в Х1=1 и дальнейшее функционирование устройства [29] определяется одним из трех случаев длительности TXid=T1id (или T0id): TXid≥(T1ic+2·T0ic); TXid≤T0ic; T0ic<TXid<(T1ic+2·T0ic).

В первом случае TXid≥(T1ic+2·T0ic) при ID=1 (или ID=0) и Х1=1 по сигналу X19=NIC=1 формируется Х9=0, по которому второй триггер устанавливается в Х2=1 и запрещает формирование Х6=0 (или Х7=0). Затем по Х2=1 и IC=1 формируется Х8=0, сбрасывающий первый триггер в Х1=0. Кроме того, по Х2=1 и IC=1 при NX3=1 и Х5=0 (или Х5=1) формируется Х14=ОМС1=0 (или X15=ONC0=0), устанавливающий (или сбрасывающий) четвертый триггер в Х4=1 (или Х4=0) так, что запрещается формирование Х6=0 (или Х7=0). Далее при Х1=0 и Х4=1 (или Х4=0) по X19=NIC=1 формируются Х10=0, сбрасывающий второй триггер в Х2=0, и Х16=0 (или Х17=0), устанавливающий (или сбрасывающий) пятый триггер в Х5=1 (или Х5=0), и устройство [29] оказывается в состоянии ЕС (26) (или НС (24)).

Во втором случае TXid≤T0ic и при Х1=1 и IC=0 сигнал ID переключится из «1» в «0» (или из «0» в «1). По Х1=1 и Х19=NIC=1 формируются Х9=0, устанавливающий второй триггер в Х2=1, и Х11=0 (или Х12=0), устанавливающий третий триггер в состояние NX3=0, запрещающее формирование Х14=0 (или Х15=0) при Х2=1 и Х5=0 (или Х5=1). Далее при ID=0 (или ID=1), X2=1 и Х3=1 по IC=1 формируется Х8=0, по которому первый триггер сбрасывается в Х1=0. Затем по NX1=1 и Х19=NIC=1 одновременно формируются Х10=0 и Х13=0, по которым второй и третий триггеры сбрасываются в нулевые состояния и устройство [29] из ПС (25) возвращается обратно в исходное состояние НС (24) (или ЕС (26)).

В третьем случае (при попадании сигнала ID в интервал неопределенности T0ic<TXid<(Tic+2·T0ic)) устройство будет функционировать неустойчиво, т.е. будет работать, как в первом или как во втором случае.

Основным недостатком устройства [29] является аппаратурная сложность (определяется количеством элементов в устройстве и числом связей между ними) и ограниченность его функциональных возможностей (устройство тактовый синхросигнал OCD не формирует, а синхронизированный сигнал OD=X4 вырабатывает попутно), поскольку оно предназначено для помехоустойчивого формирования командного синхроимпульса NOC1=Х14 (19) (или NOCO=Х15 (20)) с заградительной фильтрацией синхронизации как помехи цифрового сигнала ID при длительности его единичной T1id (или нулевой T0id) фазы, не превышающей длительности T0ic нулевой фазы тактового сигнала IC.

Из известных технических решений наиболее близким к предлагаемому является устройство [30], содержащее четыре триггера, двоичный счетчик, например четырехразрядный, формирующий на кодовом выходе кодовый сигнал С(3:0), восемь элементов И-НЕ, два элемента И, элемент ИЛИ-НЕ, три элемента НЕ, вход синхронизируемого цифрового сигнала ID, вход тактового сигнала IC и один выход, являющийся выходом синхроимпульса ONC1.

Обозначим сигналы на прямых и инверсных выходах триггеров с первого по четвертый через Х1 и NX1, ..., Х4 и NX4 соответственно, на выходах элементов И-НЕ с первого по восьмой через Х6, ..., Х13 соответственно, на выходах первого и второго элементов И через Х14 и Х15 соответственно, на выходе элемента ИЛИ-НЕ через Х16, на выходах первого, второго и третьего элементов НЕ соответственно через X17=!ID=NID, X18=!IC=NIC и X19=!X15=NX15.

С учетом принятой системы обозначений в процессе работы устройства [30] функционирование его комбинационных элементов описывается формулами:

Введем переменную «G» как признак переходного состояния устройства [30], определенный согласно логической формуле

В процессе функционирования устройства [30] его триггеры функционируют так, что первый устанавливается в Х1=1 по Х6=0 или сбрасывается в Х1=0 по Х7=0, второй устанавливается в Х2=1 по Х8=0 или сбрасывается в Х2=0 по Х9=0, третий устанавливается в Х3=1 по Х10=0 или сбрасывается в Х3=0 по Х11=0, четвертый устанавливается в Х4=1 по Х12=0 или сбрасывается в Х4=0 по Х13=0, а счетчик функционирует так, что по Х1=0 фиксируется в нулевом состоянии С(3:0)=0000, а при Х1=1 по фронту каждого импульса Х14=1, во времени, практически совпадающему со срезом каждого IC, содержимое этого счетчика, определяющее число

увеличивается на единицу.

С учетом (27)-(39) функционирование устройства [30] как автомата с памятью можно описать как последовательность переходов его из нулевого состояния (НС)

в переходное состояние (ПС)

по переходу ID из «0» в «1», а затем возможно в ПС (41) при ID=0, и из ПС (41) обратно в НС (40) или в единичное состояние (ЕС)

и из ЕС (42) в ПС (41) по переходу ID из «1» в «0», а из ПС (41) в НС (40) или обратно в ЕС (42).

Каждый переход из НС (40) в ПС (41) инициируется переключением ID из «0» в «1» так, что при ID=1 по ближайшему тактовому сигналу IC=1 формируется Х6=0, по которому первый триггер устанавливается в Х1=1, и дальнейшее функционирование устройства [30] определяется в зависимости от длительности T1id единичной фазы сигнала ID, одним из двух условий его работы:

где 16·Tic - порог обнаружения перехода сигнала ID из «0» в «1», определяемый коэффициентом пересчета «16» счетчика и периодом Tic.

Если устройство [30] находится в ПС (41) при ID=1, X1=1, С(3:0)=0000 и при условии (43) или (44), то по первому фронту сигнала Х14=NIC счетчик переходит в состояние С(3:0)=0001, практически одновременно вырабатываются сигналы Х16=0, Х15=0, Х6=1, Х7=1, Х12=1, Х13=1, Х19=1 и Х8=0, по которому второй триггер устанавливается в Х2=1. После этого по каждому фронту сигнала Х14=NIC содержимое счетчика увеличивается на «1».

Далее при условии (43) в некоторый момент времени сигнал ID переключается в «0», элемент 10 формирует сигнал Х10=0, по которому третий триггер переключается в Х3=1 и сигналом NX3=0 блокирует работу седьмого элемента И-НЕ. По шестнадцатому фронту сигнала Х14=NIC=1 счетчик переходит в нулевое состояние С(3:0)=0000, элемент ИЛИ-НЕ вырабатывает сигнал Х16=1 и в течение следующего периода Tic сначала по сигналу IC=1 формируются Х15=IC=1, Х7=NIC=0, первый триггер по Х7=0 сбрасывается в Х1=0 и фиксирует счетчик в нулевом состоянии, а затем по NX1=1 и Х19=NIC=1 одновременно вырабатываются сигналы Х9=!С=0 и Х11=IC=0, по которым второй и третий триггеры сбрасываются в Х2=0 и Х3=0, и при ID=0 устройство [30] возвращается в исходное состояние НС (40), а при ID=1 в начало ПС (41) при Х1=Х2=Х3=Х4=0, Х16=1.

При условии (44) и Х1=1, Х2=1 и NX3=1 по шестнадцатому фронту сигнала Х14=NIC=1 счетчик переходит в нулевое состояние С(3:0)=0000, элемент ИЛИ-НЕ вырабатывает сигнал Х16=1 и в течение следующего периода Tic сначала по сигналу IC=1 формируются Х15=IC=1, Х7=0 и X12=ONC1=NIC=0. По Х7=0 первый триггер сбрасывается в Х1=0 и фиксирует счетчик в нулевом состоянии, по Х12=0 четвертый триггер устанавливается в Х4=1 и сигналом NX4=0 блокирует работу первого элемента И-НЕ, а затем по NX1=1 и Х19=NIC=1 вырабатывается сигнал Х9=IC=0, по которому второй триггер сбрасываются в Х2=0, и устройство [30] при ID=1 оказывается в состоянии ЕС (42).

Если 16·Tic-T1ic≤T1id≤16·Tic+T0ic, то сигнал ID по аналогии с определением (6) характеризуется неопределенным временным параметром в интервале длительности Tic. В этом случае в зависимости от длительности между фронтом сигнала ID и первым фронтом тактовых импульсов IC при ID=1 устройство будет функционировать, как при условии (43) или как при условии (44).

Если устройство [30] находится в ЕС (42) и при Х15=IC=1 возникает кратковременная помеха ID=0 длительности T0id≥(T0ic+Tr), где Tr - минимальная длительность сигнала Х13=0, необходимая для гарантированного сброса четвертого триггера в Х4=0, то в соответствующий момент действия тактового сигнала IC=1 формируется сигнал Х13=0, по которому четвертый триггер сбрасывается в Х4=0. После исчезновения этой помехи устройство [30] при ID=1 оказывается в помеховом ПС (42), и в случае (44) в процессе каждого перехода из этого состояния в ЕС (42) устройство [30] вырабатывает ложный синхроимпульс Х12=ONC1=0 (33).

По каждому корректному изменению асинхронного сигнала ID(t)=0→1→0 при ID(t)=1 устройство [30] при условии (44) генерирует выходной импульс X12=ONC1=!IC=0 (33) в процессе перехода из ПС (41) в ЕС (42), а также попутно формирует синхронизированный сигнал X4=OD.

Кроме того, при IC=1 по каждому даже кратковременному помеховому изменению асинхронного сигнала ID(t)=1→0→1 при ID(t)=0 в течение T0id≥Tr в процессе перехода по графу ЕС (42) → помеховое ПС (41) → ЕС (42) устройство [30] генерирует помеховый выходной синхроимпульс Х12=NOC1=!IC=0 (33).

Таким образом, устройство [30] целесообразно применять только для заградительной фильтрации синхронизации изменений сигнала ID(t) в известном заранее переходном процессе длительности Tпп<(16·Tic-T1ic) при условии (43), а после перехода в ЕС (42) при условии (44) входной сигнал ID=1 устойчив, т.е. далее во времени отсутствуют помеховые изменения сигнала ID(t) из «1» в «0» при IC=1.

Основным недостатком устройства [30] является то, что при аппаратурной сложности (при построении устройства недостаточно полно использованы принципы суперпозиции логических функций и функциональные возможности составных частей устройства, например, сигналы Х9 (30) и Х11 (32) идентичны, при Х1=0 счетчик асинхронно зафиксирован в нулевом состоянии и на его тактовый вход может быть подан сигнал NIC с второго элемента НЕ с исключением первого элемента И) устройство характеризуется низкой помехоустойчивостью в состоянии ЕС (42) и ограниченностью функциональных возможностей (оно тактовый синхросигнал OCD не формирует, а синхронизированный сигнал OD=X4 вырабатывает попутно), поскольку устройство [30] предназначено для помехоустойчивого формирования командного синхроимпульса X12=ONC1 (33) с заградительной фильтрацией синхронизации цифрового сигнала ID как помехи только для заградительной фильтрации изменений сигнала ID(t) в известном заранее переходном процессе длительности Тпп при работе устройства при условии (43), а при условии (44), после перехода устройства в ЕС (42), входной сигнал ID=1 устойчив, т.е. далее во времени отсутствуют помеховые изменения сигнала ID из «1» в «0».

Предлагаемым изобретением решается задача повышения помехоустойчивости и комплексного расширения функциональных возможностей устройства за счет выполнения с помощью входных тактовых импульсов IC полной функции синхронизации входного асинхронного кодового сигнала ID(1:M) разрядности M≥2 (формирования на первом и втором кодовых выходах синхронизированного кодового сигнала OD(1:M) и его кодового синхросигнала OCD(1:M) соответственно и формирования на первом, втором и третьем одноразрядных выходах соответственно синхросигнала OCD синхронизированного кодового сигнала OD(1:M), синхросигнала паузы OPD и синхросигнала начала паузы ОРС) с заградительной фильтрацией синхронизации сигнала ID(1:M) как помехи при длительности TXid перехода его из одного состояния в другое состояние, не превышающей пороговой длительности P·Tic - см. (4).

Для достижения этого технического результата в устройство для синхронизации кодового сигнала, содержащее три триггера с прямыми и инверсными выходами и асинхронными инверсными входами сброса и установки, двоичный счетчик, содержащий тактовый вход, доминирующий асинхронный инверсный вход сброса и кодовый выход, первый элемент ИЛИ-НЕ, первый, второй и третий элементы И-НЕ, первый элемент И, тактовый вход и первый выход, дополнительно введены второй и третий выходы, второй и третий элементы ИЛИ-НЕ, пять элементов ИЛИ, элемент задержки, М≥2 формирователей сигналов, каждый из которых содержит информационный вход, вход синхронизации, вход стробирования, управляющий и информационный выходы и выход синхросигнала, разрядные входы асинхронного кодового сигнала, являющиеся информационными входами формирователей сигналов, кодовый вход порога обнаружения синхросигнала кодового сигнала, разрядные выходы синхронизированного кодового сигнала и кодового синхросигнала, соединенные соответствующим образом с информационными выходами и выходами синхросигналов формирователей сигналов, входы синхронизации которых соединены с прямым выходом первого триггера, являющегося выходом синхросигнала кодового сигнала и первым выходом устройства, тактовый вход которого соединен с тактовыми входами первого, второго и третьего триггеров и счетчика, который является синхронным и дополнительно снабжен прямым входом разрешения счета, инверсным входом разрешения записи, приоритетным относительно входа разрешения счета, и кодовым входом, соединенным с кодовым входом порога обнаружения синхросигнала кодового сигнала устройства, второй выход которого является выходом синхросигнала паузы и соединен с первым входом первого элемента ИЛИ-НЕ и прямым выходом второго триггера, инверсный выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с вторым входом первого элемента ИЛИ-НЕ, выходом первого элемента ИЛИ и входом разрешения счета счетчика, разрядные выходы кодового выхода которого соединены с входами вторых элементов И-НЕ и ИЛИ, управляющие выходы формирователей сигналов соединены с входами второго элемента ИЛИ-НЕ, выход которого соединен с первыми входами третьего элемента ИЛИ-НЕ и третьего и четвертого элементов ИЛИ, прямой выход третьего триггера соединен с вторым входом третьего элемента ИЛИ и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И-НЕ, первым входом первого элемента И и вторым входом третьего элемента ИЛИ-НЕ; выход которого соединен с информационным входом первого триггера, инверсный выход третьего триггера соединен с третьим входом третьего элемента ИЛИ-НЕ и первыми входами третьего элемента И-НЕ и пятого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и вторым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с информационным входом третьего триггера, входы сброса и разрешения записи счетчика соединены соответственно с выходами третьего и пятого элементов ИЛИ, третий выход устройства является выходом синхросигнала начала паузы и соединен с выходом первого элемента ИЛИ-НЕ и третьим входом третьего элемента ИЛИ, инверсный выход первого триггера соединен с входом сброса второго триггера и через элемент задержки связан с входами стробирования формирователей сигналов, каждый из которых содержит четвертый триггер, инверсный выход которого соединен с его информационным входом, элемент Исключающее ИЛИ, шестой элемент ИЛИ, второй и третий элементы И, информационный выход, соединенный с прямым выходом четвертого триггера и первым входом элемента Исключающее ИЛИ, выход которого соединен с первым входом второго элемента И, вход стробирования, являющийся вторым входом второго элемента И, информационный вход, являющийся вторым входом элемента Исключающее ИЛИ, выход синхросигнала, соединенный с тактовым входом четвертого триггера, выходом третьего элемента И и первым входом шестого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, вход синхронизации, являющийся вторым входом третьего элемента И, и управляющий выход, соединенный с выходом второго элемента И и вторым входом шестого элемента ИЛИ, при этом неиспользуемые входы сброса и установки всех триггеров устройства соединены с шиной Логической «1».

Авторам неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение разрядных входов асинхронного кодового сигнала разрядности М≥2, кодового входа порога обнаружения синхросигнала кодового сигнала, разрядных выходов синхронизированного кодового сигнала и его кодового синхросигнала, второго и третьего выходов соответственно синхросигналов паузы начала паузы, второго и третьего элементов ИЛИ-НЕ, пяти элементов ИЛИ, элемента задержи и М формирователей сигналов) предлагаемого устройства, которые по сравнению с прототипом [30] повышают помехоустойчивость устройства и комплексно расширяют его функциональные возможности за счет выполнения с помощью входных тактовых импульсов IC полной функции синхронизации входного асинхронного кодового сигнала ID(1:M) с заградительной фильтрацией синхронизации входного асинхронного кодового сигнала ID(1:M) как помехи при длительности TXid изменения сигнала ID(1:M), не превышающей программируемой пороговой длительности P·Tic для Р≥2 - см. (4).

На чертеже приведена электрическая функциональная схема устройства для синхронизации кодового сигнала, реализованного для М=2 и четырехразрядного двоичного синхронного счетчика и содержащего триггеры с первого 1 по третий 3, двоичный синхронный счетчик 4, содержащий тактовый вход, кодовый вход Р(3:0)=Р3Р2Р1Р0, кодовый выход С(3:0)=С3С2С1С0, доминирующий асинхронный инверсный вход сброса, вход разрешения счета и инверсный вход разрешения записи, приоритетный относительно входа разрешения счета, элементы ИЛИ-НЕ с первого 5 по третий 7, элементы И-НЕ с первого 8 по третий 10, элементы ИЛИ с первого 11 по пятый 15, элемент задержки 16, первый элемент 17 И, первый 18 и второй 19 формирователи сигналов, каждый из которых содержит информационный вход, вход синхронизации, вход стробирования, управляющий и информационный выходы и выход синхросигнала, тактовый вход 20, кодовый вход 21 порога обнаружения кодового сигнала, три выхода, разрядные входы асинхронного кодового сигнала ID(1:2), являющиеся информационными входами формирователей сигналов 18 и 19, разрядные выходы синхронизированного кодового сигнала OD(1:2) и кодового синхросигнала OCD(1:2), соединенные соответствующим образом с информационными выходами и выходами синхросигналов формирователей сигналов 18 и 19, входы синхронизации которых соединены с прямым выходом первого триггера 1, являющегося выходом синхросигнала OCD кодового сигнала и первым выходом устройства, тактовый вход 20 которого соединен с тактовыми входами первого 1, второго 2 и третьего 3 триггеров и счетчика 4, кодовый вход которого соединен с кодовым входом 21 порога обнаружения синхросигнала кодового сигнала устройства, второй выход которого является выходом синхросигнала паузы и соединен с первым входом первого элемента 5 ИЛИ-НЕ и прямым выходом второго триггера 2, инверсный выход которого соединен с первым входом первого элемента 8 И-НЕ, второй вход которого соединен с вторым входом первого элемента 5 ИЛИ-НЕ, выходом первого элемента 11 ИЛИ и входом разрешения счета счетчика 4, разрядные выходы кодового выхода С(3:0) которого соединены с входами второго элемента 9 И-НЕ и второго элемента 12 ИЛИ, управляющие выходы 22 и 23 соответственно формирователей сигналов 18 и 19 соединены с входами второго элемента 6 ИЛИ-НЕ, выход которого соединен с первыми входами третьего элемента 7 ИЛИ-НЕ и третьего 13 и четвертого 14 элементов