Реляционный процессор

Иллюстрации

Показать всеРеляционный процессор предназначен для выполнения операций реляционной алгебры, может быть использован для построения систем нечисловой обработки информации. Техническим результатом является расширение функциональных возможностей устройства за счет выполнения операций селекции, проекции и дополнения. Устройство содержит n компараторов, n-входовой элемент И, двухвходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, n двухвходовых элементов И, n m-разрядных шинных формирователей. 1 ил.

Реферат

Изобретение относится к машинам баз данных и может быть использовано для построения систем нечисловой обработки информации.

Известны реляционные процессоры, выполняющие операцию селекции (см., например, рис.5.11 на стр.208 в книге Озкарахан Э. Машины баз данных и управление базами данных. М.: Мир, 1989).

К причине, препятствующей достижению указанного ниже технического результата при использовании известных реляционных процессоров, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняются операции проекции и дополнения.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, реляционный процессор (рис.4.5 на стр.185 в книге Калиниченко Л.А., Рывкин В.М. Машины баз данных и знаний. М.: Наука, 1990), который содержит компаратор и выполняет операцию селекции.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняются операции проекции и дополнения.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения выполнения операций селекции, проекции и дополнения.

Указанный технический результат при осуществлении изобретения достигается тем, что в реляционном процессоре, содержащем компаратор, особенность заключается в том, что в него дополнительно введены n-1 аналогичных упомянутому компараторов, n-входовой элемент И, двухвходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, n двухвходовых элементов И, n m-разрядных шинных формирователей, причем выход i-го компаратора соединен с i-м входом n-входового элемента И, выход которого соединен с первым входом двухвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом i-го двухвходового элемента И, выход которого соединен с управляющим входом i-го m-разрядного шинного формирователя, управляющий вход i-го компаратора, второй вход i-го двухвходового элемента И и второй вход двухвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с i-м, (n+i)-м настроечными и управляющим входами реляционного процессора, подключенного входом i-го m-разрядного атрибута обрабатываемого кортежа, входом i-го m-разрядного атрибута эталонного кортежа и выходом m-разрядного i-го атрибута результирующего кортежа соответственно к первому, второму m-разрядному входу i-го компаратору и m-разрядному выходу i-го шинного формирователя, подключенного m-разрядным входом к первому m-разрядному входу i-го компаратора.

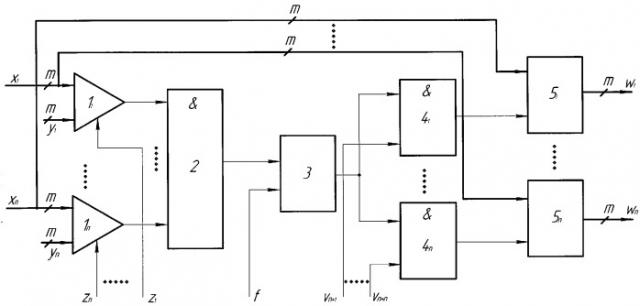

На чертеже представлена схема предлагаемого реляционного процессора.

Реляционный процессор содержит n-1 компараторов l1,...,ln, n-входовой элемент И 2, двухвходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, n двухвходовых элементов И 41,...,4n, n m-разрядных шинных формирователей 51,...,5n, причем выход компаратора 1i соединен с i-м входом элемента 2, выход которого соединен с первым входом элемента 3, выход которого соединен с первым входом элемента 4i, выход которого соединен с управляющим входом формирователя 5i, управляющий вход компаратора 1i, второй вход элемента 4i и второй вход элемента 3 соединены соответственно с i-м, (n+i)-м настроечными и управляющим входами реляционного процессора, подключенного входом i-го m-разрядного атрибута обрабатываемого кортежа, входом i-го m-разрядного атрибута эталонного кортежа и выходом i-го m-разрядного атрибута результирующего кортежа соответственно к первому, второму m-разрядным входам компаратора 1i и m-разрядному выходу формирователя 5i, подключенного m-разрядным входом к первому m-разрядному входу компаратора 1i.

Работа предлагаемого реляционного процессора осуществляется следующим образом. На первый и второй m-разрядный входы компаратора 1i подаются соответственно i-й m-разрядный атрибут хi обрабатываемого кортежа и i-й m-разрядный атрибут уi эталонного кортежа. На i-м, (n+i)-м настроечных и управляющем входах реляционного процессора фиксируются соответственно двоичные сигналы zi, Vn+i, f(zi, Vn+i, f∈{0,1}). Если при выполнении операции проекции результирующий кортеж должен (не должен) содержать i-й атрибут, то Vn+i=1(Vn+i=0). Если при выполнении операции селекции i-й атрибут присутствует (отсутствует) в эталонном кортеже, то zi=1 (zi=0). Для выполнения операции дополнения f=1 (в иных случаях f=0). Лог.0 (лог.1) на управляющем входе компаратора 1i запрещает (разрешает) его работу, при этом на его выходе формируется лог.1 (результат сравнения: лог.1 при хi=уi и лог.0 при хi≠уi). Лог.0 (лог.1) на управляющем входе m-разрядного формирователя 5i запрещает (разрешает) прохождение через него i-го m-разрядного атрибута, при этом на m-разрядном выходе этого формирователя будет присутствовать нулевой (указанный) атрибут. Таким образом, при Vn+i=...=Vn+n=1 и f=0, Z1=...=Zn=0 и f=0, Vn+1=...=Vn+n=1 и f=1 на m-разрядном выходе формирователя 5 соответственно имеем: (xi,yi,zi) - результат операции селекции

- результат операции проекции, (xi,yi,zi) - результат операции дополнения, где * - символ, обозначающий операцию умножения.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый реляционный процессор обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает выполнение операций селекции, проекции и дополнения.

Реляционный процессор, предназначенный для реализации операций селекции, проекции и дополнения, содержащий компаратор, отличающийся тем, что в него дополнительно введены n-1 аналогичных упомянутому компараторов, n-входовой элемент И, двухвходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, n двухвходовых элементов И, n m-разрядных шинных формирователей, причем выход i-го (i=1,n) компаратора соединен с i-м входом n-входового элемента И, выход которого соединен с первым входом двухвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом i-го двухвходового элемента И, выход которого соединен с управляющим входом i-го m-разрядного шинного формирователя, управляющий вход i-го компаратора, второй вход i-го двухвходового элемента И и второй вход двухвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с i-м, (n+i)-м настроечными и управляющим входами реляционного процессора, подключенного входом i-го m-разрядного атрибута обрабатываемого кортежа, входом i-го m-разрядного атрибута эталонного кортежа и выходом i-го m-разрядного атрибута результирующего кортежа соответственно к первому, второму m-разрядным входам i-го компаратора и m-разрядному выходу i-го шинного формирователя, подключенного m-разрядным входом к первому m-разрядному входу i-го компаратора.