Активная нагрузка дифференциальных усилителей

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, дифференциальных (ДУ) и операционных усилителях (ОУ), стабилизаторах напряжения и т.п.). Активная нагрузка дифференциальных усилителей содержит первый (1) и второй (2) токовые входы соответствующих первого (3) и второго (4) делителей тока, имеющих основные (5) и (6) и вспомогательные (7) и (8) токовые выходы, выходной буферный усилитель (9), выходное токовое зеркало (10), вход (11) которого связан с основным токовым выходом (5) первого делителя тока (3), а выход (12) подключен к основному токовому выходу (6) второго (4) делителя тока и входу (13) выходного буферного усилителя (9), имеющего потенциальный выход (14). Выходной буферный усилитель (9) выполнен на основе входного транзистора (15), база которого является входом (13) буферного усилителя (9), эмиттер входного транзистора (15) соединен с токовым выходом (16) дополнительного усилителя тока (17) и потенциальным выходом (14) буферного усилителя (9), а токовый вход (18) дополнительного усилителя тока (17) соединен со вспомогательным выходом (7) первого делителя тока (3). Технический результат - повышение точности передачи тока. 2 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, дифференциальных (ДУ) и операционных усилителях (ОУ), стабилизаторах напряжения и т.п.).

Известны схемы активных нагрузок дифференциальных усилителей (АН), реализованных на основе так называемых «токовых зеркал» [1-56] (фиг.1). Проблема повышения их точности (обеспечения единичной передачи тока со входа на выход) является одной из актуальных проблем аналоговой микросхемотехники. Однако в практических схемах аналоговых устройств получение единичной передачи по току токового зеркала Ki=Iвых.i/Iвх.i=1 решает проблему минимизации напряжения смещения нуля (Uсм) только в том случае, когда выходной буферный усилитель АН (фиг.1) имеет нулевой входной ток (Iвх.БУ=0). Если Iвх.БУ≠0, то необходим некоторый разбаланс входного напряжения ДУ Uвх=Uсм, при котором IДУ=Iвх.БУ+Iвых.i. Данное обстоятельство создает проблему обеспечения малых Uсм при использовании типовых активных нагрузок ДУ в практических схемах операционных усилителей. Комплексное решение этой задачи состоит в специальном построении токового зеркала и буферного усилителя, при котором в широком диапазоне температур, радиационных воздействий и статических режимов обеспечивается равенство токов IДУ=Iвх.i=Iвых.i+Iвх.БУ.

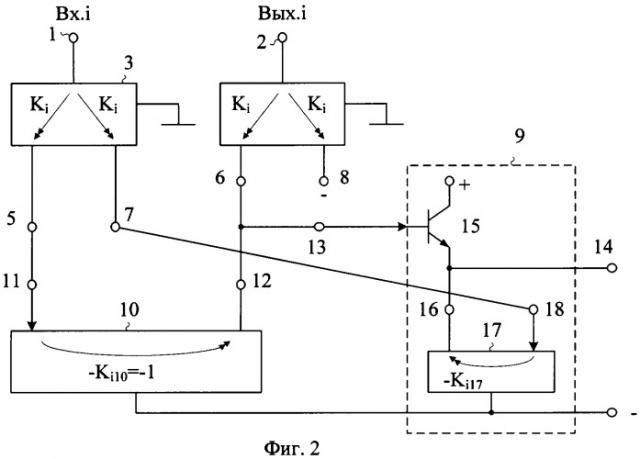

Ближайшим прототипом (фиг.1) заявляемого устройства является активная нагрузка дифференциальных усилителей, описанная в патенте фирмы Motorola (США) №4390850, содержащая первый 1 и второй 2 токовые входы соответствующих первого 3 и второго 4 делителей тока, имеющих основные 5 и 6 и вспомогательные 7 и 8 токовые выходы, выходной буферный усилитель 9, выходное токовое зеркало 10, вход 11 которого связан с основным токовым выходом 5 первого делителя тока 3, а выход 12 подключен к основному токовому выходу 6 второго 4 делителя тока и входу 13 выходного буферного усилителя 9, имеющего потенциальный выход 14.

Существенный недостаток известного устройства состоит в том, что оно не обеспечивает единичную передачу по току, что является основной причиной смещения нуля дифференциальных усилителей на его основе.

Основная цель предлагаемого изобретения состоит в повышении точности передачи тока АН при ненулевом входном токе выходного буферного усилителя 9.

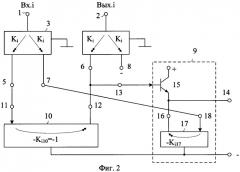

Поставленная цель достигается тем, что в активной нагрузке дифференциальных усилителей фиг.2, содержащей первый 1 и второй 2 токовые входы соответствующих первого 3 и второго 4 делителей тока, имеющих основные 5 и 6 и вспомогательные 7 и 8 токовые выходы, выходной буферный усилитель 9, выходное токовое зеркало 10, вход 11 которого связан с основным токовым выходом 5 первого делителя тока 3, а выход 12 подключен к основному токовому выходу 6 второго 4 делителя тока и входу 13 выходного буферного усилителя 9, имеющего потенциальный выход 14, предусмотрены новые связи - выходной буферный усилитель 9 выполнен на основе входного транзистора 15, база которого является входом 13 буферного усилителя 9, эмиттер входного транзистора 15 соединен с токовым выходом 16 дополнительного усилителя тока 17 и потенциальным выходом 14 буферного усилителя 9, а токовый вход 18 дополнительного усилителя тока 17 соединен со вспомогательным выходом 7 первого делителя тока 3.

На фиг.1 показана электрическая схема АН-прототипа.

На фиг.2 представлена обобщенная схема заявляемой АН в соответствии с п.1 формулы изобретения.

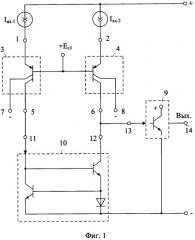

На фиг.3 показан частный случай реализации заявляемой АН, в которой выходное токовое зеркало 10 реализовано на транзисторах 19 и 20, а дополнительный усилитель тока 17 имеет коэффициент усиления Ki12.17=-2.

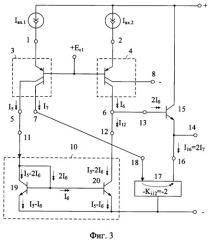

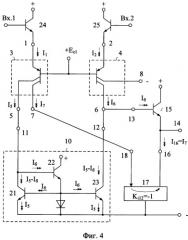

На фиг.4 показан другой частный случай выполнения АН, в котором выходное токовое зеркало 10 реализовано на транзисторах 21÷23, а в качестве источника сигнала используются транзисторы 24-25.

В схеме фиг.4 коэффициент усиления дополнительного усилителя тока 17 равен единице Ki17=-1.

На фиг.5 представлена схема заявляемой АН фиг.3 (п.2 формулы изобретения) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь систематическая составляющая напряжения смещения нуля Uсм=53 мкВ (без учета разброса параметров элементов). В качестве выходного токового зеркала 10 в данной схеме используется идеальный повторитель тока с коэффициентом передачи в 2 единицы.

На фиг.6 представлена схема заявляемой АН фиг.3 (п.2 формулы изобретения) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь систематическая составляющая напряжения смещения нуля Uсм=152 мкВ (без учета разброса параметров элементов). В качестве выходного токового зеркала 10 в данной схеме используется реальный повторитель тока на транзисторах VT25-VT27 с коэффициентом передачи в 2 единицы.

Активная нагрузка дифференциальных усилителей фиг.2 содержит первый 1 и второй 2 токовые входы соответствующих первого 3 и второго 4 делителей тока, имеющих основные 5 и 6 и вспомогательные 7 и 8 токовые выходы, выходной буферный усилитель 9, выходное токовое зеркало 10, вход 11 которого связан с основным токовым выходом 5 первого делителя тока 3, а выход 12 подключен к основному токовому выходу 6 второго 4 делителя тока и входу 13 выходного буферного усилителя 9, имеющего потенциальный выход 14. Выходной буферный усилитель 9 выполнен на основе входного транзистора 15, база которого является входом 13 буферного усилителя 9, эмиттер входного транзистора 15 соединен с токовым выходом 16 дополнительного усилителя тока 17 и потенциальным выходом 14 буферного усилителя 9, а токовый вход 18 дополнительного усилителя тока 17 соединен со вспомогательным выходом 7 первого делителя тока 3.

На фиг.3, в соответствии с п.2 формулы изобретения, коэффициент передачи по току дополнительного усилителя тока 17 равен двум.

На фиг.4, в соответствии с п.3 формулы изобретения, коэффициент передачи по току дополнительного усилителя тока 17 равен единице.

Рассмотрим работу схемы фиг.3.

В статическом режиме в схеме АН фиг.3 устанавливаются токи, показанные на данном чертеже, где обозначено: Iб - ток базы n-p-n транзисторов при IЭ=I5=I6=I7≈Iвх.1=Iвх.2. Единичная передача по току АН реализуется, если ток выхода 6 равен сумме тока I12=I5-2Iб и тока базы транзистора 5 (Iб5=2Iб):

Для обеспечения равенства I6=I5 необходимо, чтобы

Условие (2) выполняется, если коэффициент усиления по току дополнительного усилителя 17 равен двум.

Таким образом, при данном конкретном построении выходного токового зеркала 10 фиг.3 дополнительный усилитель тока 17 должен иметь вполне определенное значение коэффициента Кi12=-2 (п.2).

Если выходное токовое зеркало 10 имеет другое построение (фиг.4, транзисторы 21, 22, 23), то для получения единичной передачи по току АН фиг.4 необходимо, чтобы параметр Кi12 дополнительного усилителя тока 17 удовлетворял условию Ki12=-1. Данное требование оговаривается в п.3 формулы изобретения.

Таким образом, предлагаемая АН характеризуется более высокой точностью передачи тока, что позволяет создавать на ее основе прецизионные аналоговые микросхемы.

Данный вывод подтверждается результатами компьютерного моделирования схем (фиг.5 - фиг.6) - при отсутствии разброса параметров транзисторов заявляемая АН обеспечивает в ОУ более чем на порядок меньшие значения напряжения смещения нуля.

Источники информации

1. Патент РФ №1329639.

2. Патент США №3681623.

3. Патент США №3813607.

4. Патент США №3835410.

5. Патент США №4008441 H03f 3/16.

6. Патент США №4013973.

7. Патент США №4030044 (фиг.3).

8. Патент США №4057763.

9. Патент США №4095189.

10. Патент США №4117417.

11. Патент США №4241315.

12. Патент США №4345213.

13. Патент США №4412186 H03f 3/04.

14. Патент США №4462005 H03f 3/04.

15. Патент США №4471236.

16. Патент США №4473794.

17. Патент США №4567444.

18. Патент США №4591804 H03f 3/04.

19. Патент США №4769619.

20. Патент США №4855686.

21. Патент США №4879524 H03f 3/26.

22. Патент США №4897614.

23. Патент США №4937515 G05f 3/26.

24. Патент США №4990864.

25. Патент США №5053718.

26. Патент США №5079518 Н03К 3/16.

27. Патент США №5164658.

28. Патент США №5357188 G05f 3/26.

29. Патент США №5373253.

30. Патент США №5394079 G05f 3/16.

31. Патент США №5399991.

32. Патент США №5512815 G05f 3/16.

33. Патент США №5572114.

34. Патент США №5633612.

35 Патент США №5721512.

36. Патент США №5933055.

37. Патент США №5969574.

38. Патент США №5986507.

39. Патент США №6016050.

40. Патент США №6570438.

41. Патент США №6573795.

42. Патент США №6586918.

43. Патент США №6606001.

44. Патент США №6291977.

45. Патент США №6300803.

46. Патент США №6528981.

47. Патент США №6630818.

48. Патент США №6633198.

49. Патент США №6639452.

50. Патент США №6657481.

51. Патент США №6677807.

52. Патент США №6680605.

53. Патент США №6816014.

54. Патент РФ RU 2193273.

55. Патентная заявка США 2004/081688.

56. Патентная заявка США 2003/0030492.

1. Активная нагрузка дифференциальных усилителей, содержащая первый (1) и второй (2) токовые входы соответствующих первого (3) и второго (4) делителей тока, имеющих основные (5) и (6) и вспомогательные (7) и (8) токовые выходы, выходной буферный усилитель (9), выходное токовое зеркало (10), вход (11) которого связан с основным токовым выходом (5) первого делителя тока (3), а выход (12) подключен к основному токовому выходу (6) второго (4) делителя тока и входу (13) выходного буферного усилителя (9), имеющего потенциальный выход (14), отличающаяся тем, что выходной буферный усилитель (9) выполнен на основе входного транзистора (15), база которого является входом (13) буферного усилителя (9), эмиттер входного транзистора (15) соединен с токовым выходом (16) дополнительного усилителя тока (17) и потенциальным выходом (14) буферного усилителя (9), а токовый вход (18) дополнительного усилителя тока (17) соединен со вспомогательным выходом (7) первого делителя тока (3).

2. Устройство по п.1, отличающееся тем, что коэффициент передачи по току дополнительного усилителя тока (17) равен двум.

3. Устройство по п.1, отличающееся тем, что коэффициент передачи по току дополнительного усилителя тока (17) равен единице.