Дифференциальный усилитель с повышенным входным сопротивлением

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), широкополосных и избирательных усилителях, фильтрах и т.п.). Дифференциальный усилитель с повышенным входным сопротивлением содержит входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) выходы, транзистор источника опорного тока (6), коллектор которого связан с общей эмиттерной цепью (7) входного параллельно-балансного каскада (1), а эмиттер соединен с шиной источника питания (8) через токостабилизирующий двухполюсник (9), первый (10) и второй (11) вспомогательные транзисторы, базы которых соединены с первым (2) и вторым (3) входами параллельно-балансного каскада (1), а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости. База транзистора источника опорного тока (6) связана с объединенными эмиттерами первого (10) и второго (11) вспомогательных транзисторов, коллектор первого (10) вспомогательного транзистора соединен со вторым (3) входом входного параллельно-балансного каскада (1), а коллектор второго (11) вспомогательного транзистора связан с первым (2) входом входного параллельно-балансного каскада. Технический результат - повышение входного сопротивления. 1 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов датчиков с высоким внутренним сопротивлением, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), широкополосных и избирательных усилителях, фильтрах и т.п.).

Известны схемы дифференциальных усилителей (ДУ) с параллельным включением двух параллельно-балансных каскадов [1-15]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса наряду с одиночными параллельно-балансными каскадами стали основным усилительным элементом многих микросхем аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

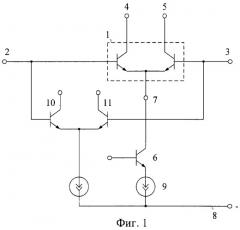

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №6917257 В2, H03F 3/45, содержащий входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 выходы, транзистор источника опорного тока 6, коллектор которого связан с общей эмиттерной цепью 7 входного параллельно-балансного каскада 1, а эмиттер соединен с шиной источника питания 8 через токостабилизирующий двухполюсник 9, первый 10 и второй 11 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами параллельно-балансного каскада 1, а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости.

Существенный недостаток известного ДУ состоит в том, что он имеет небольшое входное дифференциальное сопротивление (Rвх), зависящее от абсолютных значений коэффициента усиления по току базы (β) применяемых транзисторов и их статического режима. Для повышения в известных ДУ применяется местная отрицательная обратная связь (вводятся эмиттерные резисторы). Однако при этом ухудшаются многие параметры ДУ - коэффициент усиления по напряжению, напряжение смещения нуля, коэффициент подавления помехи по питанию, крутизна усиления ДУ и др.

Основная цель предлагаемого изобретения состоит в повышении на один-два порядка входного сопротивления ДУ.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 выходы, транзистор источника опорного тока 6, коллектор которого связан с общей эмиттерной цепью 7 входного параллельно-балансного каскада 1, а эмиттер соединен с шиной источника питания 8 через токостабилизирующий двухполюсник 9, первый 10 и второй 11 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами параллельно-балансного каскада 1, а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости, предусмотрены новые связи - база транзистора источника опорного тока 6 связана с объединенными эмиттерами первого 10 и второго 11 вспомогательных транзисторов, коллектор первого 10 вспомогательного транзистора соединен со вторым 3 входом входного параллельно-балансного каскада 1, а коллектор второго 11 вспомогательного транзистора связан с первым 2 входом входного параллельно-балансного каскада.

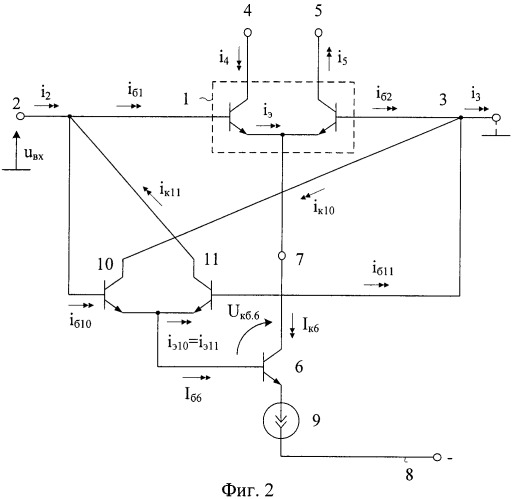

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

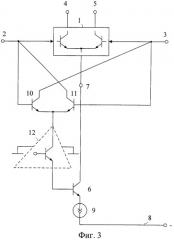

На фиг.3 представлена схема дифференциального усилителя, соответствующего п.2 формулы изобретения.

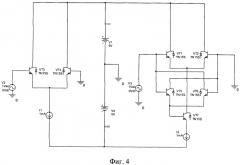

На фиг.4 показаны схемы известного и заявляемого ДУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

График фиг.5 иллюстрирует частотную зависимость входного дифференциального сопротивления известного и заявляемого устройств.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 выходы, транзистор источника опорного тока 6, коллектор которого связан с общей эмиттерной цепью 7 входного параллельно-балансного каскада 1, а эмиттер соединен с шиной источника питания 8 через токостабилизирующий двухполюсник 9, первый 10 и второй 11 вспомогательные транзисторы, базы которых соединены с первым 2 и вторым 3 входами параллельно-балансного каскада 1, а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости. База транзистора источника опорного тока 6 связана с объединенными эмиттерами первого 10 и второго 11 вспомогательных транзисторов, коллектор первого 10 вспомогательного транзистора соединен со вторым 3 входом входного параллельно-балансного каскада 1, а коллектор второго 11 вспомогательного транзистора связан с первым 2 входом входного параллельно-балансного каскада.

На фиг.3, в соответствии с п.2 формулы изобретения, база транзистора источника опорного тока 6 связана с эмиттерами первого 10 и второго 11 вспомогательных транзисторов через согласующий усилитель тока 12.

Рассмотрим работу схемы фиг.2.

Если на вход 2 подается напряжение uвх, то это вызывает приращение тока базы

где β1>>1 - коэффициент усиления по току базы левого входного транзистора каскада 1;

- сопротивление эмиттерного перехода входных транзисторов каскада 1;

ϕт=26 мВ - температурный потенциал;

Iэi=Iэ1=Iэ2=Iк6/2 - статический эмиттерный ток входных транзисторов каскада 1;

I9 - ток через двухполюсник 9.

Аналогично можно найти ток базы iб10 транзистора 10

где β10 - коэффициент усиления по току базы транзистора 10;

- сопротивления эмиттерных переходов транзисторов 10 и 11.

С другой стороны, эмиттерный и коллекторный токи транзисторов 10 и 11

Входной ток ДУ определяется суммой токов

С учетом (3) и (2) находим, что коллекторный ток транзистора 11 определяется формулой:

Поэтому

где увх - входная проводимость ДУ, причем

В ДУ-прототипе входная проводимость принимает достаточно большое значение:

Таким образом, в заявляемой схеме увх улучшается в N раз, где

Полученные выше теоретические выводы подтверждаются результатами моделирования в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» (фиг.5), выигрыш по Rвх - более чем на порядок.

Источники информации

1. Авт.св. СССР №459780.

2. Патент Японии JP 2004040157.

3. Патентная заявка США №2004/0061544.

4. Патентная заявка США №2003/0155959.

5. Патентная заявка США №2003/0141919.

6. Патент США №6292033.

7. Патент США №5936468.

8. Патент США №4866397.

9. Патент США №4331929.

10. Патент DE №10321442.

11. Патент США №6262628.

12. Патент США №6172551.

13. Патент США №5461342.

14. Патент США №5373741.

15. Патент США №6917257.

1. Дифференциальный усилитель с повышенным входным сопротивлением, содержащий входной параллельно-балансный каскад (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) выходы, транзистор источника опорного тока (6), коллектор которого связан с общей эмиттерной цепью (7) входного параллельно-балансного каскада (1), а эмиттер соединен с шиной источника питания (8) через токостабилизирующий двухполюсник (9), первый (10) и второй (11) вспомогательные транзисторы, базы которых соединены с первым (2) и вторым (3) входами параллельно-балансного каскада (1), а эмиттеры связаны друг с другом, причем все основные транзисторы схемы имеют один тип проводимости, отличающийся тем, что база транзистора источника опорного тока (6) связана с объединенными эмиттерами первого (10) и второго (11) вспомогательных транзисторов, коллектор первого (10) вспомогательного транзистора соединен со вторым (3) входом входного параллельно-балансного каскада (1), а коллектор второго (11) вспомогательного транзистора связан с первым (2) входом входного параллельно-балансного каскада.

2. Дифференциальный усилитель по п.1, отличающийся тем, что база транзистора источника опорного тока (6) связана с объединенными эмиттерами первого (10) и второго (11) вспомогательных транзисторов через согласующий усилитель тока (12).