Высокоскоростное многоканальное устройство для передачи данных между компьютером и периферийными устройствами, выполненное в виде универсальной последовательной шины

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, а именно к области локальных компьютерных сетей. Техническим результатом является увеличение максимальной скорости передачи данных между компьютером и периферийными устройствами до 480 Мбит/с при одновременном увеличении количества каналов передачи данных с подключаемыми периферийными устройствами и длины используемого кабеля, по которому могут передаваться пакеты цифровой информации, в том числе и с высокой скоростью. Устройство содержит компьютер, сигнальные линии (СЛ1, СЛ2), четыре кабеля, микросхему контроллера компьютера, микросхемы контроллеров периферийных устройств, микросхемы контроллеров хабов (X1, Х2) и универсальной последовательной шины, согласованные нагрузки (СН1, ..., СН10), стабилизаторы напряжения (СТН1, СТН2), фильтры (Ф1, ..., Ф5), предназначенные для уменьшения шума по питанию, схемы коррекции (СК1, ..., СК4) переходной характеристики сигнальных линий кабеля, общую шину (ОШ1), шину питания (ШП1), источник питания (ИП1), а также N каналов передачи данных КПД1, ..., КПДМ. 1 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к вычислительной технике, а именно к области локальных компьютерных сетей на универсальных последовательных шинах.

Известны последовательные шины передачи данных, предназначенные для периферийных устройств типа «мыши», клавиатуры, принтера, модема и жесткого диска [1].

Известно также устройство для передачи данных между компьютером и периферийными устройствами, выполненное в виде универсальной последовательной шины, включающее кабель с сигнальными линиями, шинами питания и разъемами на концах для соединения периферийных устройств с персональным компьютером, микросхему контроллера, формирующего команды, определяющие работу периферийного устройства, и микросхему, расположенную в периферийном устройстве [2].

Недостатками указанных устройств для связи персонального компьютера с периферийными устройствами являются:

- ограничения по расстоянию передачи пакетов цифровой информации,

- высокая сложность, обусловленная сложностью электрических ретрансляторов сигнала,

- высокая сложность, обусловленная наличием устройств - разветвителей кабелей.

Наиболее близким к изобретению является устройство для передачи данных между компьютером и периферийными устройствами [3], выполненное в виде универсальной последовательной шины, включающее кабель с сигнальными линиями, шинами питания и разъемами на концах для соединения периферийных устройств с персональным компьютером, микросхему контроллера компьютера, формирующего команды, определяющие работу периферийного устройства, микросхему контроллера устройства, управляющего направлениями потоков передаваемых данных, расположенную в периферийном устройстве, в котором содержатся, по крайней мере, две микросхемы-ретранслятора первым и вторым внешними электродами, соединенные с выходами микросхем контроллеров, а третьим и четвертым внешними электродами соединенные с кабелем, согласующие импедансы кабеля и контроллеров и преобразующие уровни сигналов с выходов микросхем контроллеров, расположенных в персональном компьютере и периферийном устройстве, для обеспечения их передачи по кабелю без отражения сигналов в нем.

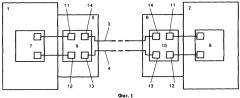

Функциональная схема устройства согласно прототипу [3] для передачи данных между персональным компьютером и периферийным устройством иллюстрируется фиг.1 и 2.

Устройство для передачи данных между персональным компьютером 1 и периферийными устройствами 2, приведенное на фиг.1 и выбранное в качестве прототипа, выполнено в виде универсальной последовательной шины, включает кабель с сигнальными линиями 3 и 4, шинами питания (не показаны) и разъемами 5 и 6 на концах для соединения периферийных устройств с персональным компьютером, микросхему контроллера 7 компьютера, формирующего команды, определяющие работу периферийного устройства, микросхему контроллера 8 устройства, управляющего направлениями потоков передаваемых данных, расположенную в периферийном устройстве 2. Устройство дополнительно содержит две идентичные микросхемы 9 и 10, функциональная блок-схема которых приведена на фиг.2. Микросхемы первым 11 и вторым 12 внешними электродами соединены с выходами микросхем контроллеров 7 и 8, а третьим 13 и четвертым 14 внешними электродами - с сигнальными линиями 3 и 4 кабеля. Микросхемы 9 и 10 согласовывают импедансы кабеля и контроллеров и преобразуют уровни сигналов с выходов микросхем контроллеров 7 и 8, расположенных в персональном компьютере 1 и периферийном устройстве 2, для передачи их по кабелю без отражения.

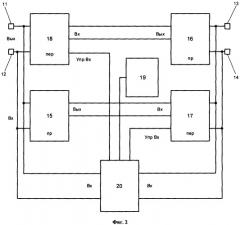

Как показано на фиг.2, каждая дополнительная микросхема 9 и 10 содержит первый и второй приемники 15 и 16, соединенные дифференциальными входами соответственно с первым 11, вторым 12, третьим 13 и четвертым 14 внешними электродами микросхем 9 и 10, а выходами - со входами соответственно первого и второго передатчика 17 и 18, которые дифференциальными выходами подключены к третьему 13 и четвертому 14, первому 11 и второму 12 внешним электродам микросхем 9 и 10. Микросхемы 9 и 10 содержат таймерное устройство 19, подключенное к логическому блоку 20, входы которого подключены к выходам приемников, а выходы - к управляющим входам первого и второго передатчиков 17 и 18, вырабатывающему для передатчиков сигналы разрешения передачи данных на внешние электроды 11, 12, 13, 14 микросхем 9 и 10.

Анализ технического решения, заявленного в прототипе [3], показывает, что оно не полностью устраняет недостатки известных устройств, используемых для связи персонального компьютера с периферийными устройствами.

Так серьезным недостатком устройства, заявленного в прототипе [3], является принципиальное ограничение длины линий связи 3 и 4 в устройстве передачи данных величиной порядка 25 м. Это обусловлено тем, что в прототипе не учтено:

1) наличие у переходной характеристики сигнальной линии кабеля участка весьма медленного нарастания вблизи стационарного значения, которое приводит к существенному влиянию на искажение формы импульсных сигналов в цифровых пакетах информации и, как следствие, к существенному увеличению джиттера (отклонения показательных участков сигнала от их требуемого положения во времени),

2) падение напряжения на шинах питания, что приводит к увеличению джиттера цифровых сигналов,

3) не учтено влияние шумов на величину джиттера при больших длинах сигнальной линии кабеля.

В прототипе не обеспечено согласование в полном объеме волнового сопротивления кабеля с выходом микросхемы-ретранслятора из-за реальных разбросов номиналов резисторов в технологии изготовления интегральных микросхем. Кроме того, ограничиваются типы кабелей и их параметры. Микросхемы ретрансляторов необходимо разрабатывать под каждое номинальное значение волнового сопротивления кабеля. Максимальная скорость передачи данных в прототипе не является высокой и составляет 12 Мбит/с.

Задачей, на решение которой направлено изобретение, является достижение следующих технических результатов:

1) увеличение максимальной скорости передачи данных между компьютером и периферийными устройствами в 40 раз до 480 Мбит/с,

2) увеличение количества каналов передачи данных с подключаемыми периферийными устройствами,

3) увеличение длины используемого кабеля, по которому могут передаваться пакеты цифровой информации, в том числе и с высокой скоростью, до значения, ограниченного только протоколом обмена данных (ответа) в последовательной шине в соответствии со спецификацией этой шины, а также в возможности согласования волнового сопротивления кабеля при использовании различного типа кабелей за счет использования микросхем контроллера хаба универсальной последовательной шины с возможностью подключения внешних согласованных нагрузок и обеспечения необходимой скорости передачи данных, схем коррекции переходной характеристики кабеля, дополнительных стабилизаторов напряжения, источников питания и фильтров, предназначенных для уменьшения шума по питанию.

Для достижения названного технического результата в устройство для передачи данных между компьютером и периферийными устройствами [3], выполненное в виде универсальной последовательной шины, включающее кабель с сигнальными линиями, шинами питания, микросхему контроллера компьютера, формирующего команды, определяющие работу периферийного устройства, микросхему контроллера устройства, управляющего направлениями потоков передаваемых данных, расположенную в первом периферийном устройстве, дополнительно включают новые элементы, являющимися существенными признаками изобретения: первую микросхему контроллера хаба универсальной последовательной шины, у которой первый и второй выводы восходящего порта соединены соответственно с первым и вторым выводами микросхемы контроллера компьютера, а также соединены соответственно через первую и вторую согласованные нагрузки с третьим и четвертым выводами восходящего порта первой микросхемы контроллера хаба универсальной последовательной шины, третий вывод микросхемы контроллера компьютера является общим выводом и соединен с пятым выводом первой микросхемы контроллера хаба универсальной последовательной шины, первым выводом первого стабилизатора напряжения, первыми выводами первого и второго фильтров, предназначенных для уменьшения шума по питанию, шестой вывод первой микросхемы контроллера хаба универсальной последовательной шины соединен со вторыми выводами первого фильтра, предназначенного для уменьшения шума по питанию, и первого стабилизатора напряжения, четвертый вывод микросхемы контроллера компьютера является выводом питания и соединен со вторым выводом второго фильтра, предназначенного для уменьшения шума по питанию, и третьим выводом первого стабилизатора напряжения, а также N каналов передачи данных, каждый j-й из которых содержит L последовательно соединенных удлинителей универсальной последовательной шины, включая первый удлинитель универсальной последовательной шины, промежуточные (s=2, ..., L-1) удлинители универсальной последовательной шины и последний L-й удлинитель универсальной последовательной шины, при этом первый и второй выводы первого удлинителя универсальной последовательной шины являются соответственно первым и вторым выводами канала передачи данных, первый вывод первого удлинителя универсальной последовательной шины через первую схему коррекции переходной характеристики кабеля соединен с первым выводом третьей согласованной нагрузки, второй вывод которой соединен с третьим выводом канала передачи данных, второй вывод первого удлинителя универсальной последовательной шины через вторую схему коррекции переходной характеристики кабеля соединен с первым выводом четвертой согласованной нагрузки, второй вывод которой соединен с четвертым выводом канала передачи данных, третий и четвертый выводы первого удлинителя универсальной последовательной шины соединены соответственно с первым и вторым выводами третьего фильтра, предназначенного для уменьшения шума по питанию, и являются соответственно пятым и шестым выводами канала передачи данных, при этом первый, второй, третий и четвертый выводы s-го (s=2, ..., L-1) удлинителя универсальной последовательной шины соединены соответственно с пятым, шестым, седьмым и восьмым выводами (s-1)-го удлинителя универсальной последовательной шины, а пятый, шестой, седьмой и восьмой выводы s-го удлинителя универсальной последовательной шины соединены соответственно с первым, вторым, третьим и четвертым выводом (s+1)-го удлинителя универсальной последовательной шины, пятый и шестой выводы последнего L-го удлинителя универсальной последовательной шины соединены соответственно с первыми выводами первой и второй сигнальных линий, седьмой и восьмой выводы последнего L-го удлинителя универсальной последовательной шины соединены соответственно с первыми выводами первой общей шины и первой шины питания, вторые выводы первой и второй сигнальных линий соединены соответственно с первым и вторым выводами восходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, второй вывод первой сигнальной линии через последовательно соединенные третью схему коррекции переходной характеристики кабеля и пятую согласованную нагрузку соединен также с третьим выводом восходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, второй вывод второй сигнальной линии через последовательно соединенные четвертую схему коррекции переходной характеристики кабеля и шестую согласованную нагрузку соединен также с четвертым выводом восходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, второй вывод первой общей шины соединен с пятым выводом второй микросхемы контроллера хаба универсальной последовательной шины, первыми выводами четвертого и пятого фильтров, предназначенных для уменьшения шума по питанию, первыми выводами второго стабилизатора напряжения и первого источника питания, шестой вывод второй микросхемы контроллера хаба универсальной последовательной шины соединен со вторыми выводами пятого фильтра, предназначенного для уменьшения шума по питанию, и второго стабилизатора напряжения, второй вывод первой шины питания соединен со вторым выводом четвертого фильтра, предназначенного для уменьшения шума по питанию, третьим выводом второго стабилизатора напряжения и вторым выводом первого источника питания, каждый j-й канал передачи данных содержит М нисходящих портов второй микросхемы контроллера хаба универсальной последовательной шины и М контроллеров М периферийных устройств, в каждом j-м канале передачи данных к каждому i-му из М нисходящих портов второй микросхемы контроллера хаба универсальной последовательной шины подключен соответствующий i-й контроллер i-го периферийного устройства, при этом первый вывод каждого i-го из М нисходящих портов второй микросхемы контроллера хаба универсальной последовательной шины соединен с первым выводом i-го контроллера соответствующего i-го периферийного устройства, второй вывод каждого i-го из М нисходящих портов второй микросхемы контроллера хаба универсальной последовательной шины соединен со вторым выводом i-го контроллера соответствующего i-го периферийного устройства, первый вывод каждого i-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединен также через соответствующую этому выводу согласованную нагрузку с третьим выводом этого же i-го порта второй микросхемы контроллера хаба универсальной последовательной шины, второй вывод каждого i-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединен также через соответствующую этому выводу согласованную нагрузку с четвертым выводом этого же i-го порта второй микросхемы контроллера хаба универсальной последовательной шины, третий вывод каждого i-го из М контроллеров М периферийных устройств соединен со вторым выводом первой общей шины, четвертый вывод каждого i-го из М контроллеров М периферийных устройств соединен со вторым выводом первой шины питания, при этом первый и второй выводы первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединены соответственно с первым и вторым выводами первого контроллера первого периферийного устройства, первый вывод первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединен также через седьмую согласованную нагрузку, соответствующую первому выводу первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины с третьим выводом первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, второй вывод первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединен также через восьмую согласованную нагрузку, соответствующую второму выводу первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, с четвертым выводом первого нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, третий и четвертый выводы первого контроллера первого периферийного устройства соединены соответственно со вторыми выводами первой общей шины и первой шины питания, первый и второй выводы М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединены соответственно с первым и вторым выводами М-го контроллера М-го периферийного устройства, первый вывод М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединен также через девятую согласованную нагрузку, соответствующую первому выводу М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины с третьим выводом М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, второй вывод М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины соединен также через десятую согласованную нагрузку, соответствующую второму выводу М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, с четвертым выводом М-го нисходящего порта второй микросхемы контроллера хаба универсальной последовательной шины, третий и четвертый выводы М-го контроллера М-го периферийного устройства соединены соответственно со вторыми выводами первой общей шины и первой шины питания, первая микросхема контроллера хаба универсальной последовательной шины содержит N нисходящих портов, которым соответствуют N каналов передачи данных, к каждому j-му из N нисходящих портов первой микросхемы контроллера хаба универсальной последовательной шины подключен соответствующий j-й канал передачи данных, первый вывод каждого j-го из N нисходящих портов первой микросхемы контроллера хаба универсальной последовательной шины соединен с первым выводом соответствующего j-го канала передачи данных, второй вывод каждого j-го из N нисходящих портов первой микросхемы контроллера хаба универсальной последовательной шины соединен со вторым выводом соответствующего j-го канала передачи данных, третий вывод каждого j-го из N нисходящих портов первой микросхемы контроллера хаба универсальной последовательной шины соединен с третьим выводом соответствующего j-го канала передачи данных, четвертый вывод каждого j-го из N нисходящих портов первой микросхемы контроллера хаба универсальной последовательной шины соединен с четвертым выводом соответствующего j-го канала передачи данных, третий вывод контроллера компьютера соединен также с пятьми выводами N каналов передачи данных, четвертый вывод контроллера компьютера соединен также с шестыми выводами N каналов передачи данных, при этом первый вывод первого нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен с первым выводом первого канала передачи данных, второй вывод первого нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен со вторым выводом первого канала передачи данных, третий вывод первого нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен с третьим выводом первого канала передачи данных, четвертый вывод первого нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен с четвертым выводом первого канала передачи данных, третий вывод контроллера компьютера соединен также с пятым выводом первого канала передачи данных, четвертый вывод контроллера компьютера соединен также с шестым выводом первого канала передачи данных, первый вывод N-го нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен с первым выводом N-го канала передачи данных, второй вывод N-го нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен со вторым выводом N-го канала передачи данных, третий вывод N-го нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен с третьим выводом N-го канала передачи данных, четвертый вывод N-го нисходящего порта первой микросхемы контроллера хаба универсальной последовательной шины соединен с четвертым выводом N-го канала передачи данных, третий вывод контроллера компьютера соединен также с пятыми выводами N-го канала передачи данных, четвертый вывод контроллера компьютера соединен также с шестым выводом N-го канала передачи данных.

Второй вариант конкретного воплощения высокоскоростного многоканального устройства для передачи данных между компьютером и периферийными устройствами, выполненного в виде универсальной последовательной шины, согласно настоящему изобретению отличается тем, что каждый из упомянутых дополнительных удлинителей универсальной последовательной шины содержит третью и четвертую сигнальные линии, вторую общую шину и вторую шину питания, первые выводы которых являются соответственно первым, вторым, третьим и четвертым выводами удлинителя универсальной последовательной шины, вторые выводы третьей и четвертой сигнальных линий соединены соответственно с первым и вторым выводами восходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины, второй вывод третьей сигнальной линии через последовательно соединенные пятую схему коррекции переходной характеристики кабеля и одиннадцатую согласованную нагрузку соединен также с третьим выводом восходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины, второй вывод четвертой сигнальной линии через последовательно соединенные шестую схему коррекции переходной характеристики кабеля и двенадцатую согласованную нагрузку соединен также с четвертым выводом восходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины, первый и второй выводы нисходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины соединены соответственно с пятым и шестым выводом удлинителя универсальной последовательной шины, первый вывод нисходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины через последовательно соединенные седьмую схему коррекции переходной характеристики кабеля и тринадцатую согласованную нагрузку соединен также с третьим выводом нисходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины, второй вывод нисходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины через последовательно соединенные восьмую схему коррекции переходной характеристики кабеля и четырнадцатую согласованную нагрузку соединен также с четвертым выводом нисходящего порта третьей микросхемы контроллера хаба универсальной последовательной шины, второй вывод второй общей шины соединен с седьмым выводом удлинителя универсальной последовательной шины, с пятым выводом третьей микросхемы контроллера хаба универсальной последовательной шины, первыми выводами шестого и седьмого фильтров, предназначенных для уменьшения шума по питанию, первыми выводами третьего стабилизатора напряжения и второго источника питания, шестой вывод третьей микросхемы контроллера хаба универсальной последовательной шины соединен со вторыми выводами седьмого фильтра, предназначенного для уменьшения шума по питанию, и третьего стабилизатора напряжения, второй вывод второй шины питания соединен с восьмым выводом удлинителя универсальной последовательной шины, со вторым выводом шестого фильтра, предназначенного для уменьшения шума по питанию, третьим выводом третьего стабилизатора напряжения и вторым выводом второго источника питания.

Настоящее изобретение поясняется чертежами и осциллограмами, приведенными на фиг.3, 4, 5 и 6.

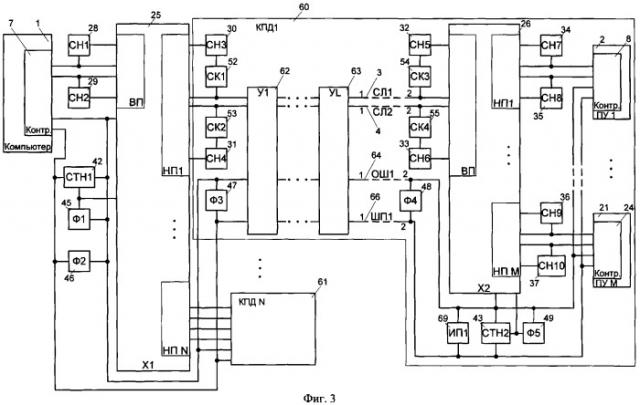

На фиг.3 приведена функциональна схема устройства, предлагаемого в изобретении, для передачи данных между персональным компьютером и периферийным устройствами, которая содержит компьютер 1, сигнальные линии (СЛ1, СЛ2) 3, 4 кабеля, микросхему контроллера 7 компьютера, микросхемы контроллеров 8, 24 периферийных устройств, микросхемы контроллеров хабов (X1, Х2) 25, 26 универсальной последовательной шины, согласованные нагрузки (СН1, ..., СН10) 28, ..., 37, стабилизаторы 42,43, напряжения (СТН1, СТН2), фильтры (Ф1, ..., Ф5) 45, ...,49, предназначенных для уменьшения шума по питанию, схемы 52, ..., 55 коррекции (СК1, ..., СК4) переходной характеристики сигнальных линий кабеля, первую общую шину (ОШ1) 64, первую шину 66 питания (ШП1), первый источник 69 питания (ИП1), а также N каналов передачи данных КПД1, ..., КПДN, из которых первый канал 60 передачи данных КПД1 (j=1) представлен в полном объеме, промежуточные j-e каналы представлены в виде точек, а последний (j=N) канал 61 передачи данных КПДN представлен в виде условного графического обозначения. Каждый канал передачи данных содержит М периферийных устройств (ПУ1, ..., ПУМ) с микросхемой контроллера в каждом периферийном устройстве, из которых первое (i=1) периферийное устройство (ПУ1) 2 с контроллером 8 и последнее (i=M) периферийное устройство (ПУМ) 21 с контроллером 24 представлены в виде условного графического обозначения, а промежуточные i-e периферийные устройства показаны в виде точек. Каждый канал передачи данных содержит L удлинителей (У1, ..., УL) универсальной последовательной шины, из которых первый удлинитель (У1) 62 универсальной последовательной шины и последний удлинитель (УL) 63 универсальной последовательной шины представлены в виде условного графического обозначения, а промежуточные s-e удлинители универсальной последовательной шины устройства показаны в виде точек. Каждая из микросхем контроллеров хабов (X1, Х2) 25, 26 универсальной последовательной шины содержит восходящий порт ВП и N нисходящих портов (НП1, ..., НПМ).

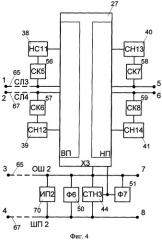

На фиг.4 представлена функциональная схема варианта исполнения удлинителей универсальной последовательной шины предлагаемого устройства, предлагаемого в изобретении, в которую входят сигнальные линии (СЛ3, СЛ4) 22, 23 кабеля, микросхема контроллера хаба (Х3) 27 универсальной последовательной шины, согласованные нагрузки (СН11, ..., CH14) 38, ..., 41, стабилизатор 44 напряжения (СТН3), фильтры (Ф6, ..., Ф7) 50, ..., 51, предназначенных для уменьшения шума по питанию, схемы 56, ..., 59 коррекции (СК5, ..., СК8) переходной характеристики сигнальных линий кабеля, вторая общая шина (ОШ2) 65, вторая шина 67 питания (ШП2), второй источник 70 питания (ИП2). Микросхема контроллера хаба (Х3) 27 универсальной последовательной шины содержит восходящий порт ВП и N нисходящих портов (НП1, ..., НПN).

При этом предлагаемое высокоскоростное многоканальное устройство, представленное на фиг.3, для передачи данных между компьютером 1 и периферийными устройствами 2 выполнено в виде универсальной последовательной шины, включает кабель с сигнальными линиями 3 и 4, шинами питания, микросхему контроллера 7 компьютера, формирующего команды, определяющие работу периферийного устройства, микросхему 8 контроллера первого устройства, управляющего направлениями потоков передаваемых данных, расположенную в первом периферийном устройстве. Устройство дополнительно содержит первую микросхему контроллера хаба 25 универсальной последовательной шины, у которой первый и второй выводы восходящего порта соединены соответственно с первым и вторым выводами микросхемы контроллера 7 компьютера, а также соединены соответственно через первую и вторую согласованные нагрузки 28, 29 с третьим и четвертым выводами восходящего порта первой микросхемы контроллера хаба 25 универсальной последовательной шины, третий вывод микросхемы контроллера 7 компьютера является общим выводом и соединен с пятым выводом первой микросхемы контроллера хаба 25 универсальной последовательной шины, первым выводом первого стабилизатора 42 напряжения, первыми выводами первого и второго фильтров 45, 46, предназначенных для уменьшения шума по питанию, шестой вывод первой микросхемы контроллера хаба 25 универсальной последовательной шины соединен со вторыми выводами первого фильтра 45, предназначенного для уменьшения шума по питанию, и первого стабилизатора 42 напряжения, четвертый вывод микросхемы контроллера 7 компьютера является выводом питания и соединен со вторым выводом второго фильтра 46, предназначенного для уменьшения шума по питанию, и третьим выводом первого стабилизатора 42 напряжения, а также N каналов передачи данных, при этом каждый j-й из которых содержит L последовательно соединенных удлинителей универсальной последовательной шины, включая первый удлинитель 62 универсальной последовательной шины, промежуточные (s=2, ..., L-1) удлинители универсальной последовательной шины и последний L-й удлинитель 63 универсальной последовательной шины, при этом первый и второй выводы первого удлинителя 62 универсальной последовательной шины являются соответственно первым и вторым выводами канала 60 передачи данных, первый вывод первого удлинителя 62 универсальной последовательной шины через первую схему 52 коррекции переходной характеристики кабеля соединен с первым выводом третьей согласованной нагрузки 30, второй вывод которой соединен с третьим выводом канала 60 передачи данных, второй вывод первого удлинителя 62 универсальной последовательной шины через вторую схему 53 коррекции переходной характеристики кабеля соединен с первым выводом четвертой согласованной нагрузки 31, второй вывод которой соединен с четвертым выводом канала 60 передачи данных, третий и четвертый выводы первого удлинителя 62 универсальной последовательной шины соединены соответственно с первым и вторым выводами третьего фильтра 47, предназначенного для уменьшения шума по питанию, и являются соответственно пятым и шестым выводами канала 60 передачи данных, при этом первый, второй, третий и четвертый выводы s-го (s=2, ..., L-1) удлинителя универсальной последовательной шины соединены соответственно с пятым, шестым, седьмым и восьмым выводами (s-1)-го удлинителя универсальной последовательной шины, а пятый, шестой, седьмой и восьмой выводы s-го удлинителя универсальной последовательной шины соединены соответственно с первым, вторым, третьим и четвертым выводом (s+1)-го удлинителя универсальной последовательной шины, пятый и шестой выводы последнего L-го удлинителя 63 универсальной последовательной шины соединены соответственно с первыми выводами первой и второй сигнальных линий 3, 4, седьмой и восьмой выводы последнего L-го удлинителя 63 универсальной последовательной шины соединены соответственно с первыми выводами первой общей шины 64 и первой шины 66 питания, вторые выводы первой и второй сигнальных линий 3, 4 соединены соответственно с первым и вторым выводами восходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, второй вывод первой сигнальной линии 3 через последовательно соединенные третью схему 54 коррекции переходной характеристики кабеля и пятую согласованную нагрузку 32 соединен также с третьим выводом восходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, второй вывод второй сигнальной линии 4 через последовательно соединенные четвертую схему 55 коррекции переходной характеристики кабеля и шестую согласованную нагрузку 33 соединен также с четвертым выводом восходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, второй вывод первой общей шины 64 соединен с пятым выводом второй микросхемы контроллера хаба 26 универсальной последовательной шины, первыми выводами четвертого и пятого фильтров 48, 49, предназначенных для уменьшения шума по питанию, первыми выводами второго стабилизатора 43 напряжения и первого источника 69 питания, шестой вывод второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен со вторыми выводами пятого фильтра 49, предназначенного для уменьшения шума по питанию, и второго стабилизатора 43 напряжения, второй вывод первой шины 66 питания соединен со вторым выводом четвертого фильтра 48, предназначенного для уменьшения шума по питанию, третьим выводом второго стабилизатора 43 напряжения и вторым выводом первого источника 69 питания, каждый j-й канал передачи данных содержит М нисходящих портов второй микросхемы контроллера хаба 26 универсальной последовательной шины и М контроллеров М периферийных устройств, в каждом j-м канале передачи данных к каждому i-му из М нисходящих портов второй микросхемы контроллера хаба 26 универсальной последовательной шины подключен соответствующий i-й контроллер i-го периферийного устройства, при этом первый вывод каждого i-го из М нисходящих портов второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен с первым выводом i-го контроллера соответствующего i-го периферийного устройства, второй вывод каждого i-го из М нисходящих портов второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен со вторым выводом i-го контроллера соответствующего i-го периферийного устройства, первый вывод каждого i-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен также через соответствующую этому выводу согласованную нагрузку с третьим выводом этого же i-го порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, второй вывод каждого i-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен также через соответствующую этому выводу согласованную нагрузку с четвертым выводом этого же i-го порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, третий вывод каждого i-го из М контроллеров М периферийных устройств соединен со вторым выводом первой общей шины 64, четвертый вывод каждого i-го из М контроллеров М периферийных устройств соединен со вторым выводом первой шины 66 питания, при этом первый и второй выводы первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединены соответственно с первым и вторым выводами первого контроллера 8 первого периферийного устройства 2, первый вывод первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен также через седьмую согласованную нагрузку 34 соответствующую первому выводу первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины с третьим выводом первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, второй вывод первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен также через восьмую согласованную нагрузку 35, соответствующую второму выводу первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, с четвертым выводом первого нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, третий и четвертый выводы первого контроллера 8 первого периферийного устройства 2 соединены соответственно со вторыми выводами первой общей шины 64 и первой шины 66 питания, первый и второй выводы М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединены соответственно с первым и вторым выводами М-го контроллера 24 М-го периферийного устройства 21, первый вывод М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен также через девятую согласованную нагрузку 36, соответствующую первому выводу М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, с третьим выводом М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, второй вывод М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины соединен также через десятую согласованную нагрузку 37, соответствующую второму выводу М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, с четвертым выводом М-го нисходящего порта второй микросхемы контроллера хаба 26 универсальной последовательной шины, третий и четвертый выводы М-го контроллера М-го периферийного устройства соединены соответственно со вторыми выводами первой общей шины 64 и первой шины 66 питания, первая микросхема контроллера хаба 25 универсальной последовательной шины содержит N нисходящих портов, которым соответствуют N каналов передачи данных, к каждому j-му из N нисходящих портов первой микросхемы контроллера хаба 25 универсальной последовательной шины подключен соответствующий j-и канал передачи данных, первый вывод каждого j-го из N нисходящих портов первой микросхемы контроллера хаба 25 универсальной последовательной шины соединен с первым выводом соответствующего j-го канала передачи данных, второй вывод каждого j-го из N нисходящих портов первой микросхемы контроллера ха