Цифровой преобразователь сигналов с неоднородной архитектурой массива выборки

Иллюстрации

Показать всеИзобретение относится к электронике для измерения характеристик высокоскоростных сигналов, которые применяются в цифровых регистраторах быстропротекающих процессов и радиолокационных приемниках. Технический результат заключается в повышении производительности. Цифровой преобразователь сигналов (ЦПС) с неоднородной архитектурой массива выборки содержит соединенные параллельно с линией входного сигнала усилители выборки и хранения (SHA), набор интеграторов, соединенных с выходами SHA, набор аналого-цифровых преобразователей (ADC), соединенных с выходами интеграторов и генератор регулируемой задержки, выполненный с возможностью обеспечения функционирования каждого SHA, интегратора и ADC в соответствующие временные интервалы. Для повышения производительности в ЦПС генератор регулируемой задержки, содержит блок определения числа циклов, выполненный с возможностью определения числа циклов интегрирования в каждой точке временной шкалы входного сигнала в зависимости от положения обрабатываемой точки сигнала на временной шкале. 4 ил.

Реферат

Изобретение относится к области электроники, а именно к цифровым преобразователям сигналов с неоднородной архитектурой массива выборки, используемым для измерения характеристик высокоскоростных сигналов, которые применяются в цифровых регистраторах быстропротекающих процессов и радиолокационных приемниках.

Для регистрации высокоскоростного сигнала широко используют цифровые преобразователи на основе усилителей выборки и запоминания (SHA - sample-and-hold amplifier), интегратора выходного сигнала SHA, прграммируемого генератора задержанных импульсов, преобразователя из аналоговой формы в цифровую (ADC - analog-to-digital converter) и интерфейса передачи данных в компьютер или микроконтроллер. В данной архитектуре интегратор выходного сигнала SHA нужен для повышения отношения "сигнал/шум". Для повышения этого отношения необходимо периодически повторять входной сигнал и интегрировать выходной сигнал SHA, что уменьшает пропускную способность системы пропорционально числу повторяющихся циклов.

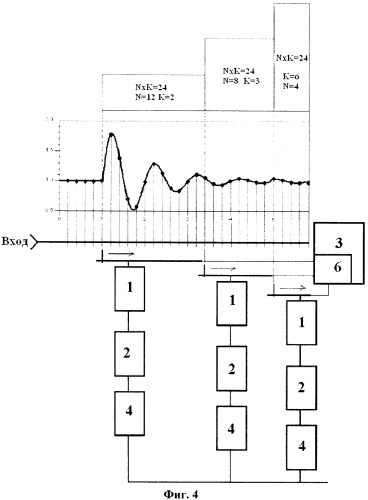

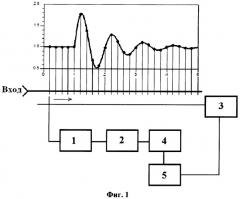

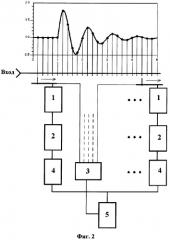

В настоящее время широко используют цифровые преобразователи (Фиг.1-3) на основе усилителя 1 выборки и хранения - SHA, которые, кроме того, содержат интегратор 2 выходного сигнала SHA, программируемый генератор 3 задержки, преобразователь 4 из аналоговой формы в цифровую - ADC и интерфейс персонального компьютера.

Известен цифровой преобразователь сигналов (см. Мелешко Е.А. Наносекундная электроника в экспериментальной физике. - М.: Энергоатомиздат, 1987, стр.174[1]), в котором используют один SHA, интегратор и генератор задержки, действующий на всей протяженности сигнала (Фиг.1). Для функционирования данного устройства важно, чтобы фиксированный сигнал повторяли N раз, где N число выборок (тактов)сигнала.

Также известна другая конструкция цифрового преобразователя (см. Мелешко Е.А. Наносекундная электроника в экспериментальной физике. - М.: Энергоатомиздат, 1987, стр.174 [2]) с несколькими (К) SHA и генераторами задержки, действующими в отдельные интервалы времени. Для функционирования данного преобразователя важно, чтобы входной сигнал повторяли N/K раз, где N - число образцов сигнала, и К -число SHA (Фиг.2). Такая конструкция обеспечивает повышение производительности в К раз по сравнению с [1]. В данной конструкции число циклов интегрирования фиксировано для всех точек временной шкалы, что является избыточным.

Наиболее близким к заявленному изобретению является цифровой преобразователь, описанный в патенте США №5,519,342 [3]), в котором число SHA и интеграторов соответствует числу точек оцифровки. Данный преобразователь выбран в качестве прототипа заявленного изобретения. Он выполнен с возможностью регистрации формы даже однократного импульса. К недостатку прототипа можно отнести то, что в случае большого числа точек оцифровки в нем требуется наличие для каждой точки отдельного SHA и генератора, поэтому данное решение (Фиг.3) требует очень больших затрат при изготовлении.

Во всех описанных выше аналогах и прототипе заявленного изобретения интегратор выходного сигнала SHA предназначен для увеличения отношения "сигнал/шум". Для повышения этого отношения в них необходимо периодически и многократно повторять входной сигнал, что влечет уменьшение производительности системы.

Задачей заявленного изобретения является создание цифрового преобразователя сигналов с неоднородной архитектурой массива выборки, который имел бы повышенную производительность и меньшую стоимость.

В общем случае, число выборок и интегрирований в заявленном цифровом преобразователе меняется на протяжении временного интервала по определенному правилу, например, по квадратичному закону для компенсации уменьшения сигнала в результате сферической расходимости, по экспоненциальному закону для сигналов, распространяющихся в средах с поглощением, и так далее.

Поставленная задача решена путем создания цифрового преобразователя сигналов с неоднородной архитектурой массива выборки, который содержит соединенные параллельно с линией входного сигнала усилители выборки и хранения, набор интеграторов, соединенных с выходами усилителей выборки и хранения, набор аналого-цифровых преобразователей, соединенных с выходами интеграторов, и генератор регулируемой задержки, выполненный с возможностью обеспечения функционирования каждого SHA, интегратора и ADC в соответствующие временные интервалы, в котором генератор регулируемой задержки содержит блок определения числа циклов, выполненный с возможностью определения числа циклов интегрирования в каждой точке временной шкалы входного сигнала в зависимости от положения обрабатываемой точки сигнала на временной шкале.

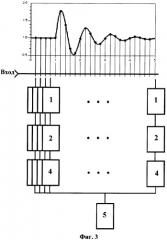

Другими словами, задача решена за счет создания в генераторе регулируемой задержки блока определения числа циклов, выполненного с возможностью более эффективного интегрирования выходного сигнала SHA на основе различия уровня "сигнал/шум" в интервалах полной временной шкалы сигнала. Сигналы, принятые в течение начального временного интервала, т.е. сравнительно малого времени, соответствуют малым дальностям, т.е. расстояниям до цели, и, соответственно, высокому уровню сигнала, следовательно, в начальном временном интервале нет необходимости в большом числе циклов интегрирования. Поэтому SHA, действующий в данном временном интервале, может обработать больше точек в течение того же числа выполняемых циклов, чем SHA, действующий во временных интервалах, соответствующих большим дальностям (Фиг.4). Таким образом, в блоке определения числа циклов заявленного цифрового преобразователя для получения требуемого отношения сигнал-шум обеспечивают требуемое число циклов интегрирования только для конца временной шкалы, для других временных интервалов число циклов уменьшают с увеличением обработанного временного интервала.

Техническим результатом заявленного изобретения является повышение производительности и уменьшение стоимости цифрового преобразователя.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими чертежами.

Фиг.1 - Схема и временная диаграмма работы цифрового преобразователя аналога [1] заявленного изобретения в режиме стробоскопа, в котором SHA последовательно осуществляет выборку величины сигнала от одной точки временной шкалы к другой, изменение временной позиции осуществляют генератором задержки, а полный цикл цифрового преобразования сигнала содержит N периодов входного сигнала.

Фиг.2 - Схема и временная диаграмма работы цифрового преобразователя аналога [2] заявленного изобретения с использованием нескольких SHA и генераторов задержки, действующих в отдельные временные интервалы.

Фиг.3 - Схема и временная диаграмма работы цифрового преобразователя прототипа [3] заявленного изобретения с большим числом SHA и интеграторов, соответствующем числу точек на временной шкале.

Фиг.4 - Схема и временная диаграмма работы цифрового преобразователя, выполненного согласно изобретению.

Как показано на Фиг.3, отношение "сигнал/шум" различается в разных временных интервалах, например, в радиолокационной системе сигналы, как правило, тем слабее, чем позже они поступили, и наоборот.

Заявленный цифровой преобразователь содержит набор 1 SHA, набор 2 интеграторов, генератор 3 регулируемой задержки, ADC 4 и блок 6 определения числа циклов, встроенный в генератор 3 регулируемой задержки. Причем набор 1 SHA (Фиг.4), соединен с линией входного сигнала, интеграторы 2, соединены с выходами набора 1 SHA, ADC 4 соединены с выходами интеграторов, генератор 3 регулируемой задержки, обеспечивает функционирование каждого SHA, интегратора и ADC в соответствующий временной интервал. Блок 6 определения числа циклов выполнен с возможностью определения числа циклов интегрирования в каждой точке временной шкалы входного сигнала в зависимости от положения обрабатываемой точки сигнала на временной шкале.

Таким образом, для увеличения отношения "сигнал/шум" используют интегрирование выходного сигнала SHA в течение нескольких циклов входного сигнала, при этом все SHA и интеграторы функционируют в каждом цикле входного сигнала, но в пределах временного интервала, соответствующего худшему отношению "сигнал/шум ", причем несколько циклов входного сигнала должны быть повторены в каждой точке временной шкалы, и выходной сигнал SHA должен быть интегрирован для увеличения отношения "сигнал/шум". Например, на Фиг.4 в последнем временном интервале шесть циклов входного сигнала должны быть интегрированы для получения требуемого отношения "сигнал / шум". Данный временной интервал содержит четыре временные точки, поэтому общее число циклов входного сигнала 6×4=24. В то же время предыдущий временной интервал, имеющий лучшее отношение "сигнал/шум", требует меньшего числа циклов интегрирования входного сигнала. Как показано на Фиг.4, это число равно трем, и в течении двадцати четырех циклов входного сигнала соответствующий SHA может обработать восемь точек временной шкалы. Первый временной интервал имеет еще более высокое отношение "сигнал/шум", он требует меньшего числа циклов интегрирования входного сигнала. Как показано на Фиг.4 это число равно двум, и в течении двадцати четырех циклов входного сигнала соответствующий SHA должен обработать двенадцать точек временной шкалы. В этом случае общее число циклов входного сигнала равно двадцати четырем, и общее число точек временной шкалы также равно двадцати четырем. В случае, если интегрирование шести циклов входного сигнала будет применено ко всем точкам временной шкалы, общее требуемое число циклов входного сигнала будет равно сорока восьми. Таким образом, мы имеем двукратное преимущество по сравнению со схемой, использующей постоянное число циклов интегрирования. В случае радарного сканера это означает двукратное увеличение производительности сканера.

Заявленный цифровой преобразователь сигналов с неоднородной архитектурой массива выборки может применяться для дискретизации и обработки быстрых электрических сигналов в частности в UWB радиолокационных системах, радарных сканерах, системах локального позиционирования.

Хотя указанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

Цифровой преобразователь сигналов с неоднородной архитектурой массива выборки, содержащий соединенные параллельно с линией входного сигнала усилители выборки и хранения, набор интеграторов, соединенных с выходами усилителей выборки и хранения, набор аналого-цифровых преобразователей, соединенных с выходами интеграторов и генератор регулируемой задержки, выполненный с возможностью обеспечения функционирования каждого SHA, интегратора и ADC в соответствующие временные интервалы, отличающийся тем, что генератор регулируемой задержки содержит блок определения числа циклов, выполненный с возможностью определения числа циклов интегрирования в каждой точке временной шкалы входного сигнала в зависимости от положения обрабатываемой точки сигнала на временной шкале.