Способ проверки многоотсчетных преобразователей временных интервалов в код

Иллюстрации

Показать всеИзобретение относится к области автоматики и вычислительной техники и может быть использовано для проверки многоотсчетных преобразователей аналоговой величины в код. Достигаемый технический результат - повышение достоверности проверки многоотсчетных преобразователей временных интервалов в код.

Способ характеризуется тем, что формируют периодически повторяющиеся совокупности взаимосвязанных временных интервалов в виде нескольких частично перекрывающихся отсчетов, формируют контрольные значения для каждой из совокупностей временных интервалов, формируют юстировочные константы в виде совокупности единичных и нулевых сигналов, определяют границы формируемых временных интервалов, проверяют сформированные юстировочные константы на соответствие заданным, изменяют заданные юстировочные константы в допустимых пределах рассогласования отсчетов, изменяют контрольные значения временных интервалов в соответствии с изменениями заданных юстировочных констант, определяют отсутствие ошибок рассогласования между измененными контрольными и выходными значениями временных интервалов. 2 ил.

Реферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для проверки многоотсчетных преобразователей аналоговой величины в код.

Известен способ проверки преобразователей временных интервалов в код, в котором задают углы поворота вала фазовращателя, формируют на выходах фазовращателей периодически повторяющуюся последовательность временных интервалов, преобразуют временные интервалы в код и определяют погрешность путем сравнения кода с контрольными значениями при изменении временных интервалов [1].

Недостатком известного способа является сложность его реализации, связанная с необходимостью использования высокоточного фазовращателя, а также невозможность проверки многоотсчетных преобразователей временных интервалов в код.

Наиболее близким техническим решением к данному изобретению является способ проверки многоотсчетных преобразователей временных интервалов в код, реализованный в преобразователе угла поворота вала в код [2]. В известном способе формируют (с помощью фазовращателей и блоков формирователей импульсов) периодически повторяющуюся совокупность взаимосвязанных временных интервалов в виде нескольких частично перекрывающихся отсчетов с соответствующими масштабными коэффициентами P1, P2, Р3 (коэффициенты электрической редукции фазовращателей), формируют контрольные значения для каждой из совокупностей временных интервалов в виде показаний углозадающего устройства вала фазовращателей, формируют в технологическом режиме юстировочные константы (ЮК) в виде разности между равноценными частями (согласующими разрядами) временных интервалов соседних отсчетов и отклонения единого значения временных интервалов всех отсчетов от заданного значения в исходном положении, запоминают ЮК, определяют погрешности в штатном режиме сравнением единых выходных значений временных интервалов с контрольными значениями при синхронном изменении задаваемых временных интервалов (при вращении вала фазовращателей) пропорционально их масштабным коэффициентам.

Единые выходные значения совокупности временных интервалов проверяемого преобразователя формируют с помощью запомненных ЮК. Блок памяти не входит в состав проверяемого преобразователя и запись в него ЮК при эксплуатации производится после установки преобразователя на объект и измерения фактических ЮК, значения которых могут получиться любыми.

Недостатком известного способа является неполнота проверок электрических цепей связи преобразователя с блоком памяти ЮК, отсутствие проверки работы преобразователя в допустимых пределах рассогласования отсчетов, а также необходимость высокоточного углозадающего устройства для формирования контрольных значений.

В предложенном способе задают ЮК в виде совокупности единичных и нулевых сигналов, исходя из полноты проверки целостности электрических цепей связи блока памяти ЮК, определяют границы формирования временных интервалов, исходя из заданных ЮК, формируют периодически повторяющуюся совокупность взаимосвязанных временных интервалов в виде нескольких частично перекрывающихся отсчетов с соответствующими масштабными коэффициентами, формируют контрольные значения для каждой из совокупностей временных интервалов, формируют в технологическом режиме ЮК и проверяют их на соответствие заданным, определяют в штатном режиме погрешности преобразователя сравнением единых выходных значений временных интервалов с контрольными значениями при синхронном изменении формируемых временных интервалов пропорционально их масштабным коэффициентам при заданных ЮК, изменяют заданные ЮК в допустимых пределах рассогласования отсчетов, изменяют контрольные значения временных интервалов в соответствии с изменениями заданных ЮК и определяют в штатном режиме отсутствие погрешности рассогласования между выходными и измененными контрольными значениями временных интервалов.

Технический эффект предложенного способа заключается в повышении достоверности проверки многоотсчетных преобразователей временных интервалов в код.

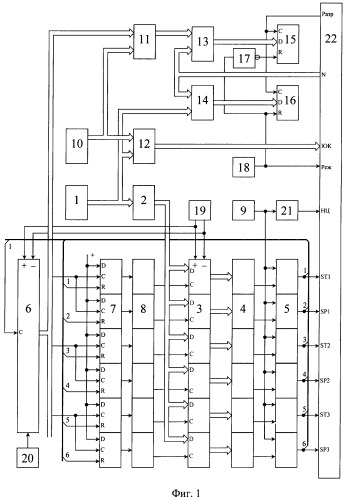

Структурные схемы двух возможных устройств для осуществления способа вместе с проверяемым преобразователем представлены на фиг.1 и фиг.2.

Устройство на фиг.1 содержит блок 1 задания ЮК, вычислительный блок 2 с памятью, блок 3 реверсивных счетчиков PC, блок 4 цифроаналоговых преобразователей ЦАП, блок 5 компараторов, реверсивный счетчик 6 импульсов, блок 7 триггеров, блок 8 одновибраторов, генератор 9 пилообразного напряжения (ГПН), блок 10 задания смещений, цифровые сумматоры 11, 12, 13, и 14, регистраторы 15 и 16, инвертор 17, переключатели 18, 19 и 20, делитель 21 частоты, проверяемый преобразователь 22. Блоки 1 и 10 представляют собой группу ключей, коммутирующих шины единичных и нулевых потенциалов (шины питания) к выходам этих блоков. Период сигналов ГПН 9 равен периоду старт (ST) и стоп (SP) импульсов проверяемого преобразователя 22. Число разрядов каждого PC блока 3 и каждого ЦАП блока 4 равно числу разрядов при измерении каждого из временных интервалов преобразователя 22. Число элементов в блоках 3 ... 5, 7, 8, а также число групп выходов блока 2 равно удвоенному количеству отсчетов проверяемого преобразователя 22. Группы выходов блока 2 подключены к входам данных соответствующих PC блока 3, счетные входы которых соединены с выходами соответствующих одновибраторов блока 8, а управляющие входы соединены с выходами переключателя 19. Выходы каждого PC блока 3 через соответствующий ЦАП блока 4 подключены к одним входам компараторов блока 5, другие входы компараторов блока 5 объединены и соединены с выходом ГПН 9 и через делитель 21 частоты с входом начала цикла (НЦ) проверяемого преобразователя 22. Выходы компараторов блока 5 подключены к входам ST и SP (начало и конец временных интервалов) проверяемого преобразователя 22 и к входам сброса R соответствующих триггеров блока 7. Информационные D-входы триггеров блока 7 соединены с шиной единичного потенциала, а синхровходы С - с соответствующими выходами реверсивного счетчика 6. Счетный вход реверсивного счетчика 6 соединен с выходом одного из компараторов блока 5, управляющие входы - с выходами переключателя 19, а вход сброса - с выходом переключателя 20. Выход переключателя 18 подключен к входу выбора режима проверяемого преобразователя 22, входу сброса регистратора 16 и через инвертор 17 - входу сброса регистратора 15. Выходы сумматора 12 подключены к входам ЮК проверяемого преобразователя 22, информационные выходы которого подключены к одной группе входов цифровых сумматоров 13 и 14, а выход разрешения проверяемого преобразователя 22 подключен к синхровходам регистраторов 15 и 16, информационные входы которых соединены с выходами соответствующих цифровых сумматоров 13 и 14.

Выходы блока 1 подключены к входам блока 2, к одной группе входов сумматора 12 и к другой группе входов сумматора 14. Выходы блока 6 подключены к одной группе входов сумматора 11, другая группа входов которого соединена с выходами блока 10 и другой группой входов сумматора 12, а выходы сумматора 11 подключены к другой группе входов сумматора 13.

ГПН 9 работает в непрерывном режиме, формируя временную развертку в виде пилообразного напряжения с периодом Т, равным периоду ST и SP импульсов на входах проверяемого преобразователя 22. При совпадении напряжения ГПН 9 с выходными напряжениями ЦАП блока 4 в компараторах блока 5 формируются импульсы, временное положение которых относительно начала развертки ГПН 9 изменяется в зависимости от выходного напряжения ЦАП блока 4. Выходные импульсы компараторов блока 5 в качестве ST и SP импульсов поступают на входы преобразователя 22. Каждая пара компараторов блока 5 вырабатывает ST и SP импульсы для одного из отсчетов преобразователя 22.

ЮК задают в блоке 1, исходя из полноты проверки преобразователя 22, например, в виде 1 и 0. По заданным ЮК в вычислительном блоке 2 определяют начальные граничные значения формируемых временных интервалов для всех отсчетов, запоминают их и далее передают на входы данных PC блока 3.

При проверке преобразователя 22 в технологическом режиме его работы переключатель 20 удерживает реверсивный счетчик 6 в нулевом состоянии, поэтому информационные сигналы на выходах триггеров блока 7 и одновибраторов блока 8 отсутствуют. Выходные коды реверсивных счетчиков блока 3 соответствуют выходным кодам вычислительного блока 2. ЦАП блока 4 формируют уровни напряжения, соответствующие выходным кодам PC блока 3, а компараторы блока 5 формируют периодически повторяющуюся совокупность взаимосвязанных временных интервалов в виде нескольких частично перекрывающихся отсчетов. На выходах N преобразователя 22 формируется код, соответствующий заданным ЮК. Этот код в сумматоре 14 сравнивается с заданными ЮК, а результат сравнения фиксируется в регистраторе 16 по сигналу разрешения РАЗР, который формируется на выходе преобразователя 22 одновременно с кодом на выходах N.

При проверке начального кода преобразователя 22 в штатном режиме его работы выходные ST и SP импульсы формируются аналогично технологическому режиму. При нулевом коде на выходах блока 10 из блока 1 через сумматор 12 на входы преобразователя 22 поступает код ЮК. На выходах N преобразователя 22 формируется единый код совокупности входных временных интервалов, который в сумматоре 13 сравнивается с выходным кодом реверсивного счетчика 6. Результат сравнения записывается в регистратор 15 по сигналу РАЗР. При проверке начального кода реверсивный счетчик 6 переключателем 20 установлен в нулевое состояние. На входы сумматора 13 поступают нулевые коды. Результат сравнения из сумматора 13 записывается в регистратор 15 по сигналу РАЗР с выхода преобразователя 22. Регистраторы 15 и 16 могут фиксировать результат каждого измерения с последующей оценкой оператором результатов проверки или фиксировать только отклонения от заданных уставок (см., например, С.С.Хризман. Цифровые измерительные приборы и системы, Справочник, «Наукова думка», Киев, 1970, с.62-63).

Режим работы проверяемого преобразователя 22 задается переключателем 18. В штатном режиме работы регистратор 16 закрыт, регистратор 15 открыт, а в технологическом режиме наоборот. Начало цикла НЦ работы проверяемого преобразователя 22 синхронизировано с началом временной развертки ГПН 9 с помощью делителя 21 частоты.

Для синхронного изменения формируемых на входах преобразователя 22 временных интервалов пропорционально их масштабным коэффициентам переключателем 20 снимают сигнал сброса с реверсивного счетчика 6, который начинает подсчитывать выходные ST (или SP) импульсы компаратора блока 5 отсчета с наибольшим значением Р. Реверсивный счетчик 6 работает в режиме делителя частоты. Выходы реверсивного счетчика 6, разрядность которых пропорциональна масштабным коэффициентам изменения формируемых блоком 5 временных интервалов, подключены к С-входам пары триггеров блока 7 соответствующих отсчетов. Выход более младшего разряда подключен к триггерам отсчета, соответствующего наибольшему Р. Выходные импульсы реверсивного счетчика 6 устанавливают триггеры блока 7 в 1. Сброс в 0 этих триггеров производится ST и SP импульсами соответствующих компараторов блока 5.

По срезам сигналов триггеров блока 7 соответствующие одновибраторы блока 8 вырабатывают импульсы, по срезам которых PC блока 3 изменяют свой код на 1. При этом PC в цепях формирования ST импульсов увеличивают (уменьшают) свой код, а в цепях формирования SP импульсов уменьшают (увеличивают) код. Направлением изменения кода в PC блока 3 управляют переключателем 19. В результате временные интервалы между ST и SP импульсами всех отсчетов одновременно увеличиваются или уменьшаются пропорционально их масштабным коэффициентам. При этом пропорционально и синхронно изменяются выходные коды преобразователя 22 и реверсивного счетчика 6, которые сравниваются в сумматоре 13. Результаты сравнения последовательно фиксируются в регистраторе 15.

Одновибраторы блока 8 выполняют функцию элементов задержки для исключения двойного срабатывания компараторов блока 5 при формировании ST и SP импульсов. Для исключения сбоев при возможном совпадении импульсов на входах триггеров блока 7 входные импульсы реверсивного счетчика 6 и импульсы на входах R триггеров блока 7 синхронизированы разными тактами высокочастотного генератора (на фиг.1 не представлены).

Для проверки работы преобразователя 22 при возможных рассогласованиях между отсчетами формируют в блоке 10 с помощью ключей единичные и нулевые сигналы для изменения ЮК в допустимых пределах. Выходной код блока 10 в сумматоре 12 суммируют с кодом ЮК с выходов блока 1, а в сумматоре 11 - с контрольным кодом с выходов реверсивного счетчика 6. Выходной код сумматора 12 поступает на входы ЮК преобразователя 22. Если изменения ЮК находятся в допустимых пределах рассогласования между отсчетами, то при отсутствии неисправностей в проверяемом преобразователе 22 на выходах цифрового сумматора 13 и в регистраторе 15 будут зафиксированы значения, близкие к нулевым.

По окончании проверки преобразователя 22 при первоначально заданных ЮК во всем диапазоне временных интервалов и изменениях ЮК в допустимых пределах устанавливают новые значения ЮК, инверсные первым, и проводят аналогичные проверки преобразователя 22 с новыми значениями ЮК. В результате достигается полнота проверок целостности электрических цепей и функционирования преобразователя 22 во всех режимах его работы.

Определение в вычислительном блоке 2 границ временных интервалов, которые записывают в процессе проверки преобразователя 22 в PC блока 3, можно производить в последовательности, обратной процессу формирования выходного кода N преобразователя 22 в штатном режиме его работы.

Выходной код N преобразователя 22 в исходном положении должен быть нулевым. Для приведения измеренного кода в исходное положение используют юстировочную константу С0. При проверке преобразователя 22 константу С0 задают, исходя из полноты проверки электрических цепей связи с блоком памяти ЮК. Тогда полный многоотсчетный код преобразователя 22 перед его приведением является дополнительным кодом С0 и составляет NП=0-С0.

Код NП можно представить в виде двух отсчетов: согласованного кода NГ старших значащих разрядов грубого отсчета ГО и кода NТ точного отсчета ТО, состоящего из кода NС старших согласующих разрядов ГО, смещенного на юстировочную константу C1 и кода NM в младших несмещенных разрядах ТО, т.е. NT=(NС-C1)+NМ

Если в преобразователе 22 данный ТО представлен кодом NT с числом разрядов n=log2(Т/ТГИ) (где ТГИ период следования импульсов ГИ заполнения временных интервалов в преобразователе 22, Т - период следования ST или SP импульсов) и однозначно определяет величину временных интервалов в диапазоне 0...Т/2, то код NST, записываемый в PC блока 3 для формирования ST импульса младшего отсчета (с наибольшим Р) преобразователя 22 может быть произвольным. Код NSP для формирования SP импульса этого отсчета определяется из соотношения NSP=NST-NT.

Если NT имеет число разрядов n+1 и определяет величину временного интервала в диапазоне 0...Т, то NT состоит из двух отсчетов. Старшие n разрядов кода NT представляют собой код NПГ промежуточного ГО с одним старшим значащим разрядом, определяющим номер полупериода (0...Т/2 или Т/2...Т), и остальными согласующими, в старших из которых записан код NПС согласующих разрядов промежуточного ГО. Младшие n разрядов кода NT являются кодом NПТ промежуточного ТО (для диапазона 0...Т/2), смещенным на юстировочную константу С2 относительно кода NПС, т.е. NПТ=(NПС - С2)+NМ. В этом случае коды NST и NSP, записываемые в PC блока 3 для формирования ST и SP импульсов младшего отсчета преобразователя 22, определяются из соотношений:

NST=[NT/2]

NSP=NST-NПТ, где [...]- целая часть числа.

Для определения кодов NST и NSP соседнего старшего (j-1) отсчета необходимо вычислить полный код NП(j-1) этого отсчета, исключив младший j отсчет

NП(j-1)=[(Pj-1/Pj)×NПj],

где [...]- целая часть числа;

Pj, Pj-1 - коэффициенты редукции соответствующих отсчетов;

NП(j-i), NПj - полные коды (j-1) и j отсчетов.

После этого с кодом NП(j-1) проделывают все описанные выше операции по нахождению NST и NSP. Так последовательно можно определить коды NST и NSP исходного положения для всех отсчетов.

После проверки преобразователя 22 с первым набором ЮК (например, чередующиеся 1 и 0 с 1 в старшем разряде) изменяют ЮК на инверсные, определяют новые значения исходных NST и NSP для всех отсчетов и повторяют частично или полностью весь цикл проверок.

Память в блоке 2 нужна для исключения повторного определения значений NST и NSP всех отсчетов при сохранении исходных значений ЮК в блоке 1 для одного и того же типа проверяемых преобразователей 22.

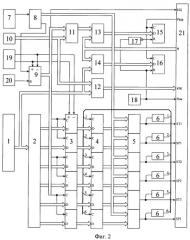

Устройство на фиг.2 содержит блок 1 задания ЮК, вычислительный блок 2 с памятью, блок 3 реверсивных счетчиков, блок 4 регистров, блок 5 цифровых компараторов (ЦК), блок 6 элементов задержки (одновибраторов), генератор 7 импульсов, счетчик 8, реверсивный счетчик 9, блок 10 задания смещений, цифровые сумматоры 11, 12, 13 и 14, регистраторы 15 и 16, инвертор 17, переключатели 18, 19 и 20, проверяемый преобразователь 21. Блоки 1 и 10 представляют собой группу ключей, коммутирующих единичные и нулевые шины к выходам этих блоков.

Устройство работает следующим образом. Генератор 7 формирует импульсы с частотой, равной частоте заполнения временных интервалов в преобразователе 21. Период счетчика 8 равен периоду ST и SP импульсов в преобразователе 21 в статическом состоянии. Блоки 1 и 2 работают так же, как одноименные блоки устройства на фиг.1. В зависимости от заданных в блоке 1 юстировочных констант в блоке 2 определяются границы временных интервалов для всех отсчетов P1, Р2, Р3 и заносятся на входы данных PC блока 3, выходные коды которых фиксируются в регистрах блока 4 и сравниваются в цифровых компараторах блока 5 с периодически изменяющимся кодом счетчика 8. При сравнении в компараторах блока 5 формируются ST и SP импульсы, поступающие в преобразователь 21 и по цепям обратной связи через элементы 6 задержки на С-входы соответствующих регистров блока 4 для записи выходных кодов PC блока 3.

При проверке работы преобразователя 21 в технологическом режиме, который задают переключателем 18, на выходной шине N данных преобразователя 21 вырабатывается код всех ЮК, соответствующих временным интервалам между ST и SP импульсами с выходов компараторов блока 5. В цифровом сумматоре 14 сравнивается ЮК, заданные блоком 1 и выработанные преобразователем 21. Результат сравнения фиксируется регистратором 16.

При проверке преобразователя 21 в штатном режиме на его входы поступают заданные ЮК с выходов блока 1 через сумматор 12. С помощью этих ЮК преобразователь 21 формирует на выходной шине данных полный код, соответствующий совокупности временных интервалов между ST и SP импульсами компараторов блока 5. Этот код сравнивается в цифровом сумматоре 13 с выходным кодом реверсивного счетчика 9, поступающим через сумматор 11. Результат сравнения фиксируется регистратором 15.

Пропорциональное изменение временных интервалов всех отсчетов при проверке работы преобразователя 21 во всем диапазоне его работы осуществляется с помощью реверсивного счетчика 9 и реверсивных счетчиков блока 3 при снятии сигнала сброса переключателем 20. На С-входы каждой пары PC блока 3 поступают с выходов реверсивного счетчика 9 импульсы с частотами, пропорциональными коэффициентам электрической редукции между отсчетами P1, Р2, Р3. Один из каждой пары PC блока 3 работает на увеличение кода, а другой - на уменьшение. Направление изменения временных интервалов между ST и SP импульсами определяется направлением счета PC блока 3 и реверсивного счетчика 9 с помощью переключателя 19. Скорость изменения временных интервалов (время проверки преобразователя 21 во всем диапазоне его работы) можно регулировать добавлением младших разрядов в реверсивный счетчик 9 (уменьшение скорости) или подключением выхода младшего разряда реверсивного счетчика 9 к входам более старших разрядов первой пары PC блока 3 (увеличение скорости). Элемент задержки блока 6 необходим для исключения сбоев компараторов блока 5 при формирования ST и SP импульсов, особенно при больших скоростях изменения временных интервалов.

Проверка работы преобразователя 21 устройством на фиг.2 при рассогласовании между отсчетами с коэффициентами электрической редукции P1, Р2, Р3 проводится аналогично такой же проверке устройством на фиг.1. В блоке 10 с помощью ключей задается величина рассогласования, в соответствии с которой в цифровом сумматоре 11 изменяется контрольный код с выходов реверсивного счетчика 9. Выходные коды цифрового сумматора 11 и преобразователя 21 сравниваются в цифровом сумматоре 13. Результаты сравнения фиксируются регистратором 15.

Проверку работы преобразователя 21 устройством на фиг.2 проводят с прямыми и инверсными выходными сигналами блока 1.

Таким образом, в предложенном способе проверки многоотсчетных преобразователей временных интервалов в код задают в блоке 1 юстировочные константы в виде совокупности единичных и нулевых сигналов, исходя из полноты проверки целостности электрических цепей связи с блоком памяти ЮК, определяют в вычислительном блоке 2 границы формируемых временных интервалов, исходя из заданных ЮК, формируют в блоке 5 периодически повторяющуюся совокупность взаимосвязанных временных интервалов в виде нескольких частично перекрывающихся отсчетов с соответствующими масштабными коэффициентами, проверяют с помощью блоков 14 и 16 сформированные проверяемым преобразователем 22 (21) юстировочные константы на соответствие заданным в блоке 1, формируют в реверсивном счетчике 6 (9) контрольные значения совокупности временных интервалов, определяют с помощью блоков 13 и 15 погрешности сравнением единых выходных значений временных интервалов преобразователя 22 (21) с контрольными значениями при синхронном изменении (с помощью блоков 3, 4, 5) временных интервалов пропорционально их масштабным коэффициентам, изменяют с помощью блоков 10 и 12 заданные юстировочные константы в допустимых пределах рассогласования отсчетов, изменяют с помощью сумматора 11 контрольные значения временных интервалов и определяют с помощью блоков 11, 13 и 15 отсутствие погрешности рассогласования между контрольными (с выходов сумматора 11) и выходными с проверяемого преобразователя 22 (21) значениями временных интервалов.

В результате обеспечивается полнота проверки многоотсчетного преобразователя временных интервалов в код, т.е. повышается достоверность проверок.

Источники информации

1. Авторское свидетельство СССР № 1275765, кл. H03M 1/10, 1985.

2. Патент РФ № 1807560, кл. H03M 1/64, 1991.

Способ проверки многоотсчетных преобразователей временных интервалов в код, основанный на формировании периодически повторяющейся совокупности взаимосвязанных временных интервалов в виде нескольких частично перекрывающихся отсчетов с соответствующими масштабными коэффициентами, формировании контрольных значений для каждой из совокупностей временных интервалов, формировании юстировочных констант, определении погрешности сравнением единых выходных значений временных интервалов с контрольными значениями при синхронном изменении формируемых временных интервалов пропорционально их масштабным коэффициентам, отличающийся тем, что задают юстировочные константы в виде совокупности единичных и нулевых сигналов, исходя из полноты проверки целостности электрических цепей связи с блоком памяти юстировочных констант, определяют границы формируемых временных интервалов, исходя из заданных юстировочных констант, проверяют сформированные юстировочные константы на соответствие заданным, изменяют заданные юстировочные константы в допустимых пределах рассогласования отсчетов, изменяют контрольные значения временных интервалов в соответствии с изменениями заданных юстировочных констант, определяют отсутствие ошибок рассогласования между измененными контрольными и выходными значениями временных интервалов.