Анализатор числа

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

235394

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹

Кл. 42m, 7/38

42m, 7 44

Заявлено 14.!Х.1967 (¹ 1183955/18-24) с присоединением заявки №

ЧПК 6 06f

G 061

УДК 681.325.6 (088.8) Приоритет

Опубликовано 16.1.1969. Бюллетень ¹ 5

Дата опубликования описания 9Л I.1969

Комитет по делам изобретений и открытий лри Совете Минивтров

СССР

Авторы изобретения

H. H. Трофимов и В. И. Кариснко

Артиллерийская радиотехническая академия Советской Армии им. Л. А. Говорова

Заявитель

АНАЛИЗАТОР ЧИСЛА

Предложенный анализатор относится к области цифровой вычислительной техники и может быть применен в множительном устройстве, в преобразователях числа в модифицированный код и в определителях арифметического веса числа.

Известны анализаторы числа, содержащие входной дешифратор, блок выработки сигнала окончания очередного такта, схему с четырьмя устойчивыми состояниями, дешифратор состояний и матрицу управляющих сигналов.

Предлагаемый анализатор отличается тем, что в нем единичный выход входного дешифратора, анализирующего два соседних разряда числа, соединен с первым входом схемы с четырьмя устойчивыми состояниями, нулевой выход входного дешифратора, анализирующего два соседних разряда числа, подсоединен ко второму входу схемы с четырьмя устойчивыми состояниями, выход блока выработки окончания очередного такта подключен к третьему входу схемы с четырьмя устойчивыми состояниями, выход которой подсоединен через дешифратор состояний ко входам матрицы управляющих сигналов.

Это позволяет повысить быстродействие анализатора и упростить его.

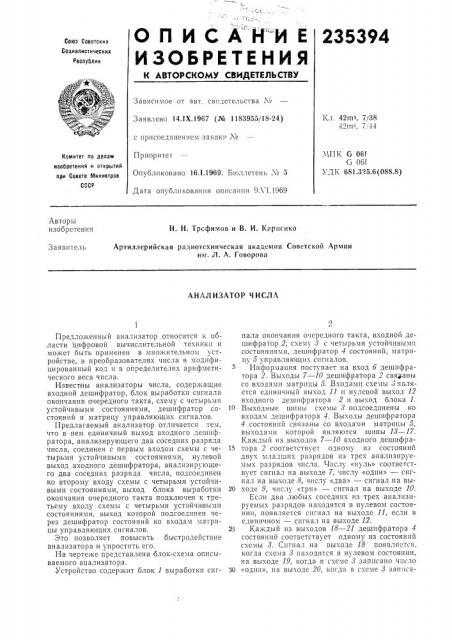

На чертеже представлена блок-схема описываемого анализатора.

Устройство содержит блок 1 выработки спгнала окончания очередного такта, входной дешифратор 2, схему 8 с четырьмя устойчивыми состояниями, дешифратор 4 состояний, матрицу 5 управляющих сигналов.

Информация поступает на вход 6 дешифратора 2. Выходы 7 — 10 дешифратора 2 связаны со входами матрицы 5. Входами схемы 8является единичный выход 11 и нулевой выход 12 входного дешифратора 2 и выход блока 1.

10 Выходные шины схемы 8 подсоединены ко входам дешифратора 4. Выходы дешифратора

4 состояний связаны со входами матрицы 5, выходами которой являются шины 18 — 17.

Каждый из выходов 7 — 10 входного дешифра15 тора 2 соответствует одному пз состояний двух младших разрядов из трех анализируемых разрядов числа. Числу «нуль» соответствует сигнал на выходе 7, числу «одпн» вЂ” сигнал на выходе 8, числу «дв໠— сигнал на вы20 ходе 9, числу «три» вЂ” сигнал на выходе 10.

Если два любых соседних из трех анализируемых разрядов находятся в нулевом состоянии, появляется сигнал на выходе 11, если в единичном — сигнал на выходе 12.

25 Каждый из выходов 18 — 21 дешифратора 4 состояний соответствует одному из состояний схемы 8. Сигнал на выходе 18 появляется, когда схема 8 находится в нулевом состоянии, на выходе 19, когда в схеме 8 записано число

30 «один», на выходе 20, когда в схеме 8 записа235394 но число «два», на выходе 21, когда в схеме

8 записано число «три».

При одновременном появлении сигнала на одном из выходов 7 — 10 входного дешифратора 2 и сигнала на одном из выходов 18 — 21 дешифратора 4 состояний возбуждается одна из выходных шин 18 — 17 матрицы 5.

Управляющие сигналы на выходе матрицы

5 появляются, если состояние двух младших разрядов из трех анализируемых разрядов числа соответствует модифицированному коду:

«нуль» — на шине 18, «один» вЂ” на шине 14, «дв໠— на шине 15, «минус один» вЂ” на шине

lб, «минус дв໠— на шине 17, Анализ числа осуществляется последовательно, начиная с младших разрядов.

В исходном положении схема 8 находится в нулевом состоянии. Схема 8 переводится; в состояние «один» сигналом с выхода 12 при условии, что схема находилась в нулевом состоянии; в состояние «два» сигналом с выхода блока

1 при условии, что схема находилась в состоянии «один»; в состояние «три» сигналом с выхода 11 при условии, что схема находилась в состоянии

«два»; в состояние «ноль» сигналом с выхода блока 1 при условии, что схема находилась в состоянии «три».

Сигнал на выходе матрицы 5 появляется: на шине 18, если возбуждены шина 17 и выход 18 или выходы 10 и 20; на шине 14, если возбуждены выходы 8 и

18 или выходы 7 и 21; на шине 15, если возбуждены выходы 9 и 18 или выходы 8 и 21; на шине lб, если возбуждены выходы 9 и 19 или выходы 8 и 20; на шине 17, если возбуждены выходы 10 и

19 или выходы 9 и 20.

Очередной управляющий сигнал передается: в множительное устройство для прибавления к частичной сумме сдвинутого на один разряд влево или без сдвига множимого в прямом или в обратном (дополнительном) коде (на чертеже не показан); в преобразователь в модифицированный код для записи чи1О сла в регистр модифицированного кода (на чертеже не показан); в определитель арифметического веса числа (на чертеже не показан).

После отработки управляющего сигнала в соответствующем устройстве появляется сигнал на выходе блока 1 и с задержкой, необходимой для отработки сигнала, с выхода блока 1 происходит сдвиг на два разряда вправо.

Предмет изобретения гю

Анализатор числа, содержащий входной дешифратор, блок выработки сигнала окончания очередного такта, схему с четырьмя устойчивыми состояниями, дешифратор состояний и

25 матрицу управляющих сигналов, отлича ощайся тем, что, с целью повышения быстродействия анализатора и упрощения его, в нем единичный выход входного дешифратора, анализирующего два соседних разряда числа, соедиЗО нен с первым входом схемы с четырьмя устойчивыми состояниями, нулевой выход входного дешифратора, анализирующего два соседних разряда числа, подсоединен ко второму входу схемы с четырьмя устойчивыми состояниями, 35 выход блока выработки окончания очередного такта подключен к третьему входу схемы с четырьмя устойчивыми состояниями, выход которой подсоединен через дешифратор состояний ко входам матрицы управляющих сигналов.

235394

13 14 15 16 17

Составигель А .А. Плащин

Редактор Е. В. Семанова Текред Л. К. Малова

Корректор О. Б. Тюрина

Заказ 728,8 Тираж 430 Подпггспое

ЦНИИПИ Комитета по дедам пзоорсге.гпй и открытий при Совстс Министров СССР

Москва, Центр, пр. Серова, д.

Типография, пр. Сапунова, 2