Устройство для формирования управляющих

Иллюстрации

Показать всеРеферат

ВсееaielsHas ймтент .;,. -.-: " -" :ичеси т:.

1 ибл и о тека qg

2354I6

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Заявлено 16.Х1.1967 (№ 1196709/18-24) с присоединением заявки ¹â€”

Приоритет

Опубликовано 16.1.1969. Бюллетень ¹ 5

Кл, 42m, 5/00

МПК Сх 06j

УДК 681.325(088.8) Комитет па делам изобретений и открытий при Совете Минивтров

СССР

Дата опубликования описания 9Л I.1969

Автор изобретения

Г. В. Москаленко

Заявитель

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ

СИГНАЛОВ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ

ПОРАЗРЯДНО ГО КОД И РОВАН ИЯ

Изобретение относится к област|т преобразования.и кодирования информации.

Известны устройства для формирования управляющих сигналов аналого-цифрового преобразователя,поразрядного кодирования, содержащие триггеры регистра, «единичные» выходы которых, за исключением выхода триггера старшего разряда, соединены со входами одноименных схем совпадения, и -схемы задержки.

Предложенное устройство отличается тем, что,в |нем «нулевые» выходы триггеров регистра, за исключением выхода триггера старшего разряда, соединены со входами им предшествующих -схем совпадения, причем выход схемы совпадения старшего разряда через cveму задержки соединен со входами схем сов,падения в цепях установки «единицы» триггеров старейшего и следующего за ним разрядов, а выходы остальных схем совпадения через схемы задержки соединены со входом схемы совпадения в цепи установки «нуля» тритгера своего разряда, а также со входом схемы совпадения в цепи установки «единицы» триггера следующего разряда. Это позволяет снизить требования к управляющим импульсам и улростить устройст|во.

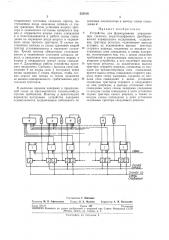

Блок-схема предложенного устройства представлена на чертеже.

Устройство состоит из регистра на триггерах 1 со входными схемами совпадения 2, которые образуют схему 8 запоминания результата в обычном .преобразователе с поразрядным кодированием. Единичные выходы всех триггеров 1, кроме .первого, соединены со входами только одноименных схем совпадения 4, а «нулевые» выходы всех триггеров 1, кроме перьвого, соединены со входами, всех предшествующих схем совпадения 4. Выход схемы совпадения 4 старшего разряда через схему задержки 5 соединен со входами схем совпадения 2 в цепях установки «единицы» триггеров старшего и следующего за ннм разрядов, а выходы остальных схем совпадения 4 через схему задержки 5 соединены со входом схемы совпадения 2 в цепи установки «нуля» триггера одноименного разряда, а также со входом схемы со впадения в цепи установки «еднницы»

20 триггера следующего разряда.

В исходном состоянии, когда определяется знак входной величины, открыта лишь одна первая схема совпадения 4, на входы которой поступают сигналы только с нулевых выходов триггеров. Выходной сигнал этой схемы открывает две схемы совпадения 2, в результате чего первый триггер (знаковый) может быть установлен, если это требуется, в «единичное» состояние сигналом с выхода схемы сра внения. Второй триггер устанавливается в

2354I6 Хо/й / с абнен я

Составитель Г. Шаповал

Редактор М. В. Афанасьева Техред Л. К. Малова

Корректор А. П. Васильева

Заказ 727/17 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, .пр Серова, д. 4

Типографии, пр, Сапунова, 2

«единичное» состояние сигналом опроса, поступающим после окончания сигнала со схемы сравнения. После установки второго триггера в «единичное» состояние задирается пер.вая и открывается вторая схема совпадения

4 и подготавливаются к работе схемы совпадения на «нулевом» входе:второго и <единичном» входе третьего триггеров. В случае поступления ситнала со схемы сравнения второй триггер уста на вливается в «нулевое» состояние. Третий триггер обязательно устанавливается в «единичное» состояние сигналом опроса, в результате чего запираются первая и вторая .и открывается третья схемы совпадения 4. Дальнейшая раббота устройства протекает аналогично. Сигналы с выходов схем совпадения 4,на входы схем 2 поступают через линии задержки 5 таким образом, чтобы сигнал опроса или сигнапл со схемы сравнения не вызвал одновременного срабатывания двух соседних триггеров.

К величине времени задержки .в предлагаемой схеме не, предъявляются сколько-нибудь строгие требования. Поэтому в прахтических вариантах построения устройства задержка осуществляется подключением небольшого по величине конденсатора к выходу схемы совпадения 4.

Предмет изобретения

5 Устройство для формиро вания управляющих сигналов аналого-цифрового преобразователя поразрядного кодирования, содержащее триггеры регистра, «единичные» выходы которых, за исключением выхода триггера

10 старшего разряда, соединены со входами одноименных схем совпадения, и схемы задержки, отличающееся тем, что, с целью снижения требований к управляющим импульсам и упрощения устройства, в нем «нулевые» выходы

15 триггеров регистра, .за исключением выхода триггера старшего разряда, соединены со входами,им предшествующих схем совпадения, причем выход схемы совпадения старшего разряда через схему задержки соединен со вхо20 дами схем совпадения в цепях установки

«еднницы» триггеров старшето и следующего за ним разрядов, а выходы остальных схем совпадения через схемы задержки соединены со входом схемы совладения в цепи установки

25 «нуля» триггера своего разряда, а также со

:входом схемы совпадения в цепи установки

«единицы» триггера следующего разряда.