Схема считывания сигналов из ячеек матрицы фотодетекторов

Иллюстрации

Показать всеИзобретение относится к технике машинного зрения и может быть использовано в оптических высокоскоростных мышках, видеокамерах и фотоаппаратах. Техническим результатом настоящего изобретения является повышение чувствительности и уменьшение количества компонентов в столбцовой схеме считывания. Указанный результат достигается за счет того, что в известном устройстве схемы считывания сигналов с активных ячеек фотодетекторов предложено первый электрод активного транзистора выполнить истоком, а второй стоком и между его стоком и затвором включить конденсатор обратной связи. В качестве элементов, обслуживающих сигнальную шину и шину постоянного потенциала восстановления, применить первый и второй генераторы втекающего и вытекающего тока, подключенные соответственно к сигнальной шине и шине постоянного потенциала, и транзистор обратной связи того же типа проводимости, что и у активного транзистора, исток которого соединен с шиной постоянного потенциала, сток - с общим выводом, затвор - с сигнальной шиной, являющейся выходом усилителя. Дополнительно предложено между стоком активного транзистора ячейки и ключом адресации каскадно включить транзистор того же типа проводимости. А между истоком транзистора обратной связи и шиной постоянного потенциала включить последовательно один или более транзисторов того же типа проводимости в диодном включении. Первый дополнительный признак улучшает точность предустановки потенциала на интегрирующем конденсаторе, второй расширяет размах выходного сигнала. 2 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к технике машинного зрения и может быть использовано в оптических высокоскоростных мышках, видеокамерах и фотоаппаратах.

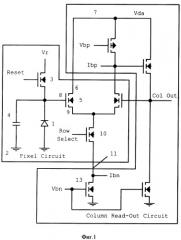

Известны схемы считывания сигналов с активных ячеек фотодетекторов, содержащие расположенные в ячейке транзисторный ключ восстановления потенциала на интегрирующем конденсаторе, активный транзистор, соединенный первым электродом с шиной источника питания, затвором - с интегрирующим конденсатором, вторым электродом - с ключом адресации, соединяющим его с сигнальной шиной, включаемые при замыкании ключей ячейки в схему распределенного усилителя, в которой элементы ячейки образуют входную часть усилитителя, а элементы, обслуживающие сигнальную шину и шину постоянного потенциала восстановления, образуют остальную часть усилителя. См., например: US Патент 6717616 B1, Apr. 6 2004, Morteza Afghahi и др. "Amplifier Assisted active pixel read out structure" и US Патент 7157682 B2, Jan. 2 2007, Kevin E. Brehmer и др. "Method and Apparatus for a CMOS image sensor with a distributed amplifier".

В этих источниках описываются устройства ячеек, содержащих истоковый повторитель, как активный транзистор, подключенный стоком к шине постоянного потенциала, а истоком через транзистор адресации к сигнальной шине, нагруженной на генератор тока, задающий рабочий режим распределенному дифференциальному усилителю, в котором истоковый повторитель при включенном транзисторе адресации становится входной ветвью.

Недостатком этих схем является недостаточная чувствительность при работе на высоких частотах считывания или сложность столбцовой части усилителя, затрудняющая ее размещение при малом шаге матрицы фотодетекторов.

Наиболее близким аналогом к заявленному изобретению является схема, описанная в US Патент 7157682 B2, Jan. 2 2007, Kevin E. Brehmer и др. "Method and apparatus for a CMOS image sensor with a distributed amplifier", имеющая те же недостатки.

Техническим результатом настоящего изобретения является повышение чувствительности и уменьшение количества компонентов в столбцовой схеме считывания.

Указанный результат достигается за счет того, что в известном устройстве схемы считывания сигналов с активных ячеек фотодетекторов предложено:

- первый электрод активного транзистора выполнить истоком, а второй стоком и между его стоком и затвором включить конденсатор обратной связи, в качестве элементов, обслуживающих сигнальную шину и шину постоянного потенциала восстановления, применить первый и второй генераторы втекающего и вытекающего тока, подключенные соответственно к сигнальной шине и шине постоянного потенциала, и транзистор обратной связи того же типа проводимости, что и у активного транзистора, исток которого соединен с шиной постоянного потенциала, сток - с общим выводом, затвор - с сигнальной шиной, являющейся выходом усилителя.

Дополнительно предложено:

- между стоком активного транзистора ячейки и ключом адресации каскодно включить транзистор того же типа проводимости.

- между истоком транзистора обратной связи и шиной постоянного потенциала включить последовательно один или более транзисторов того же типа проводимости в диодном включении.

Первый дополнительный признак улучшает точность предустановки потенциала на интегрирующем конденсаторе, второй расширяет размах выходного сигнала.

Перечень графических материалов, иллюстрирующих устройство, реализующее заявляемое изобретение.

Фиг.1 иллюстрирует известное устройство схемы считывания (прототип).

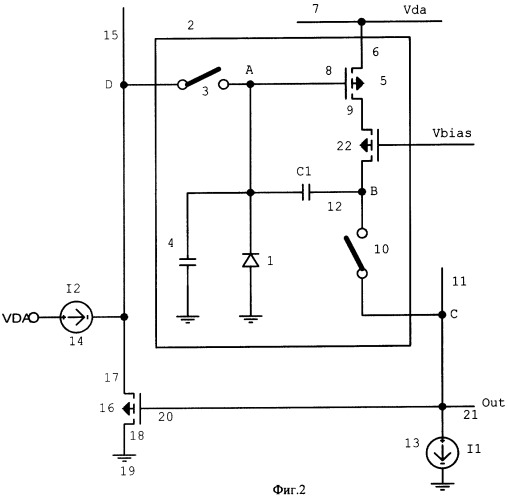

Фиг.2 показывает электрическую схему предлагаемой схемы считывания.

Схема считывания сигналов из ячеек матрицы фотодетекторов (1) состоит из расположенного в ячейке (2) транзисторного ключа (3) восстановления потенциала на интегрирующем конденсаторе (4), активного транзистора (5), соединенного первым электродом - истоком (6) с шиной источника питания (7), затвором (8) с интегрирующим конденсатором (4), вторым электродом - стоком (9) с ключом адресации (10), соединяющим его с сигнальной шиной (11), конденсатора обратной связи (12), включенного между его стоком (9) и затвором (8), при замыкании ключей ячейки (3, 10), образующих входную часть усилитителя, вторая (столбцовая) часть которого состоит из первого (13) и второго (14) генераторов втекающего и вытекающего тока, подключенных соответственно к сигнальной шине (11) и шине постоянного потенциала (15), транзистора (16) обратной связи того же типа проводимости, что и у активного транзистора (5), исток (17) которого соединен с шиной постоянного потенциала (15), сток (18) - с общим выводом (19), затвор (20) - с сигнальной шиной (11), являющейся выходом усилителя (21).

Дополнительно по п.2 формулы изобретения между стоком (9) активного транзистора (5) ячейки и ключом адресации (10) каскодно включен транзистор (22) того же типа проводимости.

Дополнительно по п.3 формулы изобретения между истоком (17) транзистора (16) обратной связи и шиной постоянного потенциала (15) включены последовательно один или более транзисторов (23) того же типа проводимости в диодном включении.

Схема работает следующим образом.

На этапе предустановки:

После включения транзисторных ключей (3 и 10) ячейка соединяется со столбцовыми элементами, образуя усилитель с двумя отрицательными обратными связями: динамической - через конденсатор (12) и статической - через транзистор (16). В установившемся режиме потенциал затвора (8) VA(0)=VDA-VGA(I1), где VGA(I1) - напряжение между истоком и затвором транзистора (5), поддерживающее ток I1. Потенциалы сигнальной шины (11) и точки В соединения конденсатора (12) со стоковой цепью активного транзистора (5) VC(0)=VB(0)=VDA-VGA(I1)-VGD(I2), где VGD(I2) - напряжение между истоком и затвором транзистора (16), поддерживающее ток I2.

На этапе накопления:

После отключения транзисторных ключей (3 и 10) в начале этапа VB=VDA из-за открытого активного транзистора (5). Скачок напряжения на В передается через конденсатор (12) на интегрирующий конденсатор (4) ΔVA=(VGA(I1)+VGD(I2))C1/(C1+CA). В конце этапа накопления длительностью Т напряжение на затворе активного транзистора понизится до VA(t)=VA(0)+ΔVA-IpT/(CA+C1)=VDA-VGA(I1)CA/(CA+CB)-VGD(I2)C1/(CA+C1)-IPT/(CA+C1), VB=VDA.

При считывании:

Ключ (10) замыкается и в образовавшемся усилителе в установившемся режиме в момент t, вследствие действия обратной связи через конденсатор (12), на затворе (8) активного транзистора (5) снова устанавливается начальное напряжение, соответствующее току I1: VA(t)=VDA-VGA(I1). На сигнальной шине (11) установится потенциал VC(t), поэтому изменение потенциала в точке В будет ΔVB(t)=VDA-VC(t) и соответствующее изменение потенциала на затворе активного транзистора будет ΔVA(t)=ΔVB(t) C1/(CA+C1). Учитывая, что ΔVA(t)=VA(T)-(VDA-VGA(I1))=VDA-VGA(I1)CA/(CA+CB)-VGB(I2)C1/(CA+C1)-IPT/(CA+C1)-(VDA-VGA(I1))=(VDA-VC(t))C1/(CA+C1), находим, что считываемый потенциал на сигнальной шине VC(t)=VDA-VGA(I1)-VGB(I2)+IPT/C1-VC(0)+IPT/C1. Относительно уровня черного VC(0) он изменяется в положительном направлении на величину IPT/C1, которая не зависит от величины интегрирующего конденсатора (4) СA. Величина конденсатора (12) C1 может быть сделана во много раз меньшей, чем СA и во столько же раз увеличится чувствительность.

Дополнительный транзистор (22) стабилизирует составляющую уровня черного VGA(I1) ввиду постоянства напряжения на стоке активного транзистора (5) при больших изменениях напряжения на сигнальной шине (11).

Каждый дополнительный транзистор в диодном включении в цепи истока (17) транзистора (16) изменяет составляющую уровня черного (-VGB(I2)) на такую же величину, увеличивая допустимый размах полезного сигнала

Настоящее описание изобретения, в т.ч. состава и работы устройства, включая предлагаемый вариант его исполнения, предполагает его дальнейшее возможное совершенствование специалистами и не содержит каких-либо ограничений в части реализации. Все притязания сформулированы исключительно в формуле изобретения.

1. Схема считывания сигналов из ячеек матрицы фотодетекторов, содержащая расположенные в ячейке транзисторный ключ восстановления потенциала на интегрирующем конденсаторе, активный транзистор, соединенный первым электродом с шиной источника питания, затвором с интегрирующим конденсатором, вторым электродом с ключом адресации, соединяющим его с сигнальной шиной, включаемые при замыкании ключей ячейки в схему распределенного усилителя, в которой элементы ячейки образуют входную часть усилитителя, а элементы, обслуживающие сигнальную шину и шину постоянного потенциала восстановления, образуют остальную часть усилителя, отличающаяся тем, что первый электрод активного транзистора является истоком, а второй стоком, между его стоком и затвором включен конденсатор обратной связи, элементами, обслуживающими сигнальную шину и шину постоянного потенциала восстановления, являются первый и второй генераторы втекающего и вытекающего тока, подключенные соответственно к сигнальной шине и шине постоянного потенциала, транзистор обратной связи того же типа проводимости, что и у активного транзистора, исток которого соединен с шиной постоянного потенциала, сток - с общим выводом, затвор - с сигнальной шиной, являющейся выходом усилителя.

2. Схема считывания по п.1, отличающаяся тем, что между стоком активного транзистора ячейки и ключом адресации каскодно включен транзистор того же типа проводимости.

3. Схема считывания по п.1, отличающаяся тем, что между истоком транзистора обратной связи и шиной постоянного потенциала включены последовательно один или более транзисторов того же типа проводимости в диодном включении.