Стартстопная система связи с частотной манипуляцией сигнала

Иллюстрации

Показать всеСтартстопная система связи относится к области радиосвязи и может использоваться в различных линиях связи. Достигаемый технический результат - повышение помехоустойчивости связи. Стартстопная система связи с частотной манипуляцией сигнала содержит на передающей стороне источник информации, первый регистр сдвига, схему ИЛИ, генератор несущих частот, передатчик, первый Т-триггер, первую схему И и генератор псевдослучайной последовательности, а на приемной стороне: приемник, частотный дискриминатор, прерыватель, согласованный фильтр, решающее устройство, формирователь импульсов, нелинейный элемент, первый сумматор, линию задержки, второй сумматор, пороговое устройство, RS-триггер, первый ключ, компаратор, второй регистр сдвига, второй ключ, схему выбора минимального сигнала, n переключателей, второй Т-триггер и вторую схему И. 3 ил.

Реферат

Изобретение относится к электро- и радиосвязи и может использоваться в проводных радио, радиорелейных и метеорных линиях связи.

Известна система связи для непрерывной передачи дискретной информации, в которой перед каждым сообщением посылается «зондирующий ключ». Если приходит этот сигнал, приемник открывается для регистрации сообщения и после приема отправляет квитанцию по обратному каналу. В противном случае приемник остается закрытым и передатчик повторяет сообщение, продолжая попытки для получения нужной квитанции [1]. Однако такая система связи имеет низкую помехоустойчивость, а в стартстопном режиме - недопустимо высокую вероятность ложной тревоги.

Наиболее близкой по технической сущности к предлагаемой системе связи является стартстопная система связи с частотной манипуляцией связи [2], принятая за прототип.

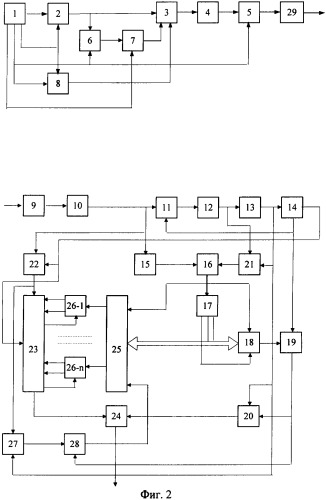

Схема системы-прототипа представлена на фиг.1, где обозначено

на передающей стороне:

1 - источник информации;

2 - первый регистр сдвига (PC);

3 - схема ИЛИ;

4 - генератор несущих частот (ГНЧ);

5 - передатчик;

8 - генератор псевдослучайной последовательности (ГПСП);

на приемной стороне:

9 - приемник;

10 - частотный дискриминатор (ЧД);

11 - прерыватель;

12 - согласованный фильтр (СФ);

13 - решающее устройство (РУ);

14 - формирователь импульсов (ФИ);

15 - нелинейный элемент (НЭ);

16 - первый сумматор;

17 - линия задержки (ЛЗ) с n отводами;

18 - второй сумматор;

19 - пороговое устройство (ПУ);

20 - RS-триггер;

21 - первый ключ;

22 - компаратор;

23 - второй PC;

24 - второй ключ;

29 - линия связи.

Система-прототип содержит на передающей стороне: последовательно соединенные источник информации 1, первый PC 2, схему ИЛИ 3, ГНЧ 4 и передатчик 5, а также ГПСП 8, выход которого соединен со вторым входом схемы ИЛИ 3, причем второй выход источника информации 1 соединен с тактовым входом первого PC 2 и первым входом ГПСП 8, второй вход которого соединен с третьим выходом источника информации 1 и вторым входом передатчика 5, а на приемной стороне содержит: последовательно соединенные приемник 9, ЧД 10, прерыватель 11, СФ 12, РУ 13 и ФИ 14, последовательно соединенные НЭ 15, первый сумматор 16 и ЛЗ 17, последовательно соединенные второй сумматор 18, первые n входов которого подключены через шину к выходам ЛЗ 17, а (n+1)-ый вход соединен с ее входом; ПУ 19 и RS-триггер 20; второй ключ 21 и последовательно соединенные компаратор 22, второй PC 23 и второй ключ 24, выход которого является выходом системы, причем первый выход ФИ 14 подключен к тактовым входам компаратора 22 и второго PC 23, а его второй выход соединен со вторыми входами прерывателя 11 и ПУ 19, выход ЧД 10 подключен к сигнальному входу компаратора 22 и входу НЭ 15, выход СФ 12 соединен первым входом первого ключа 21, второй вход первого ключа 21 объединен с выходом РУ 13 и вторым входом RS-триггера 20, а его выход подключен ко второму входу первого сумматора 16, выход RS-триггера 20 соединен со вторым входом второго ключа 24; приемная и передающая стороны системы соединены посредством линии связи 29. Система-прототип работает следующим образом.

Источник информации 1 в случайный момент времени создает на первом выходе сообщение, состоящее из n двоичных символов одинаковой длительности τ, а на втором и третьем выходах в момент начала сообщения - сетку из S коротких импульсов с периодом следования τ и положительный импульс, соответственно. При этом в ГПСП 8 формируется синхросигнал - псевдослучайная двоичная последовательность, состоящая из S элементов длительности τ, а сообщение задерживается в PC 2 на время, равное Sτ. В результате этого на выходе схемы ИЛИ 3 формируется последовательность, состоящая из синхросигнала и сообщения. Элементы этих сигналов используются для управления частотой ГНЧ 4. Полученный частотно-манипулированный сигнал усиливается в передатчике 5, включаемом импульсом длительности (n+S)τ, действующем на третьем выходе источника информации 1, и передается по линии связи 29.

На приемной стороне после общей фильтрации в приемнике 9 осуществляется демодуляция полученного сигнала в ЧД 10 и согласованная фильтрация синхросигнала в СФ 12, который вместе с блоком 13 составляет первый измерительный канал, представляющий собой устройство оптимального измерения временного положения синхросигнала (см., например, стр.115, рис.7.2 в книге Ю.С.Лезина «Введение в теорию и технику радиотехнических систем», М., «Радио и связь», 1986 г.).

В РУ 13 осуществляется сравнение входного сигнала с определенным порогом и, при условии его превышения сигналом, - формирование в момент действия его максимального значения короткого импульса, который при отсутствии помех точно совпадает по времени с моментом окончания синхросигнала при приеме. По положительному фронту этого импульса на первом выходе ФИ 14 с задержкой на время τ создается сетка из 2n коротких тактовых импульсов длительности α (α<<τ) с периодом τ, а на втором - импульс длительностью nτ+2α, который с помощью прерывателя 11 отключает вход СФ 12 от выхода блока 10. В компараторе 22 в момент действия первых n выходных тактовых импульсов блока 14 по знаку выходных сигналов ЧД 10 выносятся решения о приеме n двоичных символов сообщения, которые теми же импульсами записываются в (n+1)-разрядный PC 23, следующие n тактовые импульсы считывают информацию из PC 23 на первый вход второго ключа 24. Выходной сигнал СФ 12 в момент действия выходного импульса РУ 13 с выхода первого ключа 21 через первый сумматор 16 поступает в Л3 17 с n отводами, расстояние между которыми (по времени) равно τ.

В НЭ 15 вычисляются модульные значения элементов выходного сигнала ЧД 10, которые через этот же сумматор 16 поступают на вход ЛЗ 17. Затем входной сигнал ЛЗ 17 и выходные сигналы с n ее выходов суммируются во втором сумматоре 18 и полученный сигнал в момент действия заднего фронта импульса на втором выходе ФИ 14 сравнивается в ПУ 19 с определенным порогом. При условии превышения им порога RS-триггер 20, установленный выходным импульсом РУ 13 в нулевое состояние, переводится в единичное состояние. При этом открывается ключ 24 и информация с его первого входа передается на его выход. Если порог в ПУ 19 сигналом не превышается, то входной сигнал блока 24 на его выход поступать не будет.

Недостаток системы-прототипа - низкая помехоустойчивость связи.

Изобретение направлено на повышение помехоустойчивости связи.

Для достижения этого в стартстопную систему связи с частотной манипуляцией сигнала (СССЧМ), содержащую на передающей стороне последовательно соединенные источник информации, первый PC, схему ИЛИ, ГНЧ и передатчик, а также ГПСП, выход которого соединен со вторым входом схемы ИЛИ, причем второй выход источника информации соединен с тактовым входом первого PC и первым входом ГПСП, второй вход ГПСП соединен с третьим выходом источника информации и вторым входом передатчика, а на приемной стороне - последовательно соединенные приемник, ЧД, прерыватель, СФ, РУ и ФИ; последовательно соединенные НЭ, первый сумматор и ЛЗ; последовательно соединенные второй сумматор, первые n входов которого подключаются через шину к n выходам ЛЗ, а (n+1)-ый вход соединен со входом ЛЗ, пороговое устройство и RS-триггер; первый ключ и последовательно соединенные компаратор, второй PC и второй ключ, выход которого является выходом СССЧМ, причем первый выход ФИ подключен к тактовым входам компаратора и второго PC, а его второй выход соединен со вторыми входами прерывателя и ПУ, выход ЧД подключен к сигнальному входу компаратора и входу НЭ, выход СФ соединен с первым входом первого ключа, второй вход первого ключа объединен с выходом РУ и вторым входом RS-триггера, а выход первого ключа подключен ко второму входу первого сумматора, выход RS-триггера соединен со вторым входом второго ключа; приемная и передающая стороны СССЧМ соединены посредством линии связи, согласно изобретению введены на передающей стороне: четвертый выход источника информации, третий вход схемы ИЛИ и последовательно соединенные первый Т-триггер и первая схема И, второй вход которой соединен с четвертым выходом источника информации, а выход подключен к третьему входу схемы ИЛИ, причем счетный вход первого Т-триггера соединен с выходом первого PC, а его установочный вход - с третьим выходом источника информации, а на приемной стороне дополнительно введены: (n+1)-ый отвод ЛЗ, 2n установочных входов и n выходов второго PC, (n+2)-ой вход второго сумматора, подключенный к (n+1)-му отводу ЛЗ, схема выбора минимального сигнала (СВМ), соединенная n входами через шину с первыми n выходами ЛЗ, а (n+1)-ым - со входом ЛЗ, n переключателей, каждый из которых соединен первым входом с соответствующим выходом СВМ, вторым - с соответствующим выходом второго PC, а парой выходов - с соответствующей парой установочных входов второго PC; последовательно соединенные второй Т-триггер, подключенный счетным входом к выходу компаратора, а установочным входом - к выходу РУ, и вторая схема И, выход которой соединен со стробирующим входом СВМ, а второй вход - с выходом ПУ.

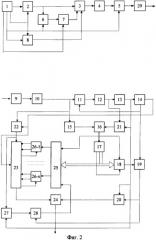

На фиг.2 представлена функциональная схема предлагаемой СССЧМ.

Она содержит на передающей стороне последовательно соединенные источник информации 1, первый PC 2, схему ИЛИ 3, ГНЧ 4 и передатчик 5; последовательно соединенные первый Т-триггер 6 и первую схему И 7, второй вход которой подключен к четвертому выходу источника информации 1, а выход - к третьему входу схемы ИЛИ 3, причем счетный вход первого Т-триггера 6 соединен с выходом PC 2, а его установочный вход объединен с третьим выходом источника информации 1 и вторым входом передатчика 5; ГПСП 8, первый вход которого объединен с тактовым входом PC 2 и подключен ко второму выходу источника информации, второй вход соединен с третьим выходом источника информации 1, а выход подключен ко второму входу схемы ИЛИ 3, а на приемной стороне содержит: последовательно соединенные приемник 9, ЧД 10, прерыватель 11, СФ 12, РУ 13 и ФИ 14; последовательно соединенные НЭ 15, первый суммматор 16 и ЛЗ 17; последовательно соединенные второй сумматор 18, первые n входов которого подключены через шину к n выходам ЛЗ 17, (n+1)-ый вход подключен ко входу ЛЗ 17, а (n+2)-ой - к (n+1)-му выходу ЛЗ 17, ПУ 19 и RS-триггер 20; первый ключ 21 и последовательно соединенные компаратор 22, второй (n+2)-разрядный PC 23 и второй ключ 24, выход которого является выходом СССЧМ, причем первый выход ФИ 14 подключен к тактовым входам компаратора 22 и второго PC 23, а его второй выход соединен со вторыми входами прерывателя 11 и ПУ 19, выход ЧД 10 подключен к сигнальному входу компаратора 22 и входу НЭ 15, выход СФ 12 соединен с первым входом первого ключа 21, второй вход которого объединен с выходом РУ 13 и вторым входом RS-триггера 20, а его выход подключен ко второму входу первого сумматора 16, выход RS-триггера 20 соединен со вторым входом второго ключа 24; а также содержит: СВМ 25, соединенную n входами через шину с первыми n выходами ЛЗ 17, а (n+1)-ым - со входом ЛЗ 17, n переключателей (26-1)-(26-n), каждый из которых соединен первым входом с соответствующим выходом СВМ 25, вторым - с соответствующим выходом PC 23 (начиная с выхода второго разряда), а парой выходов - с соответствующей парой установочных входов PC 23 (начиная с пары установочных входов второго разряда); последовательно соединенные второй Т-триггер 27, подключенный счетным входом к выходу компаратора 22, а установочным входом - к выходу РУ 13, и вторую схему И 28, выход которой соединен со стробирующим входом СВМ 25, а второй вход - с выходом ПУ 19; приемная и передающая стороны СССЧМ соединены посредством линии связи 29.

Стартстопная система связи с частотной манипуляцией сигнала работает следующим образом.

Источник информации 1 в случайный момент времени создает на первом выходе сообщение, состоящее из n-двоичных символов одинаковой длительности τ, на втором и третьем выходах в момент начала сообщения - сетку из S коротких импульсов с периодом следования τ и положительный импульс, соответственно, а на четвертом - импульс длительности τ в момент действия последнего импульса на его втором выходе.

При этом в ГПСП 8 формируется синхросигнал - псевдослучайная двоичная последовательность, состоящая из S элементов длительности τ, а сообщение задерживается в PC 2 на время, равное Sτ.

Если число символов «1» в сообщении нечетное, то Т-триггер 6, установленный передним фронтом импульса, действующего на третьем выходе источника информации 1 в состояние «0», переходит в состояние «1» и этот сигнал пропускает через первую схему И 7 на третий вход схемы ИЛИ 3 импульс с четвертого выхода источника информации 1, являющийся проверочным символом кода. При четном числе символов «1» в сообщении импульс на третий вход схемы ИЛИ 3 не поступит. В результате всего этого на выходе схемы ИЛИ 3 формируется последовательность, состоящая из синхросигнала, сообщения и символа «1» или «0» (в зависимости от числа символов «1» в сообщении). Элементы этих сигналов используются для управления частотой ГНЧ 4. Полученный частотно-манипулированный сигнал усиливается в передатчике 5, включаемом импульсом длительности (n+S+1)τ, действующем на третьем выходе источника информации и передается по линии связи 29.

На приемной стороне после общей фильтрации в приемнике 9 осуществляется демодуляция полученного сигнала в ЧД 10, и согласованная фильтрация синхросигнала - в СФ 12, который вместе с блоком 13 составляет первый измерительный канал такой же, что и в системе-прототипе. В РУ 13 осуществляется сравнение входного сигнала с определенным порогом и, при условии его превышения сигналом, - формирование в момент действия его максимального значения короткого импульса, длительности α, который при отсутствии помех точно совпадает по времени с моментом получения синхросигнала при приеме. По положительному фронту этого импульса на первом выходе ФИ 14 с задержкой на время τ создается сетка из [(n+1)+n] коротких тактовых импульсов длительности α с периодом τ, а на втором выходе - импульс длительности (n+1)τ+0,5α, который с помощью прерывателя 11 отключает вход СФ 12 от выхода блока 10. В компараторе 22 в момент действия передних фронтов первых (n+1) выходных тактовых импульсов блока 14, по знаку выходных сигналов ЧД 10 выносятся решения о приеме n двоичных символов сообщения и проверочного символа кода, которые теми же импульсами записываются в (n+2)-разрядный PC 23. Выходной сигнал СФ 12 в момент действия выходного импульса РУ 13 с выхода первого ключа 21 через первый сумматор 16 поступает в ЛЗ 17 с (n+1) отводами, расстояние между которыми (по времени) равно τ.

В НЭ 15 вычисляются модульные значения элементов выходного сигнала ЧД 10, которые через этот же сумматор 16 поступают на вход ЛЗ 17. Затем входной сигнал ЛЗ 17, выходные сигналы с первых n ее входов (шина) и выходной сигнале (n+1)-го дополнительного выхода суммируются во втором сумматоре 18 и полученный сигнал в момент действия заднего фронта импульса на втором выходе ФИ 14, сравниваются в ПУ 19 с определенным порогом. При условии превышения им порога RS-триггер 20, установленный выходным импульсом РУ 13 в нулевое состояние, переводится в единичное состояние. При этом открывается ключ 24. Если порог в ПУ 19 сигналом не превышается, то ключ 24 не открывается. Блоки 25, 26, 27 и 28 предназначены для обнаружения и коррекции одиночной ошибки в принятой кодовой комбинации. Для этого на входы СВМ 25 подаются входной сигнал ЛЗ 17 и ее выходные сигналы (по шине) с n-первых отводов, а на первый вход второго Т-триггера 27 - (n+1) выходных двоичных символов блока 22. Если число символов «1» оказывается при этом нечетным (что свидетельствует об искажении помехами кодовой комбинации), то на выходе второй схемы И 28 в момент действия переднего фронта выходного сигнала ПУ 19 будет действовать перепад напряжения и в СВМ 25 произойдет выборка номера выходного сигнала с наименьшим уровнем, так что только на одном из ее выходов будет действовать импульс с уровнем «1», а на остальных - нулевой сигнал.

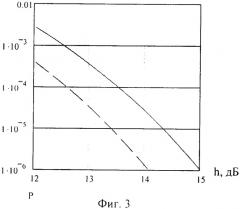

Этот импульс поступит на вход соответствующего переключателя 26, на второй вход которого подается выходной сигнал соответствующего разряда PC 23 и, если его уровень, например будет равным «1», то импульс с первого входа переключателя поступит на один из пары его выходов, который установит соответствующий разряд PC 23 в противоположное состояние. Таким образом произойдет исправление ошибочно принятого символа. Последними n выходными импульсами с первого выхода ФИ 14 информация из PC 23 будет считана через открытый ключ 24 на выход системы связи. Естественно, что такой метод коррекции ошибок не позволяет исправить их с вероятностью, равной единице. Однако расчеты показали, что при реальных отношениях сигнал/шум в канале связи 12-14 дБ вероятность ошибочного приема сообщения оказывается меньше, чем в системе-прототипе почти на порядок. Причем сравнение двух систем проводилось при одинаковых энергетических затратах при передаче. Это преимущество предлагаемой системы по сравнению с известной иллюстрируют кривые зависимости вероятности ошибочного приема сообщения Р (при n=12) от отношения с/ш h (где пунктирной линией нанесена кривая для предлагаемой системы, а сплошной - для известной), полученные методом статистического моделирования.

Таким образом, применение предложенной стартстопной системы связи с частотной манипуляцией сигнала позволяет повысить помехоустойчивость связи.

Источники информации

1. Каневский З.М., Ледовских В.И. Передача дискретной информации по каналам с обратной связью с прерываниями. «Электросвязь», №2, 1970 г.

2. Г.Б.Волобуев, В.И.Ледовских. О помехоустойчивости стартстопных систем связи с частотной манипуляцией сигнала. «Теория и техника радиосвязи», вып.№2, 1998 г.

Стартстопная система связи с частотной манипуляцией сигнала, содержащая на передающей стороне последовательно соединенные источник информации, первый регистр сдвига, схему ИЛИ, генератор несущих частот и передатчик, а также генератор псевдослучайной последовательности, выход которого соединен со вторым входом схемы ИЛИ, причем второй выход источника информации соединен с тактовым входом первого регистра сдвига и первым входом генератора псевдослучайной последовательности, второй вход генератора псевдослучайной последовательности соединен с третьим выходом источника информации и вторым входом передатчика, а на приемной стороне - последовательно соединенные приемник, частотный дискриминатор, прерыватель, согласованный фильтр, решающее устройство и формирователь импульсов; последовательно соединенные нелинейный элемент, первый сумматор и линию задержки; последовательно соединенные второй сумматор, первые n входов которого подключаются через шину к n выходам линии задержки, а (n+1)-й вход соединен со входом линии задержки, пороговое устройство и RS-триггер; первый ключ и последовательно соединенные компаратор, второй регистр сдвига и второй ключ, выход которого является выходом системы связи, причем первый выход формирователя импульсов подключен к тактовым входам компаратора и второго регистра сдвига, а его второй выход соединен со вторыми входами прерывателя и порогового устройства, выход частотного дискриминатора подключен к сигнальному входу компаратора и входу нелинейного элемента, выход согласованного фильтра соединен с первым входом первого ключа, второй вход первого ключа объединен с выходом решающего устройства и вторым входом RS-триггера, а выход первого ключа подключен ко второму входу первого сумматора, выход RS-триггера соединен со вторым входом второго ключа; приемная и передающая стороны системы связи соединены посредством линии связи, отличающаяся тем, что в нее введены на передающей стороне: четвертый выход источника информации, третий вход схемы ИЛИ и последовательно соединенные первый Т-триггер и первая схема И, второй вход которой соединен с четвертым выходом источника информации, а выход подключен к третьему входу схемы ИЛИ, причем счетный вход первого Т-триггера соединен с выходом первого регистра сдвига, а его установочный вход - с третьим выходом источника информации, а на приемной стороне дополнительно введены: (n+1)-й отвод линии задержки, 2n установочных входов и n выходов второго регистра сдвига, (n+2)-й вход второго сумматора, подключенный к (n+1)-му отводу линии задержки, схема выбора минимального сигнала, соединенная n входами через шину с первыми n выходами линии задержки, а (n+1)-м - со входом линии задержки, n переключателей, каждый из которых соединен первым входом с соответствующим выходом схемы выбора минимального сигнала, вторым - с соответствующим выходом второго регистра сдвига, а парой выходов - с соответствующей парой установочных входов второго регистра сдвига; последовательно соединенные второй Т-триггер, подключенный счетным входом к выходу компаратора, а установочным входом - к выходу решающего устройства, и вторая схема И, выход которой соединен со стробирующим входом схемы выбора минимального сигнала, а второй вход - с выходом порогового устройства.