Цифровой синтезатор частотно- и фазомодулированных сигналов

Иллюстрации

Показать всеИзобретение относится к электронно-вычислительной технике, предназначено для синтеза частотно- и фазомодулированных сигналов и может использоваться в радиолокации, навигации и адаптивных системах связи. Достигаемый технический результат - обеспечение возможности независимого управления синтезируемым сигналом как по частоте, так и по фазе. Цифровой синтезатор частотно-модулированных и фазомодулированных сигналов содержит эталонный генератор, блок задержки, первый регистр памяти, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель, сумматор, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, третий регистр памяти, делитель частоты с переменным коэффициентом деления, четвертый регистр памяти, третий цифровой накопитель. 2 ил.

Реферат

Изобретение относится к электронно-вычислительной технике, предназначено для синтеза частотно-модулированных и фазомодулированных сигналов и может использоваться в радиолокации, навигации и адаптивных системах связи.

Изобретение позволяет проводить независимую модуляцию синтезируемого сигнала как по частоте, так и по фазе.

Известны цифровые синтезаторы частот фазомодулированных сигналов, содержащие блок постоянного запоминания, три регистра памяти, два цифровых накопителя, делитель с переменным коэффициентом деления, эталонный генератор, блок задержки, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, ждущий мультивибратор и два сумматора [1].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор частот, содержащий последовательно соединенные эталонный генератор и блок задержки, последовательно соединенные первый блок постоянного запоминания, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот; второй блок постоянного запоминания и счетчик с предварительной установкой; входами цифрового синтезатора являются входы первого и второго блоков ПЗУ, а выходом - выход фильтра нижних частот [2]. Однако в известных цифровых синтезаторах нет возможности задавать начальную фазу синтезируемого сигнала.

Изобретение позволяет расширить функциональные возможности цифровых синтезаторов и дает возможность синтезировать частотно-модулированные и фазомодулированные сигналы.

Положительный эффект - обеспечение возможности управления начальной фазой синтезируемого сигнала - достигается за счет того, что в цифровой синтезатор частотно-модулированных и фазомодулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок задержки; последовательно соединенные первый регистр памяти, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель; последовательно соединенные преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, выход которого является выходом всего устройства, а входами цифрового синтезатора частотно-модулированных и фазомодулированных сигналов являются входы первого и третьего регистров памяти; последовательно соединенные третий регистр памяти, делитель частоты с переменным коэффициентом деления и первый цифровой накопитель; выходы блока задержки подсоединены к тактовому входу делителя с переменным коэффициентом деления, тактовому входу цифроаналогового преобразователя, тактовым входам первого и второго цифровых накопителей, причем новым является то, что введены последовательно соединенные четвертый регистр памяти, третий цифровой накопитель и сумматор, второй вход сумматора подключен к выходу второго цифрового накопителя, а выход сумматора подключен к входу преобразователя кодов, причем выход старшего выходного разряда суммы сумматора подсоединен к входу управления инверсией преобразователя кодов; выход блока задержки подсоединен к тактовому входу третьего цифрового накопителя; а третьим входом цифрового синтезатора частотно-модулированных и фазомодулированных сигналов является вход четвертого регистра памяти.

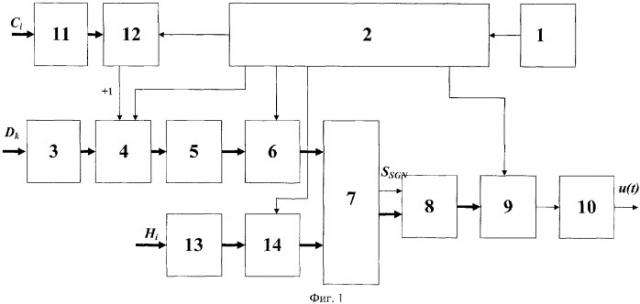

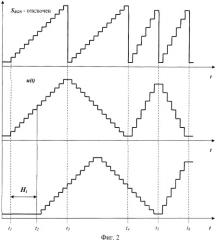

На фиг.1 приведена структурная схема цифрового синтезатора частотно-модулированных и фазомодулированных сигналов, на фиг.2 - графики сигналов на выходе ЦАП устройства.

Цифровой синтезатор частотно-модулированных и фазомодулированных сигналов (фиг.1) содержит эталонный генератор 1, блок задержки 2, первый регистр памяти 3, первый цифровой накопитель 4, второй регистр памяти 5, второй цифровой накопитель 6, сумматор 7, преобразователь кодов 8, цифроаналоговый преобразователь 9, фильтр нижних частот 10, третий регистр памяти 11, делитель частоты с переменным коэффициентом деления 12, четвертый регистр памяти 13, третий цифровой накопитель 14.

Цифровой синтезатор частотно-модулированных и фазомодулированных сигналов работает следующим образом. На вход первого регистра памяти 3 поступает код начальной частоты Сi, а на вход третьего регистра памяти 11 - код Dk, определяющий коэффициент деления делителя 12 и скорость изменения частоты цифрового вычислительного синтезатора.

Эталонный генератор 1 выдает сигнал опорной частоты синусоидальной формы, который поступает на вход блока задержки 2, формирующий разнесенные во времени последовательности прямоугольных импульсов формы «меандр», которые поступают на тактовые входы делителя с переменным коэффициентом деления 12, первого и второго цифровых накопителей 4 и 6, а также тактовый вход цифроаналогового преобразователя 9 и служат для синхронизации работы цифрового синтезатора.

С первым тактовым импульсом в момент t1 (фиг.2) код начальной частоты Сi из первого регистра памяти 3 записывается в первый цифровой накопитель 4, код коэффициента деления Dk из третьего регистра памяти 11 записывается в делитель с переменным коэффициентом деления 12, а код начальной фазы Hi из четвертого регистра памяти 13 записывается в третий цифровой накопитель 14.

Затем с каждым тактовым импульсом код А на выходе первого цифрового накопителя 4 будет изменяться следующим образом:

Код А поступает на вход второго цифрового накопителя 6, результат суммирования в котором будет изменяться по формуле:

Код В поступает на второй вход сумматора 7, а на первый его вход поступает код Нi с выхода третьего цифрового накопителя 14.

Код S на выходе сумматора 7 изменяется по формуле:

Результат суммирования с выхода сумматора 7 поступает на вход преобразователя кодов 8, причем старший разряд кода суммы SSGN является знаковым и поступает на вход управления инверсией преобразователя кодов 8. Остальные N старших разрядов (где N - разрядность ЦАП) через преобразователь кодов поступают на информационные цифроаналогового преобразователя (ЦАП) 9. Если SSGN=0, то на ЦАП поступает прямой двоичный код суммы, если SSGN=1, то на ЦАП 9 поступает обратный код суммы.

На выходе ЦАП 9 формируется ступенчатый сигнал «треугольной» формы, который подается на ФНЧ 10. Фильтр нижних частот 10 имеет частоту среза fcp<fm/2, где fm - тактовая частота, и пропускают на выход синтезатора только первую гармонику сформированного сигнала.

Если принять, что φi=Hi - начальная фаза, f0=Сi+1 - начальная частота; 0.5f'=1/Dk - скорость изменения частоты синтезируемого сигнала, Δt=Т - период следования тактовых импульсов, то тогда на выходе фильтра нижних частот 10 формируется сигнал, амплитуда которого изменяется по формуле:

где f0 - начальная частота синтезируемого сигнала, f' - скорость изменения частоты синтезируемого сигнала, φi - начальная фаза сигнала. Таким образом, в цифровом синтезаторе появилась возможность управлять фазой и частотой синтезируемого сигнала.

Источники информации

1. Патент Российской Федерации №2204196, МПК H03L 7/18, Цифровой синтезатор фазомодулированных сигналов / Рябов И.В., Рябов В.И. - Заявл. 13.03.2001. Опубл. 10.05.2003. Бюл. №13.

2. Патент Российской Федерации №2058659, МКИ Н03В 19/00, Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. - Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. №11. (Прототип).

Цифровой синтезатор частотно-модулированных и фазомодулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок задержки; последовательно соединенные первый регистр памяти, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель; последовательно соединенные преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот, выход которого является выходом всего устройства, а входами цифрового синтезатора частотно-модулированных и фазомодулированных сигналов являются входы первого и третьего регистров памяти; последовательно соединенные третий регистр памяти, делитель частоты с переменным коэффициентом деления и первый цифровой накопитель; соответствующие выходы блока задержки подсоединены к тактовому входу делителя с переменным коэффициентом деления, к тактовому входу цифроаналогового преобразователя, тактовым входам первого и второго цифровых накопителей, отличающийся тем, что введены последовательно соединенные четвертый регистр памяти, третий цифровой накопитель и сумматор, второй вход сумматора подключен к выходу второго цифрового накопителя, а выход сумматора подключен к входу преобразователя кодов, причем выход старшего выходного разряда суммы сумматора подсоединен к входу управления инверсией преобразователя кодов; выход блока задержки подсоединен к тактовому входу третьего цифрового накопителя; а третьим входом цифрового синтезатора частотно-модулированных и фазомодулированных сигналов является вход четвертого регистра памяти.