Компенсационный акселерометр

Иллюстрации

Показать всеИзобретение предназначено для применения в качестве чувствительного элемента в системах стабилизации и навигации и может найти применение в приборах измерения механических величин компенсационного типа. Компенсационный акселерометр содержит последовательно включенные по информационным входам чувствительный элемент, датчик угла, предварительный и избирательные усилители, включенные в одну из отрицательных обратных связей. Введение в компенсационный акселерометр двух отрицательных обратных связей (аналоговой и цифровой), содержащих усилители, фильтр верхних частот, компаратор, преобразователи уровня сигнала, логические схемы ИЛИ, фазовый сдвигатель, логические блоки, реверсивные двоичные счетчики, сумматоры, двоичный умножитель, генератор тока, электронный ключ, позволило создать устройство для измерения ускорений с расширенной полосой пропускания и с астатизмом по отклонению за счет введения в цифровую отрицательную обратную связь двоичного умножителя. 4 ил.

Реферат

Изобретение относится к измерительной технике и может быть использовано в качестве элемента в системах стабилизации и навигации. Оно может найти применение в приборах измерения механических величин компенсационного типа.

Известно устройство для измерения ускорений (патент РФ № 2098833, МПК6 G01P 15/13, опубл. 10.12.97), содержащее чувствительный элемент, включающий в себя два неподвижных электрода и подвижную пластину, три усилителя, два резистора, при этом выход первого усилителя подключен к первому резистору, а вход второго усилителя соединен со вторым резистором и является выходом устройства. Для повышения помехоустойчивости при воздействии электрических помех в него введен источник опорного напряжения, генератор электрического сигнала, две транзисторные пары, три резистора, два конденсатора, позволяющих, за счет охвата усилителя отрицательной обратной связью, осуществлять компенсацию электрических помех.

Недостатком данного устройства является низкая точность измерения, так как выбор коэффициента усиления с жесткой отрицательной обратной связью ограничен условием устойчивости системы.

Наиболее близким по техническому решению является устройство (патент РФ № 2308039, МПК6 G01P 15/13 (2006.01), опубл. в бюл. № 28, 10.10.2007), содержащее чувствительный элемент, датчик угла и датчик момента с электронным ключом, две отрицательные обратные связи, одна с выхода датчика угла на вход датчика моментов через последовательно соединенные по информационным входам предварительный и избирательные усилители, первый компаратор, первый преобразователь уровня сигнала, пару логических схем И, первую пару ЖСГ, пару схем ИСКЛЮЧАЮЩЕЕ ИЛИ, реверсивный двоичный счетчик, двоичный умножитель и электронный ключ, вторая отрицательная обратная связь введена с выхода избирательного усилителя на входы пары схем ИСКЛЮЧАЮЩЕЕ ИЛИ через последовательно соединенные по информационным входам сумматор, амплитудный детектор, фильтр верхних частот, второй компаратор, второй преобразователь уровня сигнала, вторую пару ЖСГ, кроме того, дополнительные входы пары логических схем И и сумматора соединены с выходом ГОН, а дополнительные входы первой и второй пары ЖСГ схемы управления соединены с выходом генератора вспомогательной частоты через схему формирования вспомогательной частоты, дополнительный вход двоичного умножителя соединен с выходом вспомогательного реверсивного двоичного счетчика, в обратную цепь которого введена схема управления, второй вход электронного ключа соединен с выходом генератора тока и выход основного реверсивного двоичного счетчика является цифровым выходом устройства для измерения ускорений.

Недостатком подобного устройства является низкая точность измерения, обусловленная точностью работы аналоговых усилителей и порогового элемента. Кроме того, точность измерения зависит от параметров схемы электронного ключа, осуществляющего выборку информации. Эта погрешность приводит к апертурной ошибке, свойственной подобной схеме выборки и обработки информации.

Задачей настоящего изобретения является расширение полосы пропускания устройства и повышение точности измерения.

Это достигается за счет того, что в компенсационный акселерометр, содержащий последовательно включенные по информационным входам чувствительный элемент, датчик угла, один из входов которого соединен с выходом генератора опорного напряжения, предварительный и избирательные усилители, цифровую отрицательную обратную связь с первого выхода избирательного усилителя, в которую включены компаратор, первый преобразователь уровня сигнала, первая логическая схема ИЛИ, первый реверсивный двоичный счетчик, выход которого является цифровым выходом компенсационного акселерометра, двоичный умножитель, один из входов которого соединен с выходом первого реверсивного двоичного счетчика, электронный ключ, второй вход которого соединен с выходом генератора тока, и датчик момента, аналоговую отрицательную обратную связь со второго выхода избирательного усилителя, включающую сумматор, а также вторую логическую схему ИЛИ, второй реверсивный двоичный счетчик, выход которого соединен с другим входом двоичного умножителя, и генератор вспомогательной частоты, введены со второго входа избирательного усилителя на вход датчика момента последовательно по информационным входам фильтр верхних частот и преобразователь напряжение-ток, выход которого соединен с входом сумматора, первый логический блок, вход которого соединен с выходом первого преобразователя уровня сигнала, а выход - с входом первой логической схемы ИЛИ, первый выход избирательного усилителя соединен также с вычитающим входом первого реверсивного двоичного счетчика через последовательно соединенные по информационным входам второй сумматор, второй преобразователь уровня сигнала, второй логический блок, вторую логическую схему ИЛИ, один из выходов первого логического блока соединен с входом второй логической схемы ИЛИ, выход второго логического блока соединен с входом первой логической схемы ИЛИ, кроме того, вход первого логического блока соединен с выходом генератора опорного напряжения через фазовый сдвигатель и дополнительные входы второго логического блока, второго сумматора соединены с выходом генератора опорного напряжения, в обратную цепь второго реверсивного двоичного счетчика введена третья логическая схема ИЛИ, вход которой соединен с выходом генератора вспомогательной частоты.

Введение в компенсационный акселерометр двух отрицательных обратных связей, содержащих усилители, фильтр верхних частот, компаратор, преобразователи уровня сигнала, логические схемы и блоки, фазовый сдвигатель, реверсивные двоичные счетчики, сумматоры, двоичный умножитель, генератор тока, электронный ключ позволило создать компенсационный акселерометр с расширенной полосой пропускания и с астатизмом по отклонению за счет введения в цифровую отрицательную обратную связь двоичного умножителя.

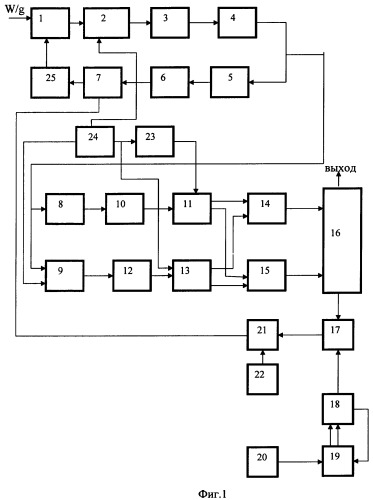

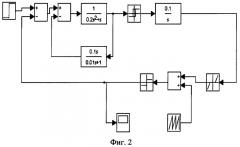

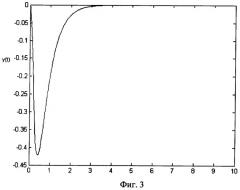

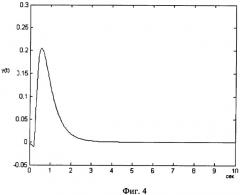

На фиг.1 изображена функциональная схема компенсационного акселерометра, на фиг.2 - структурная схема компенсационного акселерометра, на фиг.3, 4 - переходный процесс в аналоговой модели акселерометра.

Компенсационный акселерометр содержит чувствительный элемент 1, отклонение которого фиксирует датчик угла 2, выход датчика угла 2 соединен с входом предварительного усилителя 3, выход которого соединен с входом избирательного усилителя 4. Один из выходов избирательного усилителя 4 соединен с входом фильтра верхних частот 5, выход которого соединен с входом преобразователя напряжение-ток 6, выход которого соединен с входом первого сумматора 7. Другой выход избирательного усилителя 4 соединен как с входом компаратора 8, так и с входом второго сумматора 9. Выход компаратора 8 соединен с входом первого преобразователя уровня сигнала 10, выход которого соединен с входом первого логического блока 11. Выход второго сумматора 9 соединен с входом второго преобразователя уровня сигнала 12, выход которого соединен с входом второго логического блока 13. Один из выходов второго логического блока 13 соединен с одним из входов первого логической схемы ИЛИ 14, другой выход второго логического блока 13 соединен с входом второй логической схемы ИЛИ 15. Один из выходов первого логического блока 11 соединен с одним из входов первой логической схемы ИЛИ 14. Другой выход первого логического блока 11 соединен с одним из входов второй логической схемы ИЛИ 15. Выходы логических схем 14 и 15 соединены с суммирующим и вычитающим входами первого реверсивного двоичного счетчика 16. Выход первого реверсивного двоичного счетчика 16 соединен с одним из входов двоичного умножителя 17. Другой вход двоичного умножителя 17 соединен с выходом второго реверсивного двоичного счетчика 18, входы которого соединены с выходами третьей логической схемы ИЛИ 19. Вход третьей логической схемы ИЛИ 19 соединен с выходом генератора вспомогательной частоты 20 и с выходом второго реверсивного двоичного счетчика 18. Выход двоичного умножителя 17 соединен с одним из входов электронного ключа 21, другой вход которого соединен с выходом генератора тока 22. Выход электронного ключа 21 соединен с одним из входов первого сумматора 7, выход которого соединен с входом датчика момента 25. Второй вход первого логического блока 11 соединен, через фазовый сдвигатель 23, с выходом генератора опорного напряжения 24. Входы второго логического блока 13, второго сумматора 9 и датчика угла 2 соединены с выходом генератора опорного напряжения 24.

Внутреннее содержание предварительного и избирательного усилителей, компаратора, фильтра верхних частот, реверсивного двоичного счетчика, двоичного умножителя, сумматора, преобразователя уровня сигнала, фазового сдвигателя, логических блоков и схем, генератора тока, схемы электронного ключа, генератора опорного напряжения и формирования вспомогательной частоты описаны в книге: П.Хоровиц, У.Хилл. Искусство схемотехники. М.: Мир, т.1-3, 1993.

Устройство для измерения ускорений работает следующим образом. При действии ускорения W на чувствительный элемент 1, выполненный в виде маятника, действует инерционный момент, равный mlW (I, m - приведенная длина и масса маятника). Под действием этого момента происходит отклонение чувствительного элемента 1, которое фиксируется датчиком угла 2 обмотки, возбуждения которого соединены с выходом генератора опорного напряжения ГОН 24. Сигнал с датчика угла 2, после усиления предварительным усилителем 3, поступает на вход избирательного усилителя 4, который выделяет сигнал на несущей частоте f1 (ГОН), который затем поступает на вход фильтра верхних частот 5. Сигнал с выхода фильтра 5 поступает на вход преобразователя напряжение-ток 6, а затем на вход первого сумматора 7. Сигнал в виде напряжения ±U4 с усилителя 4 поступает на вход компаратора 8. Напряжение с компаратора 8 поступает на вход первого преобразователя уровня сигнала 10, в котором вырабатывается сигнал в виде напряжения от 0 до ±2.5 (В). Выходные сигналы с ГОН 24 и с выхода избирательного усилителя 4 поступают на вход второго сумматора 9 и суммируются. Сигнал, смещенный по уровню в зависимости от фазы отклонения чувствительного элемента 1, с выхода второго сумматора 9 поступает на вход второго преобразователя уровня сигнала 12, в котором происходит преобразования сигнала на несущей частоте в сигнал постоянного тока. Преобразователи уровня сигнала 10 и 12 выдают необходимый уровень напряжения для работы логических блоков 11 и 13. На второй вход первого логического блока 11 подается сигнал с выхода ГОН 24 через фазовый сдвигатель 23, а на второй вход второго логического блока 13 - с выхода ГОН 24. Первый логический блок 11 осуществляет операцию умножения сигналов с выхода 10 и с выхода 23. Второй логический блок 13 осуществляют операцию умножения сигналов с выхода ГОН 24 и с выхода второго преобразователя уровня 12. Срабатывание логических блоков 11 и 13 осуществляется на несущей частоте ГОН 24 в зависимости от сигнала фазового сдвигателя 23 и от фазы отклонения 1. Фильтр верхних частот 5, включенный в аналоговую отрицательную обратную связь, обеспечивает в устройстве для измерения ускорений заданный переходный процесс (фиг.3 и фиг.4). Выходы первого логического блока 11 соединены с входами первой логической схемы ИЛИ 14 и второй логической схемы ИЛИ 15. Выходы второго логического блока 13 соединены с входами как первой логической схемы ИЛИ 14, так и второй логической схемы ИЛИ 15. В результате логического сложения сигналов схемами 14 и 15, в зависимости от фазы отклонения 1, получим логический "0" либо логическую "1". Импульсы с 14 или 15 подаются либо на суммирующий вход первого реверсивного двоичного счетчика 16, либо на вычитающий вход 16. Информация равная разности "положительных" и "отрицательных" импульсов с 16 переписывается в двоичный умножитель 17 по импульсу второго реверсивного двоичного счетчика 18, в обратную цепь которого введена третья логическая схема ИЛИ 19. Формирование импульсов счета схемой 19 осуществляется в соответствии с частотой генератора вспомогательной частоты 20, включенного на вход схемы 19. Импульсы с двоичного умножителя 17 поступают на один из входов электронного ключа 21 в соответствии с знаком отклонения чувствительного элемента 1. Другой вход электронного ключа 21 соединен с генератором тока 22. Сигнал в виде ШИМа (широтно-импульсной модуляции) с выхода электронного ключа 21 поступает на вход один из входов первого сумматора 7. Сигнал с выхода 7 поступает на токовую обмотку датчика моментов 25, который развивает момент, по модулю и знаку компенсирующий угловое отклонение 1. Выходом устройства для измерения ускорений является цифровой код с выхода первого реверсивного двоичного счетчика 16.

Введение в компенсационный акселерометр двух отрицательных обратных связей, содержащих усилители, компараторы, преобразователи уровня сигнала, сумматор, логические блоки и схемы, двоичный умножителя, реверсивные двоичные счетчики, позволяет создать устройство для измерения ускорений с астатизмом первого порядка и с расширенной полосой пропускания. Причем одна аналоговая отрицательная обратная связь обеспечивает устойчивость и заданное качество переходного процесса, а другая, цифровая отрицательная обратная связь обеспечивает выдачу информации в цифровом коде.

Аналоговая модель компенсационного акселерометра (фиг.2) промоделирована при параметрах: T=0.2 с, T1=0.1 с, T2=0.01 c, K1=0.1, при ширине зоны неоднозначности порогового элемента, включенного в обратную связь, равной 0.01, и результаты моделирования представлены на фиг.3 и фиг.4 (соответственно при входном воздействии, меньшем нуля и большем нуля). Из анализа переходных процессов следует, что устройство устойчиво, устойчивость обеспечивает фильтр верхних частот, включенный в аналоговую отрицательную обратную связь.

Компенсационный акселерометр, содержащий последовательно включенные по информационным входам чувствительный элемент, датчик угла, один из входов которого соединен с выходом генератора опорного напряжения, предварительный и избирательный усилители, цифровую отрицательную обратную связь с первого выхода избирательного усилителя, в которую включены компаратор, первый преобразователь уровня сигнала, первая логическая схема ИЛИ, первый реверсивный двоичный счетчик, выход которого является цифровым выходом компенсационного акселерометра, двоичный умножитель, один из входов которого соединен с выходом первого реверсивного двоичного счетчика, электронный ключ, второй вход которого соединен с выходом генератора тока, и датчик момента, аналоговую отрицательную обратную связь со второго выхода избирательного усилителя, включающую сумматор, а также вторую логическую схему ИЛИ, второй реверсивный двоичный счетчик, выход которого соединен с другим входом двоичного умножителя, и генератор вспомогательной частоты, отличающийся тем, что в него введены со второго входа избирательного усилителя на вход датчика момента последовательно по информационным входам фильтр верхних частот и преобразователь напряжение-ток, выход которого соединен с входом сумматора, первый логический блок, вход которого соединен с выходом первого преобразователя уровня сигнала, а выход с входом первой логической схемы ИЛИ, первый выход избирательного усилителя соединен также с вычитающим входом первого реверсивного двоичного счетчика через последовательно соединенные по информационным входам второй сумматор, второй преобразователь уровня сигнала, второй логический блок, вторую логическую схему ИЛИ, один из выходов первого логического блока соединен с входом второй логической схемы ИЛИ, выход второго логического блока соединен с входом первой логической схемы ИЛИ, кроме того, вход первого логического блока соединен с выходом генератора опорного напряжения через фазовый сдвигатель и дополнительные входы второго логического блока, второго сумматора соединены с выходом генератора опорного напряжения, в обратную цепь второго реверсивного двоичного счетчика введена третья логическая схема ИЛИ, вход которой соединен с выходом генератора вспомогательной частоты.