Трехкаскадная коммутационная система

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и связи. Технический результат заключается в расширении функциональных возможностей трехкаскадной коммутирующей системы за счет обеспечения процесса настройки новых каналов связи на фоне передачи информации по ранее настроенным каналам, а также в сокращении времени настройки каналов связи за счет сокращения числа шагов настройки системы. Система содержит входной, промежуточный и выходной каскады соответствующих блоков коммутации X, R, Z (X=1, …, x, R=1, …, r, Z=1, …, z). Входы данных блоков Х входного каскада образуют информационные входы системы, выходы данных блоков Z выходного каскада образуют информационные выходы системы. Система работает в трех режимах: настройки, при которой производятся поиск и фиксация каналов связи, передачи информации, полной или частичной разборки каналов связи, при этом процесс настройки новых каналов связи происходит на фоне передачи информации по ранее настроенным каналам. Для управления системой используются тринадцать управляющих входов системы. 9 ил.

Реферат

Устройство предназначено для применения в вычислительной технике и связи.

Известен цифровой коммутатор с пространственным разделением каналов (см. патент США №4417245, 1983 г.). Однако в данном устройстве отсутствует возможность осуществления процесса настройки коммутатора на фоне передачи информации.

Наиболее близким по технической сути является трехкаскадная коммутирующая система, используемая в многопроцессорных вычислительных системах, состоящая из входного, промежуточного и выходного каскадов, каждый из которых содержит группу блоков коммутации, каждый блок коммутации содержит матрицу ячеек коммутации и узел управления. Каждая ячейка коммутации блоков коммутации входного и промежуточного каскадов содержит узел сравнения, узел разборки канала связи, элементы памяти-триггеры, элементы И и ИЛИ. Каждая ячейка коммутации блоков коммутации выходного каскада содержит узел разборки канала связи, элемент памяти-триггер, элементы И. (см. а.с. СССР №1226481, 1985 г.).

Недостаток устройства состоит в невозможности осуществления процесса настройки коммутирующей системы на фоне передачи информации, так как фазы настройки каналов связи, передачи информации и разборки каналов связи четко разграничены.

Техническая задача: создание схемы трехкаскадной коммутационной системы с параллельной настройкой и передачей информации, выполняющей одновременный поиск всех необходимых каналов связи, передачу информации со входов на выходы по образованным каналам связи, и обеспечивающей процесс настройки новых каналов связи на фоне передачи информации по ранее настроенным каналам.

Технический результат: расширение функциональных возможностей трехкаскадной коммутирующей системы за счет обеспечения процесса настройки новых каналов связи на фоне передачи информации по ранее настроенным каналам, а также сокращение времени настройки каналов связи за счет сокращения числа шагов настройки системы.

Он достигается тем, что в каждый коммутационный блок выходного каскада известной трехкаскадной коммутирующей системы введены буферные запоминающие устройства. Адресные входы буферных оперативных запоминающих устройств (ОЗУ) соединены с выходами счетчиков. Входы установки буферных ОЗУ в третье состояние соединены с дополнительными вертикальными координатными шинами. Выходы ячеек коммутации, расположенные в одном вертикальном ряду коммутационного блока выходного каскада, подключены к соответствующей дополнительной вертикальной шине.

Установлены дополнительные триггеры (с инверсными входами), входы установки

«» которых соединены с одной стороны с выходами элементов И, которые соединены этими же выходами со входами соответствующих регистров циклического сдвига, с другой стороны, входы установки «» соединены с дополнительной шиной, которая подключена к выходу инвертора, на вход которого подается управляющий потенциал Н0. Входы сброса «» дополнительных триггеров соединены с одним из выходов буферных ОЗУ, а выходы данных триггеров соединены со входами дополнительного элемента И, сигнал с выхода которого подается на центральное управляющее устройство (ЦУУ).

Кроме этого во все коммутационные блоки промежуточного каскада вводятся инверторы, число которых равно числу триггеров, на входы «S» которых подается потенциал начальной установки исходного состояния системы СИ0. В предлагаемой коммутационной системе вместо данного потенциала на входы установки «S» триггеров подается потенциал Н0. Вход каждого инвертора соединен с одной стороны с выходом узла ускоренного распространения сигнала занятости входной координатной шины, а с другой стороны - со входами сброса «R» триггеров, выход инверторов соединен со входами установки «S» триггеров.

Кроме этого во всех коммутационных блоках входного каскада использованы элементы двухвходовое И, число которых равно числу линий связи между блоками входного и промежуточного каскада, и постоянные запоминающие устройства (ПЗУ) с третьим состоянием на выходе, число которых равно числу информационных входов системы. Кроме этого в предлагаемое устройство введены дополнительные вертикальные и горизонтальные шины, подключенные к одному выходу соответствующих ячеек коммутации. Дополнительный вход (вход установки элемента в третье состояние) каждого элемента двухвходовое И, подключенного своим выходом к одной вертикальной информационной шине, соединен с дополнительной вертикальной шиной, а дополнительный входы ПЗУ, подключенного к одной горизонтальной информационной шине, соединен с соответствующей дополнительной горизонтальной шиной.

Кроме этого в каждую ячейку коммутации коммутационных блоков выходного каскада введены два дополнительных элемента двухвходовое И. На один вход первого элемента двухвходовое И подается настроечный потенциал, второй вход этого же элемента соединен с инверсным выходом триггера ячейки коммутации, а выход - со входом одного из уже установленных в существующей коммутирующей системе элементов четырехвходовое И. Первый вход второго дополнительного элемента И соединен с прямым выходом триггера, на второй вход этого элемента подается потенциал фиксации каналов связи, а выход соединен с дополнительной координатной шиной блока коммутации выходного каскада.

В каждую ячейку коммутации коммутационных блоков промежуточного каскада введен дополнительный элемент двухвходовое И, один вход которого подключен к инверсному выходу триггера управления, на второй вход подается потенциал настройки коммутирующей системы, а выход соединен со входом узла сравнения ячейки коммутации. В каждую ячейку коммутации коммутационных блоков входного каскада введен дополнительный элемент двухвходовое И, один вход которого подключен к инверсному выходу триггера, на второй вход подается потенциал настройки коммутирующей системы, а выход соединен со входом узла сравнения ячейки коммутации.

Сигнал с прямого выхода триггера ячейки коммутации коммутационных блоков входного каскада снимается и подается на две дополнительные горизонтальные и вертикальные координатные шины коммутационного блока входного каскада.

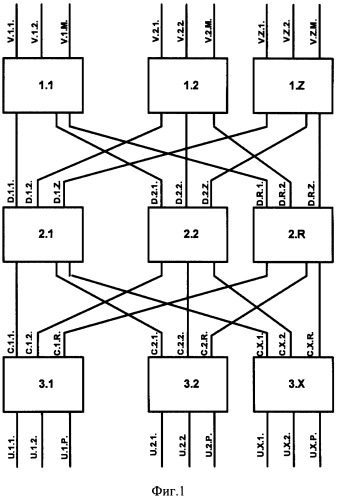

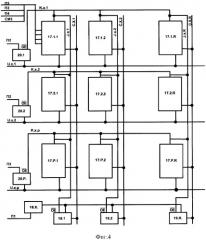

На фиг.1 представлена структурная схема трехкаскадной коммутационной системы, на фиг.2-4 - функциональные схемы блоков коммутации соответственно выходного, промежуточного и входного каскадов, на фиг.5-7 - функциональные схемы ячеек коммутации соответственно выходного, промежуточного и входного каскадов, на фиг.8 - функциональная схема буферного ОЗУ, на фиг.9 - временная диаграмма управляющих сигналов.

Предлагаемая коммутационная система (фиг.1) содержит z блоков коммутации 1.1, 1.2, …, 1.Z, образующих выходной каскад, r блоков коммутаций 2.1, 2.2, …, 2.R, образующих промежуточный каскад, × блоков коммутации 3.1, 3.2, …, 3.Х, образующих входной каскад, р×х информационных входов системы (U.x.p), являющихся одновременно входами данных блоков коммутации 3.Х входного каскада, m×z информационных выходов системы (V.z.m.), являющихся одновременно выходами данных блоков коммутации выходного каскада, линии связи (С.х.r.) между блоками 3.Х и 2.R входного и промежуточного каскадов, соединяющие выходы данных блоков 3.Х входного каскада с входами данных блоков 2.R промежуточного каскада, и линий связи (D.r.z.) между блоками 2.R и 1.Z промежуточного и выходного каскадов, соединяющие соответствующие выходы данных блоков 2.R с входами данных блоков 1.Z.

При этом Z=1, …, z; P=1, … p; R=1, …, r; X=1, …, x; M=1, …, m.

Коммутационная система содержит также следующие управляющие входы: ТИ-вход тактовых импульсов; Н0- вход установки триггеров коммутационных блоков входного и промежуточного каскадов в состояние «1»; СИ0 - вход начальной установки состояния регистров циклического сдвига; П0 - вход настройки; П1 - первый вход синхронизации, соответствующий первому полушагу настройки; П2 - второй вход синхронизации, соответствующий второму полушагу настройки; СИ1 - первый вход запуска для запуска узлов сравнения; СИ2 - вход разблокировки для разрешения конфликта при занятии линий связи C.X.R; СИ3 - второй вход запуска для запуска узлов сравнения во втором полушаге настройки; СИ4 - вход фиксации каналов связи; СИ5 - вход поиска незаблокированных каналов связи; П3 - вход разборки каналов связи; П4 - вход разрешения передачи информации.

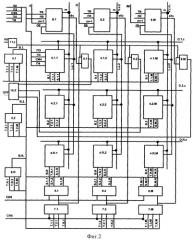

Каждый блок 1.Z выходного каскада (фиг.2) состоит из матрицы ячеек 4.R.M. коммутации и узла управления, содержащего группу регистров циклического сдвига 5.М., первую группу элементов И 6.R., вторую группу элементов И 7.М. У блока 1.Z. через S.m.r. обозначены прямые выходы r-ых разрядов регистров циклического сдвига 5.М.

Кроме этого каждый блок 1.Z. содержит 8.М. буферных запоминающих устройств RAM типа FIFO, информация в которые записывается по мере считывания из внешнего ОЗУ. Каждое буферное ОЗУ имеет четыре входа, управляющих работой данного ОЗУ и два выхода данных. Первый выход данных соединен с информационными выходами системы (V.z.m.), а второй выход данных соединен с «» входами триггеров 9.М. Вход (вход установки буферного ОЗУ в третье состояние) каждого запоминающего устройства подключен к общей координатной шине L.z.m. Вход CS каждого ОЗУ 8.М. подключен к выходу тактового генератора управляющего устройства, а вход разрешения считывания команд коммутации из каждого буферного ОЗУ 8.М. W/R подключен к выходу П0. Прямые выходы триггеров 9.М. соединены со входами элемента И 10.Z., потенциал с выхода которого подается на центральное управляющее устройство. Потенциал Н0 подается на входы «» триггеров 9.М. через инвертор 11.Z.

Каждый блок 2.R. промежуточного каскада (фиг.3) состоит из узлов ускоренного распространения сигнала занятости 12.Х., матрицы ячеек 13.Z.X. коммутации, группы триггеров 14.Х. и группы элементов И 15.Х.

Кроме этого каждый блок 2.r. состоит из элементов И 16.Х.

Каждый блок 3.Х. (фиг.4) входного каскада состоит из матрицы ячеек коммутации 17.P.R., элемента 18.Х. идентификатора блока коммутации, группы ключей (элементов И) 19.R. и элементов памяти 20.Р. идентификаторов входов Р.

В свою очередь, каждая ячейка 4.R.M. (фиг.5) состоит из триггера 21 коммутации, узла разборки каналов связи 22, элементов И 23-26, а также элементов И 27 и И 28. Через T.r.m. обозначен инверсный выход триггера 21, являющийся выходом занятости ячейки.

Каждая ячейка коммутационного блока промежуточного каскада 13.Z.X. (фиг.6) состоит из элемента ИЛИ 29, узла сравнения 30, триггеров 31 коммутации и 32 управления, элемента запрета 33, узла 34 разборки каналов связи, элементов И 35-38.

Кроме этого ячейка состоит из элемента И 39. На первый вход элемента И 39 подается потенциал настройки П0, а второй вход подключен к инверсному выходу триггера управления 32.

Кроме того, в каждом коммутирующем узле 13.Z.X. имеется вход F.Z.X. признака занятости входной координатной шины и выход E.Z.X. занятости ячейки, необходимые для разрешения конфликта при распределении линий связи С.Х.r.

Каждая ячейка коммутационного блока входного каскада 17.Р.R (фиг.5) состоит из элемента И 40, узла 41 разборки канала связи, элемента ИЛИ 42, узла сравнения 43 и триггера коммутации 44. Кроме этого ячейка содержит элемент И 45, на первый вход которого подается потенциал настройки П2, второй вход подключен к инверсному выходу триггера 44, а выход подключен ко входу узла сравнении 43. С прямого выхода триггера коммутации 44 снимается сигнал .

Предлагаемая трехкаскадная коммутационная система с параллельной настройкой и передачей информации может работать в трех режимах: в режиме настройки, при котором производится поиск и фиксация каналов связи, в режиме передачи информации и в режиме разборки каналов связи, ставших ненужными. При этом передача информации может идти на фоне настройки и разборки каналов связи.

Работа коммутационной системы начинается с установки в прямое состояние триггеров 14.Х. и 9.М. Это осуществляется импульсом, поданным на вход Н0 коммутационной системы. Установка коммутационной системы в такое исходное состояние подготавливает ее для настройки каналов связи.

Импульс Н0 также устанавливает в инверсное состояние триггеры 21 через узлы разборки каналов связи 22 в каждой ячейке 4.R.M., триггеры 31 через узлы разборки каналов связи 34 и элемент ИЛИ 29, триггеры 32 через узлы разборки каналов связи 34 в каждой ячейке 13.Z.X. и триггеры 44 через узлы разборки каналов связи 41 и элементы ИЛИ 42 в каждой ячейке 17.P.R.

Режим настройки коммутационной системы начинается с установки всех регистров циклического сдвига 5.М. в исходное состояние. Это осуществляется импульсом, поданным на вход СИ0 коммутационной системы.

Этот импульс, поступая на входы регистров циклического сдвига 5.М., записывает в них соответствующий код, содержащий только одну единицу в том разряде, к прямому входу которого подключен вход СИ0. Таким образом, после записи этих кодов в регистрах 5.М., расположенных в пределах одного блока 1.Z., не будет существовать одинаковых кодов. В регистрах сдвига 5.1. единица записана в первом разряде, в регистрах сдвига 5.2 - во втором и т.д. Наконец, в регистрах сдвига 5.М. единица записана в разряде М. После записи кодов потенциал с прямого выхода S.m.r. разряда, содержащего единицу, каждого регистра 5.М. поступает на соответствующие элементы И 23 и 24, и готовят их к приему информации.

Поиск и фиксация каналов связи в режиме настройки осуществляется в коммутационной системе под воздействием программы коммутации и управляющих сигналов, появляющихся на соответствующих управляющих входах системы в соответствии с временной диаграммой, изображенной на фиг.9. Программа коммутации представляет собой упорядоченное в соответствии с расположением выходов V.z.m. коммутационной системы множество команд коммутации, представляющих собой пары (р.х.), идентифицирующих те входы U.x.p. коммутационной системы, с которыми необходимо соединить соответствующий выход V.z.m. При этом х является адресом блока 3.Х., в котором расположен нужный вход, а р - адрес нужного входа в пределах этого блока. В элементах памяти 18.Х. и 20.р. кажого блока 3.Х. хранятся соответственно идентификатор х этих блоков и идентификатор р входов U.x.p. коммутационной системы.

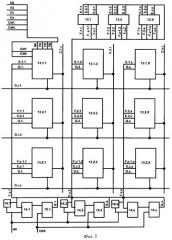

Команда коммутации состоит из m=log2(P×X) разрядов. При записи команд коммутации в буферное ОЗУ из внешнего ОЗУ по шине I.M к m-разрядной команде коммутации добавляется дополнительный нулевой бит.Таким образом, в каждой ОЗУ 8.М. хранятся N (m+1)-разрядных пар (р.х.). Функциональная схема буферного ОЗУ представлена на фиг.8. Информация из внешнего ОЗУ записывается в буферное ОЗУ под управлением счетчиков 46.М, подключенных к адресным входам ОЗУ 47.М. На вход данных DI ОЗУ 47.М. поступают (m+1)-разрядные команды коммутации из внешнего ОЗУ по шине I.M. Выходы Q1-Qn счетчиков соединены с адресными входами A1-An ОЗУ 47.М. На вход CS ОЗУ 47.М. (который разрешает или запрещает его работу) поступают тактовые импульсы ТИ. На вход разрешения записи/чтения W/R из ОЗУ 47.М. поступают сигналы управления П0. Каждое буферное ОЗУ 8.М. имеет два выхода данных. Один выход соединен с информационным выходом коммутационной системы V.z.m., а второй выход соединен со входом сброса триггера 9.М.

Дальнейшая работа коммутационной системы в режиме настройки непосредственно связана с поиском и фиксацией каналов связи в соответствии с подпрограммой коммутации. Подпрограмма коммутации - это совокупность (m+1)-разрядных пар (р.х.), одновременно поступающих на выходы буферных ОЗУ 8.М. Особенностью работы предлагаемой коммутационной системы в этом режиме является то, что в системе ведется поиск одновременно всех необходимых каналов связи в соответствии с подпрограммой коммутации.

Каждый шаг настройки выполняется за два полушага. В течение первого полушага производится поиск каналов связи через блоки 2.R. промежуточного каскада к блокам 3.Х. входного каскада. На втором полушаге производится поиск каналов связи для конкретных входов U.x.p. в блоках коммутации 3.Х., образование ветвящихся в блоках коммутации 2.R. каналов связи с выходами V.z.m., если в подключенных к ним буферных ОЗУ 8.М. хранится одинаковая адресная информация и фиксация найденных каналов во всех блоках коммутации коммутационной системы.

При настройке накопившееся к данному моменту времени множество команд коммутации, представляющих собой подпрограмму коммутации, параллельно считывается из буферных ОЗУ 8.М. и поступает на свободные информационные выходы системы V.z.m.

Первый полушаг первого шага настройки начинается подачей на входы П0, П1 и СИ1 управляющих сигналов, изображенных на временной диаграмме.

Сигнал П0, поступая на вход записи/чтения информации W/R буферных ОЗУ 8.М., разрешает выдачу хранящихся в них команд коммутации на соответствующие выходы V.z.m. коммутационной системы. Этот же сигнал поступает на входы всех элементов И 27 во всех ячейках 4.R.M. В результате те элементы И 27, на вторые входы которых поступил сигнал «1» с инверсных выходов триггеров 21, будут подготовлены к приему настроечной информации. В свою очередь, сигнал с выходов элементов И 27, сигнал с прямых выходов S.m.r. тех разрядов циклического сдвига 5.М., которые хранят единицы, и разрешающий сигнал с выхода В.r. элементов И 6.R., поступающий на третьи управляющие входы элементов И 24, готовят эти элементы к приему настроечной информации.

Среди всех элементов И 24, подключенных входом к одному и тому же выходу V.z.m., будет только один подготовлен к приему информации. Аналогично среди всех элементов И 24, подключенных к одной линии связи D.r.z, будет только один подготовлен к передаче информации.

Потенциал П0 разрешает выдачу (m+1) разрядов команд коммутации из буферного ОЗУ 8.М. Последний нулевой бит команд коммутации «0» поступает на вход сброса «» триггеров 9.М. и переводит их в нулевое состояние. Оставшиеся m разрядов команд коммутации поразрядно начнут поступать по подключенному к буферному ОЗУ 8.М. выходу V.z.m через подготовленный элемент И 24 по соответствующей линии связи D.r.z. на входы узлов сравнения 30, расположенных в ячейках 13.Z.X., подключенных к одной линии связи. Естественно, что прежде всего будут поступать разряды адреса Х блоков 3-Х.

Только те узлы сравнения 30, на которые подается положительный потенциал П0 через элемент И 39, будут подготовлены к сравнению адресов X. В свою очередь, только те элементы И 39, на вторые входы которых поступил сигнал «1» с инверсных выходов триггеров управления 32, будут подготовлены к приему настроечного потенциала П0.

С другой стороны, сигнал со входа П1, поступая на входы элементов памяти 18.Х. в блоках 3-Х., разрешает поразрядную передачу адресов Х всех блоков 3-Х. Адрес Х элемента памяти 18.Х. в каждом блоке 3.Х. через открытый ключ 19.R. (элемент И), поступает одновременно на все свободные от передачи информации линии связи C.x.R, связанные с этим блоком. Ключ 19.R находится в закрытом состоянии (третье состояние на выходе) в случае, если хотя бы через одну ячейку коммутации 17.P.R., подключенную к линии связи C.x.R, установлен канал связи. В данном случае сигнал с прямого выхода триггера 44 ячейки коммутации 17.P.R. проходит по шине J.x.R ко входу ключа 19.R. и устанавливает элемент 19.R. в третье состояние, тем самым запрещая передачу адреса Х блока 3.Х. на соответствующую линию связи C.x.R.

По свободным линиям связи С.Х.r. адреса Х поступают на вторые входы узлов сравнения 30, подготовленные к сравнению информации.

Сигналы, существующие на входах П0 и СИ1, разрешают сравнение первых разрядов адресов Х команд коммутации.

В зависимости от результатов сравнения триггер 31 установится в прямое или останется в инверсном состоянии. Те узлы сравнения 30, на входы которых поступили одинаковые значения первых разрядов адресов X, устанавливают соединенные с ними триггеры 31 в прямое состояние, и сигналы, появившиеся на прямых входах этих триггеров, разрешают дальнейшее сравнение разрядов адресов Х команд коммутации на этих узлах сравнения. Каждый следующий сигнал равенства подтверждает прямое состояние триггера 31. Сигнал неравенства, выработанный узлом сравнения 30 на любом шаге сравнения, пройдя через элемент ИЛИ 29, установит триггер 31 в инверсное состояние, тем самым прекратит дальнейшее сравнение разрядов адресов Х в данном узле сравнения 30. После выдачи на сравнение всех разрядов адресов Х в соответствии с временной диаграммой снимается сигнал со входа П1 и временно снимается со входа П0. В результате в прямом состоянии останутся только те триггеры 31, на которые все время поступали только сигналы равенства с узлов сравнения 30.

Так как адреса X, поступившие на один блок 2.R., однозначно определяют линии связи С.Х.r., соединяющие этот блок с блоками 3.Х. входного каскада, можно было бы считать, что канал связи через промежуточный блок определен. Однако из-за того, что к одному блоку коммутации 3.Х. подключено р входов, возникает большая вероятность поступления из различных блоков 1.Z. на ячейки 13.Z.X. подключенных к одной линии связи С.Х.r. пар (р.х.) с равными X, но неравными Р. На первом полушаге настройки эти пары различить нельзя, т.е. все триггеры 31 ячеек 13.Z.X., получивших равные X, не зависимо от дальнейших Р будут установлены в прямое состояние. Таким образом, возникает конфликт за занятие линии связи С.Х.r. Для разрешения этого конфликта и для создания возможности поиска канала связи в блоках коммутации 3.Х. во втором полушаге настройки необходимо принять решение, какую же из выделенных на первом полушаге настройки установкой триггеров 31 в прямое состояние линий связи D.r.Z подключить к линии связи С.Х.r.

В предлагаемой коммутационной системе принято, что к незанятой линии связи С.Х.r. из всех претендующих на подключение к ней на данном шаге линий связи выбирается та, у которой значение параметра Z будет наименьшим. Этот выбор осуществляется во время подачи импульса на вход СИ2. Этот импульс поступает на вход элементов И 15.Х., на которые поступают сигналы с прямых выходов соответствующих триггеров 14.Х.

В случае если все ячейки 13.Z.X., подключенные к шине F.Z.X., остаются незанятыми, то триггер 14.Х. сохраняет положительный потенциал на прямом выходе. Если через ячейку 13.Z.X. в последующих шагах настройки будет установлен канал связи, то сигнал занятости координатной шины сбросит триггер 14.Х., так как на его вход сброса «R» будет подаваться положительный потенциал с шины F.Z.X, а на вход установки триггера в единичное состояние «S» - отрицательный потенциал через инвертор 16.Х.

На выходе G.X. элементов И 15.Х., подготовленных триггерами 14.Х., формируется импульс, который поступает на элементы И 33 и И 38 всех ячеек 13.Z.X., подключенных к соответствующей линии связи С.Х.r.

Предположим, что триггеры 31 ячеек коммутации 13.1-Х., 13.2-Х., …, 13.Z*-1.X., подключенных соответственно к линиям связи D.r.l., D.r.2., …, D.r.Z*-1., установлены в инверсное состояние, триггер 31 ячейки 13.Z*.X. установлен в прямое состояние, а триггеры 31 всех остальных ячеек 13.Z.X. (при Z>Z*), подключенных к той же линии связи С.Х.r., установлены либо в прямое, либо в инверсное состояние.

Тогда элементы запрета 33 в ячейках 13.Z.X. (Z<Z*) будут блокированы сигналами с прямых выходов триггеров 31. Элемент запрета 33 в ячейке 13.Z*.X. будет подготовлен к прохождению информации, так как на его управляющий вход поступает разрешающий сигнал с прямого выхода триггера 31. На блокирующий вход этого элемента запрета 33 сигнал не поступает, так как в ячейках 13.Z.X. (Z<Z*) сигнал F.Z.X. занятости входной шины вырабатываться не будет, т.е. их триггеры 31 находятся в инверсных состояниях в силу принятых выше предположений. Следовательно, на выходе F.Z*-1.Х узла 12.Х. ускоренного распространения сигнала занятости входной координатной шины сигнал будет отсутствовать. Таким образом, импульс, поступающий с выхода соответствующего элемента И 15.Х., пройдя через элемент запрета 33 в ячейке 13.Z*.X., перебросит в прямое состояние триггер 32. Кроме того, в этой же ячейке на элементе И 38 сформируется признак занятости входной шины. Этот признак поступит с выхода E.Z*.X ячейки 13.Z*.X на соответствующий вход узла 12.Х. и в течение одного такта распространится на все входы F.Z.X ячеек 13.Z.X. при Z>Z*, блокируя элементы запрета 33, расположенные в этих ячейках, и таким образом запретит переход в прямое состояние триггеров 32 во всех ячейках 13.Z.X. (Z>Z*) независимо от состояния их триггеров 31. Сигнал занятости, возникающий в элементе 38 любой ячейки 13.Z.X., пройдя через узел 12.Х. ускоренного распространения сигнала занятости, поступит на инверсный вход соответствующего триггера 14.Х и переведет его в инверсное состояние.

Таким образом, до тех пор пока ячейка коммутации блока коммутации промежуточного каскада будет занята, нулевое состояние на выходе триггера 14.Х. будет блокировать цепи установки триггеров 32 в прямое состояние и цепи формирования сигналов разрешения конфликтов в ячейках 13.Z.X.

В результате описанных действий, если среди ячеек 13.Z.X., подключенных к одной лини связи С.Х.r., существовало какое-то множество ячеек, триггеры 31 которых находились в прямом состоянии, то только в одной из этих ячеек 13.Z.X., триггер 32 перейдет в прямое состояние и останется в этом состоянии до конца работы. Триггер 32 подготовит элемент И 35 к прохождению информации во втором полушаге настройки.

Второй полушаг настройки начинается с момента поступления сигналов на входы П2, СИ3 и возобновления сигнала на входе П0 коммутационной системы. Повторное появление сигнала на входе П0 разрешает дальнейшую поразрядную передачу настроечной информации из буферных ОЗУ 8.М. Оставшаяся в буферных ОЗУ 8.М. настроечная информация представляет собой адреса Р команд коммутации.

Эти адреса, поступив на выходы V.z.m., проходят через элементы И 24 в ячейках 4.R.M. по линиям связи D.r.z. через элементы И 35, подготовленные сигналом с выхода П2 на линию связи С.Х.r. С линии связи С.Х.r. адреса Р поразрядно поступают на входы узлов сравнения 30 в ячейках 13.Z.X. и 43 в ячейках 17.P.R.

С другой стороны, на вторые входы узлов сравнения 30 поступают адреса по линиям связи D.r.Z. из буферных ОЗУ 8.М. различных ячеек 1.Z. На тех узлах сравнения 30, на входах которых имеется разрешающий сигнал с прямых выходов триггеров 31, поразрядное сравнение адресных кодов продолжится так же, как было описано выше.

На узлы сравнения 43 на вторые входы также будут поступать адреса Р. Но они будут поступать из элементов памяти 20.Р. под управлением сигнала со входа П2 через входы U.x.p.коммутационной системы. При этом адреса будут поступать только из тех элементов памяти 20.Р., на вход которых поступает разрешающий сигнал «0» по шине К.х.р. В противном случае, элементы 20.Р. будут находится в третьем (закрытом) состоянии. Элемент 20.Р. находится в закрытом состоянии в случае, если хотя бы через одну ячейку коммутации 17.P.R., подключенную к одной входной информационной шине U.x.p., установлен канал связи.

Сравнение первых разрядов в узлах сравнения 43 будет разрешено сигналами, появившимися на входах П2 и СИ3. Только те узлы сравнения 43, на которые подается положительный потенциал П2 через элемент И 45, будут подготовлены к сравнению адресов Р. В свою очередь, только те элементы И 45, на вторые входы которых поступил положительный потенциал с инверсных выходов триггеров 44, будут подготовлены к приему настроечного потенциала П2.

Дальнейшее сравнение в узлах сравнения 43 будет выполняться так же, как и в узлах сравнения 30. Процесс сравнения адресов Р команд коммутации закончится после прохождения последних разрядов адресов Р. После этого снимаются сигналы со входов П0 и П2 коммутационной системы.

В результате этого триггеры 31 и 44, на которые поступили только сигналы равенства из узлов сравнения 30 и 43, будут находиться в прямом состоянии.

Для фиксации найденных каналов связи в ячейках 13.Z.X. формируется сигнал фиксации. Формирование этого сигнала производится теми элементами И 37, на управляющие входы которых поданы сигналы с прямых выходов триггера 31. Импульс СИ4 проходит через такие элементы И 37 на соответствующие линии связи D.r.Z. и по ним поступает на входы элементов И 23 в ячейках 4.R.M. Через элементы И 23, на вторые входы которых подан сигнал с прямого выхода S.m.r, r-го разряда соответствующего регистра сдвига 5.М, сигнал фиксации проходит на прямые входы триггеров 21 и устанавливает последние в прямое состояние. Сигнал с инверсных выходов T.r.m. триггеров 21 снимается и таким образом через элементы И 6.r. блокируется прохождение настроечной информации через элементы И 24 во всех ячейках 4.R.M, подключенных к одной линии связи D.r.Z. Кроме того, триггеры 21, установленные в прямое состояние, через элементы И 7.М. блокируют прохождение импульса циклического сдвига СИ5 на регистры циклического сдвига 5.М.

Кроме этого триггеры 21 ячеек коммутации коммутационных блоков выходного каскада, установленные в прямое состояние, переводят буферные ОЗУ 8.М., подключенные к выходам ячеек, в третье (закрытое) состояние через координатные шины L.z.m. В данном случае, на координатную шину L.z.m поступает положительный потенциал через элемент И 28, на первый вход которого поступает сигнал с прямого выхода триггера 21, а на второй - сигнал фиксации СИ4. Таким образом, в следующем шаге настройки заблокированное буферное ОЗУ 8.М. не будет участвовать в процессе настройки.

Кроме выполненных действий, на втором полушаге настройки коммутационной системы выполняется подготовительная работа для выполнения следующего шага. Подготовка заключается в сдвиге в сторону старших разрядов содержимого, незаблокированных элементами И 7.М. регистров сдвига 5.М. Сдвиг производится подачей импульса на вход СИ5 коммутационной системы. Пусть в результате сдвига единица, записанная ранее в r*-ом разряде регистра сдвига 5.М., перейдет в (r*+1)-й разряд и соответственно сигнал с прямого выхода (r*+1)-го разряда этого регистра поступит на вход ячейки 4.r*+1.М., подключенной к линии связи D.r*-1.Z. Если к этой линии связи подключена ячейка 4.r.М. (r=r*+1), в которой триггер 21 находится в прямом состоянии, то никаких изменений в ячейках 4.r*+1.М. не произойдет. Если же среди ячеек 4.R.M., подключенных к линии связи D.r*+1.Z., не существует узла с находящимся в прямом состоянии триггером 21, то элемент И 24 ячейки 4.r*+1.М. будет подготовлен к передаче настроечной информации с выхода V.z.m. на линию связи D.r*+1.Z.

В результате выполненных действий коммутационная система готова к следующему шагу настройки, на котором проверяется возможность построения заблокированных на текущем шаге настройки каналов связи через другие блоки 13.Z.X. промежуточного каскада.

Очередной шаг настройки выполняется в основном точно так же, как и описанный первый шаг. Отличие состоит лишь в том, что к зафиксированным на предыдущих шагах каналам связи через ячейки 13.Z.X. могут подключать новые ветви, если по ранее зафиксированным каналам связи и по новым ветвям поступает одинаковая настроечная информация. При этом для ранее зафиксированных каналов настроечная информация поступает из соответствующих буферных ОЗУ 8.М. по следующему маршруту: выход V.z.m. коммутационной системы, элемент И 25 ячейки 4.R.M. с триггером 21 в прямом состоянии, линия связи D.r.Z., элемент И 35 в ячейке 13.Z.X. с триггером 32, находящимся в прямом состоянии, линии связи С.Х.r., входы соответствующих узлов сравнения 30. Настроечная информация для новых ветвей поступает по последующим маршрутам: буферные ОЗУ 8.М., выходы V.z.m. коммутационной системы, незаблокированные элементы И 24, линии связи D.r.Z., входы соответствующих узлов сравнения 30.

В дальнейшем процесс сравнения идет также, как описано ранее. Следует подчеркнуть, что состояние фиксации уже найденного канала связи в коммутационной системе подтверждается на каждом шаге настройки.

Процесс настройки коммутационной системы будет продолжаться до тех пор, пока не будут найдены каналы связи для всей подпрограммы коммутации, поступившей на информационные выходы из буферных ОЗУ на первом шаге настройки. Этот процесс контролируется ЦУУ, на которое подается потенциал с выхода элемента И 10.Z. блока коммутации выходного каскада. Входы элемента И 10.Z. соединены с прямыми выходами триггеров 9.М. В исходном состоянии системы, когда на ее управляющие входы поступает потенциал Н0, триггеры 9.М. устанавливаются в прямое состояние отрицательным потенциалом, поданным с инвертора 11.Z. на вход установки триггеров в единичное состояние «», с элемента И 10.Z. подается единичный потенциал на ЦУУ. На первом шаге настройки в момент считывания первого нулевого разряда «0» команды коммутации из буферного ОЗУ 8.М триггеры 9.М сбрасываются, тем самым на выходе элемента И 10.Z появляется нулевой потенциал, который подает сигнал на центральное управляющее устройство о начале процесса настройки. В случае если в процессе поиска на первом шаге настройки для команды коммутации, выданной на информационный выход V.Z.M, отыскивается свободный канал связи, то нулевой потенциал с выхода элемента 7.М подается на вход сброса «» триггера 9.М и устанавливает его в прямое состояние. Таким образом, пока для всех команд коммутации, выданных на информационные выходы V.z.m, не найдутся свободные каналы связи, процесс поиска каналов связи не закончится, так как на выходе элемента И 10.Z будет присутствовать нулевой потенциал.

Максимальное число шагов настройки, которое необходимо выполнить для полного процесса поиска и фиксации всех требуемых каналов связи, равно R. Это связано с тем, что для каждой пары (р.х.) существует R различных каналов связи через промежуточный каскад коммутационной системы. Для неблокирующей трехкаскадной коммутационной системы по крайней мере один из них будет незаблокированным независимо от того, в каком порядке производится поиск этих каналов.

После выполнения i шагов настройки, когда в неблокируемой трехкаскадной коммутационной системе будут зафиксированы все требуемые по подпрограмме коммутации каналы связи, на выходе элемента И 10.Z. появится единичный потенциал, дающий сигнал ЦУУ о прекращении процесса настройки каналов связи.

Фаза передачи информации начинается подачей на вход П4 соответствующего сигнала, информация проходит с входа U.X.P. через линию связи C.X.R, элемент И 36, линию связи D.R.Z., элемент И 26 на выход V.Z.M. коммутационной системы.

Сигнал разборки каналов связи поступает из ЦУУ. В режиме разборки каналов связи управляющие сигналы подаются на вход П3 коммутационной системы и на тот вход U.X.p., каналы связи от которого необходимо разобрать.

В результате этого через узел 22 разборки каналов связи будет сброшен в инверсное состояние триггер 21, через узел 34 разборки каналов связи и элемент ИЛИ 29 - триггеры 31 и 32, и через узел 41 разборки каналов связи, и элемент ИЛИ 42 - триггер 44 и, таким образом, будут разобраны соответствующие каналы связи через коммутационную систему.

Следующая фаза настройки коммутационной системы начинается по сигналу из ЦУУ. При этом накопившееся к данному моменту времени множество команд коммутации считывается параллельно из «незаблокированных» буферных ОЗУ 8.М и поступает на свободные информационные выходы системы V.z.m. При этом по уже установленным каналам связи продолжает передаваться информация, а занятые линии связи V.z.m., D.z.m. и С.х.r. блокируются для передачи настроечной информации на данном этапе настройки.

Предлагаемая трехкаскадная коммутационная система позволяет производить поиск одновременно всех M×Z каналов связи, соединяющих Р×Х входов с M×Z выходами за i шагов работы системы. Шаг работы системы состоит из количества тактов, достаточных для прохождения m+1-разрядного кода, плюс два дополнительных такта, обусловленных алгоритмом работы системы. Таким образом, поиск M×Z каналов связи в предлагаемой коммутационной системе займет (log2(P×X)+3)×i тактов.

Источники информации

1. Патент США №4417245, 1983 г.

2. Авторское свидетельство СССР №1226481, 1985 г