Микропроцессор гибридный

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может найти применение в системах обработки сигналов. Техническим результатом является расширение функциональных возможностей устройства за счет обработки сигналов и изображений при работе с вещественной арифметикой. Устройство содержит буфер инструкций, блок управления памятью, кэш-память второго уровня, целочисленное арифметико-логическое устройство (АЛУ), блок вещественной арифметики и системный контроллер. 3 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к вычислительной технике и может найти применение в системах обработки сигналов и другой информации, где необходима высокая производительность при работе с вещественной арифметикой.

Прототипом устройства может служить любой процессор с RISC архитектурой, но максимально близким является микропроцессор RM7065A фирмы PMC-Sierra, содержащий буфер инструкций, блок управления памятью, кэш-память второго уровня, целочисленное арифметико-логическое устройство (АЛУ), блок вещественной арифметики и контроллер шины (см., например. Short Form Data Sheet PMC-2011599 RM7065A 64-Bit MIPS RISC Microprocessor with Integrated L2 Cache, http://www.pmc-sierra.com).

Описанный прототип может выполнять до двух команд за такт, но не позволяет эффективно решить задачи обработки сигналов и изображения при работе с вещественной арифметикой.

Задачей изобретения является создание на основе универсального микропроцессора высокопроизводительного микропроцессора гибридного, позволяющего осуществить обработку сигналов и изображения при работе с вещественной арифметикой.

Указанная задача осуществляется микропроцессором гибридным, содержащим буфер инструкций, блок управления памятью, кэш-память второго уровня, целочисленное арифметико-логическое устройство (АЛУ), блок вещественной арифметики и контроллер, при этом буфер инструкций выполнен с возможностью предсказания переходов для компенсации потерь при выполнении команды перехода и с возможностью выставлять на выполнение до четырех инструкций в режиме обработки сигналов с аппаратным контролем возможности одновременного выполнения инструкций в режиме динамического переупорядочивания, имеет один вход и пять выходов и связан с блоком управления памятью, целочисленным АЛУ и блоком вещественной арифметики, блок управления памятью содержит кэш-память инструкций первого уровня и кэш-память данных первого уровня, десять входов и семь выходов и связан со всеми блоками микропроцессора, кэш-память второго уровня выполнена в виде внутренней памяти для сокращения потерь при обмене с внешней памятью, имеет восемь входов и шесть выходов и разделена на 16 отдельных банков памяти с дополнительными шинами, связывающими ее с блоком управления памятью, блоком вещественной арифметики и системным контроллером, выполненными с возможностью работы с банками памяти по отдельности и загрузки данными обоих сдвоенных блоков вещественной арифметики, целочисленное АЛУ выполнено с возможностью выполнения двух целочисленных команд за такт и вычисления адреса для 128-разрядной загрузки/сохранения, имеет шесть входов и два выхода и связано с буфером инструкций, блоком управления памятью и блоком вещественной арифметики, блок вещественной арифметики выполнен с возможностью выполнения двух сдвоенных операций умножения, сложения и вычитания вещественных чисел одинарной точности за такт и операций умножения и сложения чисел двойной точности, имеет семь входов и четыре выхода и связан с буфером инструкций, с блоком управления памятью, целочисленным АЛУ и кэш-памятью второго уровня, контроллер выполнен в виде встроенного системного контроллера, имеет два входа и три выхода и связан с блоком управления памятью и кэш-памятью второго уровня.

Указанная задача осуществляется также тем, что связь блока вещественной арифметики с кэш-памятью второго уровня выполнена по четырем дополнительным 128-разрядным шинам данных, а связь кэш-памяти второго уровня с системным контроллером - по двум дополнительным 64-разрядным шинам данных.

Указанная задача осуществляется также тем, что буфер инструкций содержит буфер перехода, блок управления буферами, буфер выполнения, блок выборки/декодирования команд, блок предсказания перехода, блок анализа зависимостей, счетчик команд, счетчик перехода, блок выбора потока выполнения и два мультиплексора, при этом буфер перехода выполнен с одним входом и одним выходом и связан с блоком управления памятью и через мультиплексор с буфером выполнения, блок управления буферами выполнен с четырьмя выходами и двумя входами и связан с блоком предсказания переходов, блоком выборки/декодирования команд, блоком анализа зависимостей, регистром счетчика программ, управляющим мультиплексором буфера выполнения, буфер выполнения выполнен с одним входом и одним выходом и связан с блоком выборки/декодирования команд, блок выборки/декодирования команд выполнен с двумя входами и двумя выходами и связан с буфером выполнения, блоком анализа зависимостей, блоком выбора потока выполнения, блоком управления буферами и блоком предсказания перехода, блок предсказания перехода выполнен с тремя входами и тремя выходами и связан с блоком управления буферами, блоком выборки/декодирования команд, с счетчиком команд, с счетчиком перехода и с мультиплексором, связанным с блоком управления памятью, блок анализа зависимостей выполнен с одним входом и двумя выходами и связан с блоком управления буферами, блоком выборки/декодирования команд и блоком выбора потока выполнения, счетчик команд выполнен с одним входом и одним выходом и связан с блоком управления буферами, блоком предсказания перехода и мультиплексором, связанным с блоком управления памятью, счетчик перехода выполнен с одним входом и одним выходом и связан с блоком предсказания перехода и мультиплексором, связанным с блоком управления памятью, блок выбора потока выполнения выполнен с двумя входами и четырьмя выходами и связан с блоком выборки/декодирования команд, блоком анализа зависимостей, с блоком управления памятью, целочисленным АЛУ и блоком вещественной арифметики.

Указанная задача осуществляется также тем, что кэш-память второго уровня содержит четыре входных мультиплексора, блок управления кэш-памятью второго уровня, блок регистров ПДП и векторного режима, четыре группы памятей 4×16 Кбайт и шесть выходных буферов, при этом каждый из четырех входных мультиплексоров выполнен с шестью входами и одним выходом и связан с системным контроллером, блоком управления памятью и блоком вещественной арифметики, с блоком управления кэш-памятью второго уровня и соответствующей группой памятей 4×16 Кбайт, блок управления кэш-памятью второго уровня выполнен с пятью входами и тремя выходами и связан с входными мультиплексорами, группами памятей 4×16 Кбайт, выходными буферами и блоком регистров ПДП и векторного режима, блок регистров ПДП и векторного режима выполнен с одним входом и двумя выходами и связан с блоком управления памятью, с блоком управления кэш-памятью второго уровня и выходными буферами, каждая из четырех групп памятей 4×16 Кбайт выполнена с двумя входами и одним выходом и связана с входными мультиплексорами, блоком управления кэш-памятью второго уровня и выходными буферами, шесть выходных буферов, каждый из которых выполнен с пятью входами и одним выходом и связан с системным контроллером, блоком управления памятью, с блоком вещественной арифметики, с блоком управления памятью и группами памятей 4×16 Кбайт.

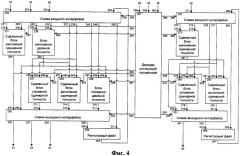

Указанная задача осуществляется также тем, что блок вещественной арифметики, содержит две несимметричные схемы входного интерфейса, декодер инструкций процессора, два сдвоенных блока умножения одинарной точности, блок умножения двойной точности, два сдвоенных блока сложения одинарной точности, два сдвоенных блока вычитания одинарной точности, блок сложения двойной точности, две несимметричные схемы выходного интерфейса, два регистровых файла, при этом две несимметричные схемы входного интерфейса, одна из которых выполнена с пятью входами и девятью выходами, а другая - с тремя входами и пятью выходами, и связаны с блоком управления памятью, целочисленным АЛУ и кэш-памятью второго уровня, с декодером инструкций микропроцессора, двумя сдвоенными блоками умножения одинарной точности, блоком умножения двойной точности, двумя сдвоенными блоками сложения одинарной точности, двумя сдвоенными блоками вычитания одинарной точности, блоком сложения двойной точности и двумя регистровыми файлами, декодер инструкций микропроцессора выполнен с тремя входами и двенадцатью выходами и связан с буфером инструкций, двумя схемами входного интерфейса, двумя сдвоенными блоками умножения одинарной точности, блоком умножения двойной точности, двумя сдвоенными блоками сложения одинарной точности, двумя сдвоенными блоками вычитания одинарной точности, блоком сложения двойной точности и двумя схемами выходного интерфейса, два сдвоенных блока умножения одинарной точности, каждый из которых выполнен с тремя входами и одним выходом и связан со схемами входного интерфейса, декодером инструкций микропроцессора, схемами выходного интерфейса со сдвоенным блоком сложения одинарной точности, со сдвоенным блоком вычитания одинарной точности, блок умножения двойной точности выполнен с тремя входами и одним выходом и связан со схемами входного интерфейса, декодером инструкций микропроцессора, схемами выходного интерфейса и с блоком сложения двойной точности, два сдвоенных блока сложения одинарной точности, каждый из которых выполнен с четырьмя входами и одним выходом и связан со схемами входного интерфейса, декодером инструкций микропроцессора, схемами выходного интерфейса, со сдвоенными блоками умножения одинарной точности, два сдвоенных блока вычитания одинарной точности, каждый из которых выполнен с четырьмя входами и одним выходом и связан со схемами входного интерфейса, декодером инструкций микропроцессора, схемами выходного интерфейса, со сдвоенными блоками умножения одинарной точности, блок сложения двойной точности выполнен с четырьмя входами и одним выходом и связан со схемами входного интерфейса, декодером инструкций процессора, схемами выходного интерфейса, с блоком умножения двойной точности, две несимметричные схемы выходного интерфейса, одна из которых выполнена с шестью входами и четырьмя выходами, а другая - с четырьмя входами и двумя выходами и связаны соответственно с блоком управления памятью, целочисленным АЛУ и кэш-памятью второго уровня, с декодером инструкций микропроцессора, двумя сдвоенными блоками умножения одинарной точности, блоком умножения двойной точности, двумя сдвоенными блоками сложения одинарной точности, двумя сдвоенными блоками вычитания одинарной точности, блоком сложения двойной точности и двумя регистровыми файлами, два регистровых файла, каждый из которых выполнен с двумя входами и одним выходом и связан со схемами входного интерфейса и схемами выходного интерфейса.

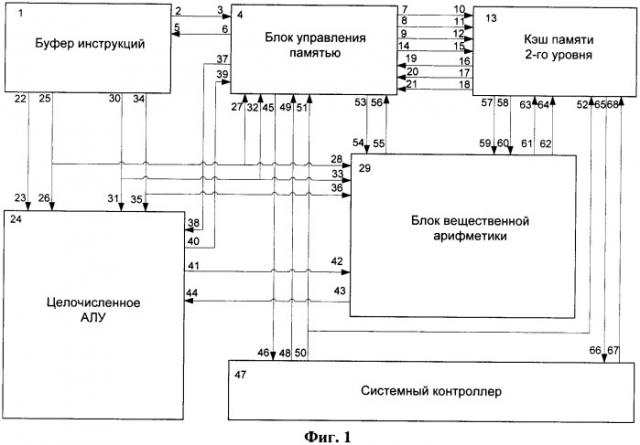

На фиг.1 представлена блок-схема микропроцессора гибридного.

На фиг.2 - блок-схема буфера инструкций.

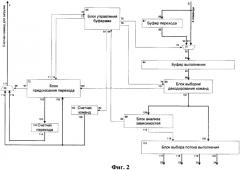

На фиг.3 - блок-схема кэш-памяти второго уровня.

На фиг.4 - блок-схема блока вещественной арифметики.

Микропроцессор гибридный (фиг.1) состоит из буфера инструкций 1, выход 2 которого - линии запроса и адреса - связан с входом 3 блока управления памятью 4, вход 5 - входные инструкции - связан с выходом 6 блока управления памятью 4. Выходы 7, 8 и 9 блока управления памятью 4 - запросы и адреса данных, инструкций и операций сохранения - связаны с входами 10, 11 и 12 кэш-памяти второго уровня 13. Выход 14 блока управления памятью 4 - данные сохранения - связан с входом 15 кэш-памяти второго уровня 13, а выходы 16, 17 - данные загрузки кэш-памяти инструкций и данных первого уровня и 18 - выходные данные в режиме внутренней памяти - кэш-памяти второго уровня 13 связаны с входами 19, 20 и 21 блока управления памятью 4. Выход 22 буфера инструкций 1 - целочисленная инструкция - связан с входом 23 целочисленного АЛУ 24, выход 25 - целочисленная инструкция или инструкция загрузки/сохранения - связан с входом 26 целочисленного АЛУ 24, входом 27 блока управления памятью 4 и входом 28 блока вещественной арифметики 29, выход 30 буфера инструкций 1 - инструкция расширенной загрузки/сохранения - связан с входом 31 целочисленного АЛУ 24, входом 32 блока управления памятью 4 и входом 33 блока вещественной арифметики 29, выход 34 буфера инструкций 1 - инструкция вещественной арифметики или инструкция расширенной вещественной арифметики - связан с входом 35 целочисленного АЛУ 24 и входом 36 блока вещественной арифметики 29. Выход 37 блока управления памятью 4 связан с входом 38 целочисленного АЛУ 24, а выход 39 целочисленного АЛУ 24 связан с входом 40 блока управления памятью 4 - линии взаимодействия целочисленного АЛУ и блока управления памятью. Выход 41 целочисленного АЛУ 24 связан с входом 42 блока вещественной арифметики 29, а выход 43 блока вещественной арифметики 29 связан с входом 44 целочисленного АЛУ 24 - линии обмена данными целочисленного АЛУ и блока вещественной арифметики. Выход 45 блока управления памятью 4 - выходные данные - связан с входом 46 системного контроллера 47, выход 48 системного контроллера 47 - линии контроля когерентности - связан с входом 49 блока управления памятью 4, выход 50 системного контроллера 47 - входные данные - связан с входом 51 управления памятью 4 и входом 52 кэш-памяти второго уровня 13. Выход 53 блока управления памятью 4 связан с входом 54 блока вещественной арифметики 29, а выход 55 блока вещественной арифметики 29 связан с входом 56 блока управления памятью 4 - линии обмена данными блока управления памятью и блока вещественной арифметики. Выходы 57 и 58 кэш-памяти второго уровня 13 связаны с входами 59 и 60 блока вещественной арифметики 29, а выходы 61 и 62 блока вещественной арифметики 29 связаны с входами 63 и 64 кэш-памяти второго уровня 13 - дополнительные 128-разрядные шины данных. Выход 65 кэш-памяти второго уровня 13 связан с входом 66 системного контроллера 47, а выход 67 системного контроллера 47 связан с входом 68 кэш-памяти второго уровня 13 - канал прямого доступа к памяти.

В качестве блока управления памятью 4 может использоваться любой блок управления памятью микропроцессора с RISC архитектурой, содержащий кэш-память данных и инструкций первого уровня, например блок управления памятью MIPS подобного микропроцессора типа прототипа или любого другого, или SPARC V8 подобного процессора. В качестве целочисленного АЛУ 24 может использоваться любое целочисленного АЛУ микропроцессора с RISC архитектурой, позволяющее выполнять две целочисленные команды за такт, обработку адреса и пересылку. В качестве системного контроллера может использоваться любой из существующих системных контроллеров, позволяющий подключать дополнительные каналы данных и имеющий совместимую локальную шину с используемым блоком управления памяти.

Буфер инструкций 1 состоит из блока управления буферами 69, вход 70 которого связан с выходом 71 блока предсказания перехода 72, выход 73 - с входом 74 блока предсказания перехода 72, выход 75 - с управляющим входом 76 мультиплексора 77, выход 81 - с входом 82 счетчика команд 83, вход 84 - с выходом 85 блока анализа зависимостей 86; буфера перехода 87, вход 88 которого связан с входом 2 буфера инструкций 1, выход 89 - с входом 90 мультиплексора 77; мультиплексора 77, вход управления 76 которого связан с выходом 75 блока управления буферами 69, вход 90 - с выходом 89 буфера перехода 87, вход 91 - с входом 2 буфера инструкций 11, выход 92 - с входом 93 буфера выполнения 94; буфера выполнения 94, вход 93 которого связан с выходом 92 мультиплексора 77, выход 95 - с входом 96 блока выборки/декодирования 80; блока предсказания перехода 72, выход 71 которого связан с входом 70 блока управления буферами 69, вход 74 - с выходом 73 блока управления буферами 69, выход 97 - с управляющим входом 98 мультиплексора 99, выход 102 - с входом 103 счетчика перехода 104, вход 105 - с выходом 106 счетчика команд 83, вход 100 - с выходом 101 блока выборки/декодирования 80; блока выборки/декодирования 80, вход 96 которого связан с выходом 95 буфера выполнения 94, вход 79 - с выходом 78 блока управления буферами 69, выход 101 с входом 100 блока предсказания перехода 72, выход 107 - с входами 108 блока анализа зависимостей 86 и 109 блока выбора потока выполнения 110; мультиплексора 99, вход управления 98 которого связан с выходом 97 блока предсказания перехода 72, выход 111 - с выходом 5 буфера инструкций 1, вход 112 - с выходом 106 счетчика команд 83, вход 113 - с выходом 114 счетчика перехода 104; счетчика команд 83, вход 82 которого связан с выходом 81 блока управления буферами 69, выход 106 - с входом 112 мультиплексора 99; блока анализа зависимостей 86, выход 85 которого связан с входом 84 блока управления буферами 69, вход 108 - с выходом 107 блока выборки/декодирования 80, выход 115 - с входом 116 блока выбора потока выполнения 110; блока выбора потока выполнения 110, выход 116 которого связан с выходом 115 блока анализа зависимостей 86, вход 109 - с выходом 107 блока выборки/декодирования 80, выход 117 - с выходом 22 буфера инструкций 1, выход 118 - с выходом 25 буфера инструкций 1, выход 119 - с выходом 30 буфера инструкций 1, выход 120 - с выходом 34 буфера инструкций 1.

В качестве блока управления буферами 69 может быть использован блок управления буферами типа FIFO (first input first output, очередь). Буфер перехода 87 и буфер выполнения 94 - регистры для хранения 4-х 32-разрядных инструкций. Блок предсказания перехода 72 - стандартный блок предсказания переходов RISC процессора с предсказанием перехода, управляющий выставлением запроса на шину адреса и формирующий сигналы о выставлении предсказанного запроса и подтверждения или отмены предсказанного перехода. Блок выборки/декодирования 80 - стандартный блок декодирования инструкций микропроцессора с RISC архитектурой (например, блок декодирования MIPS подобного микропроцессора типа прототипа или любого другого), декодирующий полученные команды. Счетчик команд перехода 104 - регистр, хранящий значение целевого адреса перехода предсказанного перехода. Счетчик команд 83 - регистр, хранящий текущее значение счетчика команд. Блок анализа зависимостей 86 - стандартный блок анализа зависимостей, выбранных для выполнения инструкций микропроцессора с RISC архитектурой, выполняющего 2 команды за такт (например, блок декодирования микропроцессора типа прототипа или любого другого). Блок выбора потока выполнения 110 - стандартный блок микропроцессора с RISC архитектурой с 4-мя потоками выполнения (например, блок выдачи инструкций микропроцессора типа прототипа), распределяющий выбранные и декодированные инструкции по потокам выполнения.

Кэш-память второго уровня 13 состоит из четырех входных мультиплексоров 121, 122, 123 и 124; четырех групп памятей 125, 126, 127 и 128 емкостью 4×16 килобайт каждая; шести выходных буферов 129, 130, 131, 132, 133 и 134; блока регистров 135, хранящих параметры работы блока кэш-памяти второго уровня в режимах векторном и прямого доступа к памяти (ПДП); блока управления кэш-памятью второго уровня 136.

Вход 52 блока 13 - входные данные - связан с входами 137, 138, 139 и 140 входных мультиплексоров 121, 122, 123 и 124 соответственно; вход 68 блока 13 - входные данные - связан с входами 141, 142, 142 и 144 входных мультиплексоров 121, 122, 123 и 124 соответственно; вход 15 блока 13 - входные данные - связан с входами 145, 146, 147 и 148 входных мультиплексоров 121, 122, 123 и 124 соответственно; вход 63 блока 13 - входные данные - связан с входами 149, 150, 151 и 152 входных мультиплексоров 121, 122, 123 и 124 соответственно; вход 64 блока 13 - входные данные - связан с входами 153, 154, 155 и 156 входных мультиплексоров 121, 122, 123 и 124 соответственно.

Вход 10 блока 13 - линии адреса - связан с входом 157 блока управления кэш-памятью второго уровня 136; вход 11 блока 13 - линии адреса - связан с входом 158 блока управления кэш-памятью второго уровня 136; вход 12 блока 13 - линии адреса - связан с входом 159 блока управления кэш-памятью второго уровня 136.

Выход 160 входного мультиплексора 121 связан линией данных с входом 161 группы памятей 125. Выход 162 входного мультиплексора 122 связан линией данных с входом 163 группы памятей 126. Выход 164 входного мультиплексора 123 связан линией данных с входом 165 группы памятей 127. Выход 166 входного мультиплексора 124 связан линией данных с входом 167 группы памятей 128.

Выход 168 блока управления кэш-памятью второго уровня 136 связан с управляющими входами 169, 170, 171 и 172 входных мультиплексоров 121, 122, 123 и 124 соответственно. Выход 173 связан с входами адреса и управляющих сигналов 174, 175, 176 и 177 групп памятей 125, 126, 127 и 128 соответственно. Выход 178 группы памятей 125 связан линией данных с входами 179, 180, 181, 182, 183 и 184 выходных буферов 129, 130, 131, 132, 133 и 134 соответственно. Выход 185 группы памятей 126 связан линией данных с входами 186, 187, 188, 189, 190 и 191 выходных буферов 129, 130, 131, 132, 133 и 134 соответственно. Выход 192 группы памятей 127 связан линией данных с входами 193, 194, 195, 196, 197 и 198 выходных буферов 129, 130, 131, 132, 133 и 134 соответственно. Выход 199 группы памятей 128 связан линией данных с входами 200, 201, 202, 203, 204 и 205 выходных буферов 129, 130, 131, 132, 133 и 134 соответственно. Выход 206 блока управления кэш-памятью второго уровня 136 связан с управляющими входами 207, 208, 209, 210, 211 и 212 выходных буферов 129, 130, 131, 132, 133 и 134 соответственно.

Выход 213 выходного буфера 129 - линия данных - связан с выходом 65 блока 13; выход 214 выходного буфера 130 - линия данных - связан с выходом 18 блока 13; выход 215 выходного буфера 131 - линия данных - связан с выходом 16 блока 13; выход 216 выходного буфера 132 - линия данных - связан с выходом 17 блока 13; выход 217 выходного буфера 133 - линия данных - связан с выходом 57 блока 13; выход 218 выходного буфера 134 - линия данных - связан с выходом 58 блока 13.

Выход 219 блока регистров 135 связан линией данных с входом 220 блока управления кэш-памятью второго уровня 136. Выход 221 блока регистров 135 связан линией данных с входом 222 блока управления кэш-памятью второго уровня 136.

Блоки 121, 122, 123 и 124 представляют собой стандартные 128-разрядные мультиплексоры 4 в 1. Блоки 125, 126, 127 и 128 представляют собой стандартные 128-разрядные блоки памяти. Блоки 129, 130, 131, 132, 133 и 134 представляют собой стандартные 128-разрядные мультиплексоры 4 в 1, объединенные с выходными буферами. Блок 135 представляет собой набор регистров. Блок 136 представляет собой стандартный контроллер ЗУ, формирующий адресные сигналы, сигналы разрешения работы входных мультиплексоров и выходных буферов.

Блок вещественной арифметики 29 состоит из блоков, описанных ниже. Данные от внешних устройств поступают на входы 223, 224 и 225 схемы входного интерфейса 226 с входов 42, 54 и 59 блока 29 соответственно. Данные с выходов 227 и 228 блока 226 поступают на входы операндов 229 и 230 сдвоенного блока умножения одинарной точности 231. Данные с выходов 232 и 233 поступают соответственно на входы операндов 234 и 235 блока умножения двойной точности 236. Данные с выходов 237 и 238 блока 226 поступают соответственно на входы операндов 239 и 240 сдвоенного блока сложения одинарной точности, а также соответственно на входы операндов 242 и 243 сдвоенного блока вычитания одинарной точности 244. Данные с выходов 245 и 246 блока 226 поступают на входы операндов 247 и 248 блока сложения двойной точности 249 соответственно. С выхода 250 блока 226 данные поступают на вход 251 регистрового файла 252, с выхода 253 которого данные приходят на вход 254 блока 226. На вход 255 блока 226 поступает набор управляющих сигналов с выхода 256 декодера инструкций процессора 257. На входы 258, 259 и 260 блока 257 поступают инструкции процессора с входов 28, 33 и 36 блока 29. Наборы сигналов управления поступают на вход 261 блока 231 с выхода 262 блока 257 и на вход 263 блока 237 с выхода 264 блока 257. С выхода 265 блока 257 управляющие сигналы поступают на вход 266 схемы входного интерфейса 267, а с выхода 268 блока 257 - на вход 269 сдвоенного блока умножения одинарной точности 270. На вход 271 блока 270 с выхода 53 блока 54 поступают данные от внешних устройств. С выходов 272 и 273 операнды поступают на входы 274 и 275 блока 270 соответственно. Операнды с выходов 276 и 277 блока 267 соответственно поступают на входы 278 и 279 сдвоенного блока сложения одинарной точности 280, а также на входы 281 и 282 сдвоенного блока вычитания одинарной точности. С выхода 284 блока 267 данные поступают на вход 285 регистрового файла 286, с выхода 287 которого данные приходят на вход 288 блока 267. С выхода 289 блока 231 двойной результат умножения одинарной точности подается на вход 290 блока 241, вход 291 блока 244 и на вход 292 схемы выходного интерфейса 293. С выхода 294 блока 236 результат умножения двойной точности подается на вход 295 блока 249 и на вход 296 блока 293. С выхода 297 блока 270 двойной результат умножения одинарной точности подается на вход 298 блока 280, на вход 299 блока 283 и на вход 300 схемы входного интерфейса 301. Управляющие сигналы для блока 241 поступают на его вход 302 с выхода 303 блока 257. Управляющие сигналы для блока 244 поступают на его вход 304 с выхода 305 блока 257. Управляющие сигналы для блока 249 поступают на его вход 306 с выхода 307 блока 257. С выхода 308 блока 257 управляющие сигналы подаются на вход 309 блока 283, а с выхода 310 блока 257 - на вход 311 блока 280. С выхода 312 блока 241 двойной результат сложения одинарной точности поступает на вход 313 блока 293. С выхода 314 блока 244 двойной результат вычитания одинарной точности поступает на вход 315 блока 293. С выхода 316 блока 249 результат сложения двойной точности поступает на вход 317 блока 293. С выхода 318 блока 280 двойной результат сложения одинарной точности поступает на вход 319 блока 301. С выхода 320 блока 283 двойной результат вычитания одинарной точности поступает на вход 321 блока 301. Сигналы управления поступают на вход 322 блока 293 с выхода 323 блока 257. С выхода 324 блока 257 сигналы управления поступают на вход 325 блока 301. Данные с выходов 326, 325 и 328 блока 293 подаются на входы внешних блоков соответственно через выходы 55, 43 и 61 блока 29. С выхода 329 блока 293 данные поступают на вход 330 блока 252. С выхода 331 блока 301 данные поступают на входы внешних блоков через выход 62 блока 29. С выхода 332 данные поступают на вход 333 блока 286.

Блоки 226, 267, 293 и 301 состоят из стандартных 64-разрядных мультиплексоров. Блоки 231 и 270 состоят из двух стандартных 32-разрядных устройств умножения вещественных чисел одинарной точности. Блок 236 является стандартным 64-разрядным устройством умножения вещественных чисел двойной точности. Каждый из блоков 241, 244, 280 и 283 состоит из двух стандартных 32-разрядных устройств суммирования вещественных чисел одинарной точности. Блок 249 является стандартным 64-разрядным устройством суммирования вещественных чисел двойной точности. Архитектура блоков 231, 236, 241, 244, 249, 270, 280, 283 отвечает требованиям стандарта IEEE-754. Блок 257 является стандартной комбинационной схемой декодирования инструкций процессора. Регистровые файлы 252 и 286 выполнены на основе стандартной многопортовой памяти.

Буфер инструкций 1 контролирует запрос инструкций, обеспечивает их временное хранение во внутренних буферах, выставляет команды на выполнение и обрабатывает команды переходов. Буфер инструкций 1 выставляет запрос с адресом блоку управления памятью 4 по линиям связи (выход 2 - вход 3). Блок управления памятью 4 является связующим звеном между блоками 1, 13, 24 и 47, получив запрос от блока 1, он проверяет наличие инструкций в собственной кэш-памяти инструкций первого уровня, при отсутствии обращается в кэш-память второго уровня 13, а при отсутствии их и там - в системный контроллер 47. Инструкции из системного контроллера 47 по линии связи (выход 50 - вход 51 и 52) поступают в кэш-память второго уровня 13 и блок управления памятью 4, откуда затем в буфер инструкций 1. Буфер инструкций 1, проанализировав полученные инструкции на возможность одновременного выполнения, выставляет их по одной, парами или четверками в целочисленное АЛУ 24 по линиям связи (выход 22 - вход 23), в целочисленное АЛУ 24, блок управления памятью 4 и блок вещественной арифметики 29 по линиям связи (выход 25 - входы 26, 27 и 28), (выходы 30 - вход 31, 32 и 33), в целочисленное АЛУ 24 и блок вещественной арифметики 29 по линиям связи и (выход 34 - входы 35 и 36). Целочисленное АЛУ выполняет одновременно либо две целочисленные инструкции, либо целочисленную инструкцию и вычисляет адрес для целочисленной или вещественной загрузки/сохранения, одновременно с этим вычисляется адрес для 128-разрядной загрузки/сохранения команд обработки сигналов. Вычисленные адреса по линиям (выход 40 - вход 39) поступают в блок 4. Служебная информация или данные при выполнении команды передачи данных передаются по линиям (выход 41 - вход 42) в блок 29. Блок вещественной арифметики 29, предназначенный для выполнения арифметических операций над числами с плавающей запятой, содержит выделенные блоки одинарной точности, дополненные командами обработки сигналов. Блок вещественной арифметики 29 выполняет до двух инструкций - арифметическую и загрузки/сохранения - за такт, получая их по линиям: (выход 34 - вход 36) арифметическую инструкцию, (выход 25 - вход 28) инструкцию вещественную загрузки/сохранения и (выход 30 - вход 33) инструкцию 128-разрядной загрузки/сохранения команд обработки сигналов. Блок вещественной арифметики 29 связан 64-разрядными шинами данных, используемыми для обычных загрузки/сохранения, с блоком управления памятью 4, линии связи (выход 53 - вход 54) используются для передачи данных в блок управления памятью 4, а по линиям (выход 55 - вход 56) данные поступают в блок вещественной арифметики 29. Четыре 128-разрядные шины данных (выход 57 - вход 59), (выход 58 - вход 60), (выход 61 - вход 63) и (выход 62 - вход 64) связывают блок вещественной арифметики 29 с кэш-памятью второго уровня 13. Кэш-память второго уровня 13 используется как кэш-память в обычном режиме или как внутренняя память данных в режиме обработки сигналов. Кэш-память второго уровня 13 разделена на 16 отдельных банков памяти, объединенных в четыре группы памятей, которые могут работать независимо. По линиям связи (выход 7 - вход 10), (выход 8 - вход 11) и (выход 9 - вход 12) в кэш-память второго уровня 13 поступают адреса и запросы из блока управления памятью 4 на данные, инструкции и отображенную память. По линии связи (выход 14 - вход 15) поступают данные для сохранения. По линиям связи (выход 16 - вход 19), (выход 17 - вход 20) и (выход 18 - вход 21) в блок управления памятью 4 из кэш-памяти второго уровня 13 поступают данные. Блок управления памятью 4 связан линиями (выход 48 - вход 49) с системным контроллером 47, по которым может выполняться контроль когерентности подсистемы памяти. Данные из блока управления памятью 4 в системный контроллер 47 передаются по линиям (выход 45 - вход 46), а данные из системного контроллера 47 поступают одновременно в блок управления памятью 4 и кэш-память второго уровня (выход 50 - входы 51, 52). Кэш-память второго уровня связана дополнительными шинами, по которым осуществляется прямой доступ к памяти без загрузки процессора, с системным контроллером 47 по линиям (выход 65 - вход 66), (выход 67 - вход 68).

Наличие байтовых стробов записи во всех кэш-памятях и механизма обратной записи в кэш-памяти второго уровня позволяет отказаться от сбора данных при невыровненных операциях загрузок/сохранений без потери производительности. При некэшируемых операциях внутренняя шина не поддерживает невыровненные операции, но наличие встроенного контроллера памяти снижает потери сбора данных.

Буфер инструкций 1 выставляет запрос на выход 2 с выхода 111 мультиплексора выбора адреса 99. Мультиплексор 99 управляется блоком предсказания перехода 72 (сигналом выбора адреса с выхода 97 на вход 98): выбирается или адрес следующего по порядку запроса с линии 106-112, хранящегося в счетчике команд 83, или целевой адрес перехода с линии 114-113, хранящийся в счетчике перехода 104. Значение счетчика перехода 104 записывается из блока предсказания ветвления 72 по линии 102-103. Для расчета целевого адреса перехода в качестве базового адреса берется адрес следующего запроса (значение счетчика команд 83, получаемое по линии 106-105). Решения по предсказанию принимаются на основе информации, получаемой от блока управления буферами 69 по линии 73-74 и от блока выборки/декодирования команд 80 по линии 101-100. Сам блок предсказания перехода 72, помимо управления мультиплексором выбора адреса 99, по линии 71-70 выдает информацию о выставлении запроса по предсказанному адресу блоку управления буферами 69.

Запрошенные инструкции выставляются кэш-памятью инструкций на вход 5 буфера инструкций 11. Далее, по линии 88 полученные инструкции записываются в буфер перехода 87, в котором инструкции хранятся до принятия решения о переписывании их в буфер выполнения 94. Основным буфером для работы является буфер выполнения 94, инструкции в который записываются через мультиплексор 77 по линии 92-93. Мультиплексор 77 управляется сигналом управления 75-76 от блока управления буферами 69 и выбирает для записи в буфер выполнения 94 или полученные инструкции с линии 5-91, или инструкции, предварительно записанные в буфер перехода 87, по линии 89-90.

Из буфера выполнения 94 по линии 95-96 инструкции выбираются (вычитываются) парами в блок выборки/декодирования команд 80. Количество инструкций, необходимых для чтения (читать 1 или 2 команды), определяется управляющими сигналами 78-79. В блоке выборки/декодирования команд 80 происходит предварительное декодирование типов инструкций, и на основе этого по линии 101-100 в блок предсказания перехода 72 выставляется информация о декодировании инструкции перехода, на основании которой рассчитывается целевой адрес перехода, помещаемый по линии 102-103 в счетчик перехода 104.

Из блока выборки/декодирования команд 80 инструкции передаются: по линии 107-108 в блок анализа зависимостей 86, который определяет возможность их выполнения в текущий момент времени; по линии 107-109 в блок выбора потока выполнения 110. Блок анализа зависимостей 86 формирует информацию о количестве инструкций, которые могут быть выполнены. Эта информация по линии 115-116 передается в блок управления буферами 69, который, основываясь на этой информации, по линии 81-82 управляет увеличением счетчика счетчиком команд 83 для запроса инструкций. Информация о зависимости выбранных в данный момент инструкций из блока анализа зависимостей 86 по линии 115-116 передается в блок выбора потока выполнения 110, который распределяет две полученный по линии 107-109 из блока выборки/декодирования команд 80 инструкции по 4-м потокам выполнения. В зависимости от типа инструкции, определяемого при ее декодировании в блоке выборки/декодирования команд 80, инструкция направляется на один из выходов блока выбора потока выполнения 110. На выход 117 (на линии 117-22) выставляются инструкции целочисленной арифметики, которые должны выполняться в блоке целочисленного АЛУ 24 (передаются по линии 22-23); на выход 118 (на линию 118-25) выставляются инструкции обмена с памятью, которые должны выполняться в блоке целочисленного АЛУ 24 (передаются по линии 25-26), в блоке управления памятью 4 (передаются по линии 25-27) и в блоке вещественной арифметики 29 (передаются по линии 25-28); на выход 119 (на линию 119-30) выставляются инструкции двойного блока вещественной арифметики 29, которые должны выполняться в блоке целочисленного АЛУ 24 (передаются по линии 30-31), в блоке управления памятью 4 (передаются по линии 30-32) и в блоке вещественной арифметики 29 (передаются по линии 30-33); на выход 120 (на линию 120-34) выставляются инструкции вещественной арифметики или обмена данными между целочисленным АЛУ 24 и блоком вещественной арифметики 29, которые выполняться в блоке вещественной арифметики 29 (передаются по линии 34-36) и в целочисленном АЛУ 24 (передаются по линии 34-35).

Данные на входы блока кэш-памяти второго уровня 13 поступают от следующих блоков: от системного контроллера 47 данные для заполнения строки кэш-памяти поступают на вход 52; от системного контроллера 47 данные в режиме прямого доступа к памяти поступают на вход 68; от блока управления памятью 4 при выполнении команды сохранения данные поступают на вход 15; от блока вещественной арифметики 29 при выполнении команды сохранения в векторном режиме данные поступают на вход 63; от блока вещественной арифметики 29 при выполнении команды сохранения в режиме цифровой обработки сигналов данные поступают на вход 64.

Адрес на входы блока кэш-памяти второго уровня 13 поступает от следующих блоков: адрес команды загрузки/сохранения поступает из блока управления памятью 4 на вход 10; адрес команды, запрошенной буфером инструкций 1, поступает из блока управления памятью 4 на вход 11; адрес команды загрузки/сохранения режима цифровой обработки сигналов поступает из блока управления памятью 4 на вход 12.

Данные с выходов блока кэш-памяти второго уровня 13 поступают в следующие блоки: в системный контроллер 47 в режиме прямого доступа к памяти данные поступают с выхода 65; в блок управления памятью 4 при выполнении команды загрузки данные поступают с выхода 18; в блок управления памятью 4 для заполнения строки кэш-памяти инструкций первого уровня данные поступают с выхода 16; в блок управления памятью 4 для заполнения строки кэш-памяти данных первого уровня данные поступают с выхода 17; в блок вещественной арифметики 29 при выполнении команды загрузки в векторном режиме данные по