Цифроаналоговый преобразователь

Иллюстрации

Показать всеЦифроаналоговый преобразователь, содержащий несколько источников тока и такое же число дифференциальных усилителей, каждый из которых соединен с одним источником тока и выполнен с возможностью питания от данного источника тока, причем выходы дифференциальных усилителей соединены, отличающийся тем, что токи I0 источников тока находятся в троичном соотношении между собой, а входами дифференциальных усилителей управляют таким образом, что ток каждого выхода усилителя принимает значения 0, I0, I0/2. Технический результат - повышение быстродействия. 4 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к области электроники, а именно к цифроаналоговым преобразователям, применяемым, в частности, в формирователях сигналов со сложным спектром.

В общем случае, преобразование дискретных цифровых сигналов в аналоговую форму производят путем коммутации калиброваных источников напряжения, тока, заряда и т.п. Применяют также методы временного управления, когда средняя за большой промежуток времени величина зависит от соотношения длительностей включенного и выключенного состояния соответствующего источника напряжения, соотношение же длительностей задают счетчиком числа тактов. Схемотехника различных типов цифроаналоговых преобразователей (ЦАП) рассмотрена, например, в книге "CMOS Mixed-signal Circuit Design" Volume II / R.Jacob Baker, IEEE Press [1]. Основными показателями качества для ЦАП являются точность, быстродействие и удобство реализации в интегральном исполнении.

С повышением быстродействия вычислительных машин и других цифровых устройств проблема повышения быстродействия ЦАП выдвигается на передний план. При этом быстродействие ЦАП, в первую очередь, определяется быстродействием переключающих устройств, в качестве которых в настоящее время используют биполярные или MOS транзисторы. Кроме того, при практической реализации высокоскоростных переключающих устройств необходимо учитывать влияние паразитных реактивностей соединительных проводников даже при реализации устройства в виде интегральной микросхемы.

Наибольшее быстродействие в настоящее время достигнуто в переключающих устройствах, выполненных на базе дифференциального усилителя. Они применены, например, в быстродействующем ЦАП, описанном в статье Anne Van den Bosch, Marc A. F. Borremans, Michel S. J. Steyaert and Willy Sansen, "A 10-bit 1-GSample/s Nyquist Current-Steering CMOS D/A Converter", IEEE J. Solid-State Circuits, vol. 36, no. 3, March 2001, pp.315-324 [2]. Здесь дифференциальные усилители используют как переключатели, подключающие источники тока к общей нагрузке, т.е. все переключатели соединены параллельно.

Недостаток данного аналога состоит в том, что параллельное соединение N секций усилителей порождает избыточные паразитные емкости соединительных проводников, тем большие, чем больше секций содержит ЦАП, и соответственно усложняется сеть соединительных проводников.

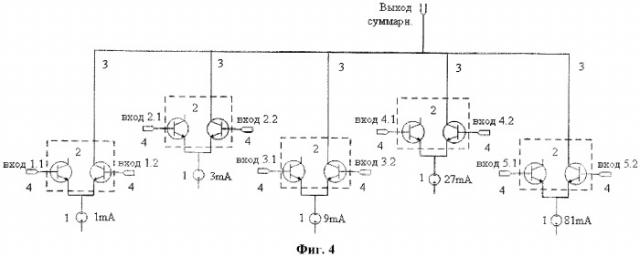

В некоторых схемах ЦАП используют способность дифференциального усилителя осуществлять деление пополам тока I0, поступающего от внешнего источника, в том случае, если управляющие входы диференциального усилителя находятся в одинаковом положении. Такая схема применена в ЦАП, выполненном согласно патенту US 3474440 [3], который является наиболее близким к заявленному изобретению и выбран в качестве прототипа. В схеме ЦАП прототипа имеется только один источник тока, и двоичное деление этого тока осуществляют цепочкой дифференциальных усилителей, включенных последовательно (Фиг.1). Такое построение требует одного источника тока и N дифференциальных усилителей, где N - разрядность ЦАП. Схема ЦАП прототипа также содержит диоды и операционные усилители для суммирования токов и преобразования суммарного тока в выходное напряжение.

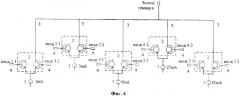

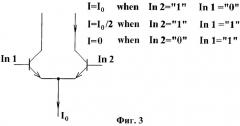

Принцип последовательного включения, применяемый в ЦАП прототипа, трудно использовать в современных интегральных схемах в связи с тем, что требуемое питающее напряжение в схеме с последовательным подключением оказывается примерно в N раз выше, чем для остальной части ЦАП. Недостатком ЦАП прототипа является также и то, что в нем дифференциальные усилители используют для формирования только двух уровней выходного тока (I0 и I0/2 либо 0 и I0) (Фиг.2), поэтому для обеспечения высокой точности преобразования требуется большое количество дифференциальных усилителей и соответственно большое количество соединяющих их проводников, что усложняет, удорожает и уменьшает быстродействие ЦАП.

Задачей заявленного изобретения является создание цифроаналогового преобразователя с упрощенной конструкцией, уменьшенной стоимостью изготовления и повышенным быстродействием при сохранении точности преобразования, например, за счет уменьшения числа переключающих каскадов (дифференциальных усилителей) и соответственно уменьшения паразитных емкостей проводников, которые соединяют эти каскады, что достигают путем использования троичной логики управления каскадом. В заявленном изобретении в каждом переключающем каскаде, выполненном в виде дифференциального усилителя, формируют три уровня выходного тока 0, I0, I0/2.

Поставленная задача решена путем создания цифроаналогового преобразователя, содержащего несколько источников тока и такое же число дифференциальных усилителей, каждый из которых соединен с одним источником тока и выполнен с возможностью питания от данного источника тока, причем выходы дифференциальных усилителей соединены. Основное отличие заявляемого решения от прототипа состоит в том, что токи I0 источников тока находятся в троичном соотношении между собой, а входами дифференциальных усилителей управляют таким образом, что ток каждого выхода усилителя принимает значения 0, I0, I0/2.

В одном из реализованных вариантов заявляемого цифроаналогового преобразователя дифференциальные усилители были выполнены на основе транзисторов, выбранных из группы, которая содержала биполярные транзисторы, полевые (КМОП) транзисторы и транзисторы других типов.

В одном из реализованных вариантов заявляемого цифроаналогового преобразователя выходы дифференциальных усилителей были соединены параллельно.

В одном из реализованных вариантов заявляемого цифроаналогового преобразователя выходы дифференциальных усилителей были соединены последовательно, при этом выходы части дифференциальных усилителей являлись источниками тока для остальных дифференциальных усилителей.

В одном из реализованных вариантов заявляемого цифроаналогового преобразователя токи I0 источников тока находились в троичном соотношении между собой, а именно в соотношении 1:3:9:27:81…

Техническим результатом заявленного изобретения является упрощение конструкции, уменьшение стоимости изготовления и повышение быстродействия цифроаналогового преобразователя при сохранении точности преобразования.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими чертежами.

Фиг.1 Упрощенная схема ЦАП с последовательным подключением дифференциальных усилителей, выполненная согласно прототипу заявляемого изобретения.

Фиг.2 Схема работы дифференциального усилителя при формировании двух уровней выходного тока (в двоичном режиме), выполненная согласно прототипу заявляемого изобретения.

Фиг.3 Схема работы дифференциального усилителя при формировании трех уровней выходного тока (в троичном режиме), выполненная согласно заявляемому изобретению.

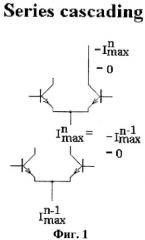

Фиг.4 Схема ЦАП с параллельным подключением дифференциальных усилителей, выполненная согласно заявляемому изобретению.

На Фиг.4 показан пример цифроаналогового преобразователя, содержащего пять источников 1 тока и такое же число дифференциальных усилителей 2, каждый из которых соединен с одним источником 1 тока и выполнен с возможностью питания от данного источника тока. Выходы 3 дифференциальных усилителей соединены параллельно. Токи I0 источников 1 тока находятся в троичном соотношении 1:3:9:27:81…, а входами 4 дифференциальных усилителей 2 управляют с помощью внешнего устройства таким образом, что ток каждого выхода 3 усилителя 2 принимает значения 0, I0, I0/2.

Дифференциальные усилители на Фиг.4 условно показаны выполненными на основе биполярных транзисторов. Точно так же имеется возможность выполнения дифференциальных усилителей на основе полевых (КМОП) транзисторов и транзисторов других типов.

Использование троичной логики управления заявленным ЦАП позволяет уменьшить число каскадов при сопоставимой точности. Так, 5-разрядный заявленный троичный ЦАП имеет точность, определяемую числом градаций выходного тока 243 (35=243), в то время как близкий по точности известный двоичный ЦАП обеспечивает 256 градаций выходного тока при 8 разрядах (28=256), т.е. сложность заявленного ЦАП меньше почти в 2 раза (8/5=1,8).

Хотя указанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

1. Цифроаналоговый преобразователь, содержащий несколько источников тока и такое же число дифференциальных усилителей, каждый из которых соединен с одним источником тока и выполнен с возможностью питания от данного источника тока, причем выходы дифференциальных усилителей соединены, отличающийся тем, что токи I0 источников тока находятся в троичном соотношении между собой, а входами дифференциальных усилителей управляют таким образом, что ток каждого выхода усилителя принимает значения 0, I0, I0/2.

2. Цифроаналоговый преобразователь по п.1, отличающийся тем, что дифференциальные усилители выполнены на основе транзисторов, выбранных из группы, которая содержит биполярные транзисторы, полевые (КМОП) транзисторы и транзисторы других типов.

3. Цифроаналоговый преобразователь по п.1, отличающийся тем, что выходы дифференциальных усилителей соединены параллельно.

4. Цифроаналоговый преобразователь по п.1, отличающийся тем, что выходы дифференциальных усилителей соединены последовательно, при этом выходы части дифференциальных усилителей являются источниками тока для остальных дифференциальных усилителей.

5. Цифроаналоговый преобразователь по п.1, отличающийся тем, что токи I0 источников тока находятся в троичном соотношении между собой, а именно в соотношении 1:3:9:27:81.