Самосинхронный однотактный d-триггер с низким активным уровнем сигнала управления

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Техническим результатом изобретения является обеспечение самосинхронной реализации однотактного D-триггера с однофазным кодированием информационного входа, низким активным уровнем сигнала управления и парафазным кодированием информационного выхода. Этот результат достигается тем, что в схему, содержащую бистабильную ячейку, информационный вход, управляющий вход, прямой и инверсный информационные выходы и индикаторный выход, введены еще один элемент И-ИЛИ-НЕ и инвертор. 4 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен D-триггер [1], содержащий четыре элемента И-НЕ и инвертор.

Недостаток известного устройства - отсутствие средств индикации окончания переходных процессов.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный RS-тригтер [2], содержащий бистабильную ячейку на элементах И-ИЛИ-НЕ с парафазным кодированием информационных входов и выходов и индикаторный элемент И-ИЛИ-НЕ.

Недостаток прототипа - работа только с данными, представленными в парафазном коде, что удваивает число информационных связей между многоразрядным источником входной информации и регистром на базе данного триггера и не позволяет использовать его в качестве элемента интерфейса между синхронными и самосинхронными схемами.

Задача, решаемая в изобретении, заключается в обеспечении самосинхронной реализации однотактного D-триггера с однофазным информационным входом и низким активным уровнем сигнала управления, гарантирующей работоспособность триггера при любых задержках составляющих его элементов.

Это достигается тем, что в триггере, содержащем три элемента И-ИЛИ-НЕ, информационный вход, управляющий вход, прямой и инверсный информационные выходы и индикаторный выход, введены инвертор на информационном входе и еще один элемент И-ИЛИ-НЕ, информационный вход подключен к входу инвертора, второму входу первой группы входов И первого элемента И-ИЛИ-НЕ, первому входу первой группы входов И третьего элемента И-ИЛИ-НЕ и первому входу первой группы входов И четвертого элемента И-ИЛИ-НЕ, управляющий вход соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ, выход которого подключен ко вторым входам первых групп входов И второго и третьего элементов И-ИЛИ-НЕ и третьим входам первой и второй групп входов И четвертого элемента И-ИЛИ-НЕ, выход инвертора подключен к первым входам первых групп входов И первого и второго элементов И-ИЛИ-НЕ и первому входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ подключен ко второму входу первой группы входов И четвертого элемента И-ИЛИ-НЕ, входу второй группы входов И третьего элемента И-ИЛИ-НЕ и прямому информационному выходу триггера, выход третьего элемента И-ИЛИ-НЕ соединен со вторым входом второй группы входов И четвертого элемента И-ИЛИ-НЕ, входом второй группы входов И второго элемента И-ИЛИ-НЕ и инверсным информационным выходом триггера, выход четвертого элемента И-ИЛИ-НЕ подключен к индикаторному выходу триггера.

Предлагаемое устройство удовлетворяет критерию "существенные отличия".

Использование элементов И-ИЛИ-НЕ и инверторов для реализации D-триггера известно. Однако использование их в данном случае позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

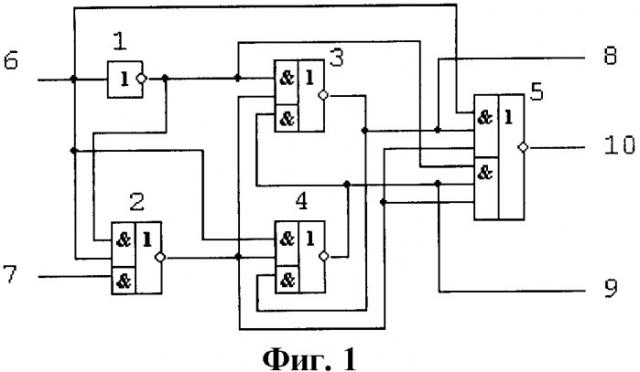

На фиг.1 изображена схема самосинхронного однотактного D-триггера с однофазным входом данных.

Схема D-триггера содержит инвертор 1, четыре элемента И-ИЛИ-НЕ 2-5, информационный вход 6, управляющий вход 7, прямой информационный выход 8, инверсный информационный выход 9 и индикаторный выход 10, информационный вход 6 подключен к входу инвертора 1, второму входу первой группы входов И элемента И-ИЛИ-НЕ 2, первому входу первой группы входов И элемента И-ИЛИ-НЕ 4 и первому входу первой группы входов И элемента И-ИЛИ-НЕ 5, управляющий вход 7 соединен с входом второй группы входов И элемента И-ИЛИ-НЕ 2, выход которого подключен ко вторым входам первых групп входов И элементов И-ИЛИ-НЕ 3 и 4 и третьим входам первой и второй групп входов И элемента И-ИЛИ-НЕ 5, выход инвертора 1 подключен к первым входам первых групп входов И элементов И-ИЛИ-НЕ 2 и 3 и первому входу второй группы входов И элемента И-ИЛИ-НЕ 5, выход элемента И-ИЛИ-НЕ 3 подключен ко второму входу первой группы входов И элемента И-ИЛИ-НЕ 5, входу второй группы входов И элемента И-ИЛИ-НЕ 4 и прямому информационному выходу триггера 8, выход элемента И-ИЛИ-НЕ 4 соединен со вторым входом второй группы входов И элемента И-ИЛИ-НЕ 5, входом второй группы входов И элемента И-ИЛИ-НЕ 3 и инверсным информационным выходом триггера 9, выход элемента И-ИЛИ-НЕ 5 подключен к индикаторному выходу триггера 10.

Схема функционирует следующим образом. Запись нового состояния с информационного входа 6 в бистабильную ячейку, образованную элементами 3 и 4, обеспечивается подачей на управляющий вход 7 активного низкого уровня. Выход элемента 2 переключается в высокое состояние, открывая тем самым входы бистабильной ячейки на элементах 3 и 4. Если на информационном входе 6 высокий уровень, элемент И-ИЛИ-НЕ 4 переключится в состояние "0", а элемент И-ИЛИ-НЕ 3 - в состояние "1". При этом индикаторный выход 10 переходит в состояние "0". При высоком уровне сигнала на управляющем входе 7 выход элемента 2 переключается в низкое состояние и бистабильная ячейка запирается по входам, сохраняя состояние своих выходов. При этом индикаторный выход 10 перейдет в состояние "1". Элемент 5 выполняет функцию индикатора окончания переходных процессов во всех элементах однотактного D-триггера и регулятора фаз его переключения. Значение "0" на выходе элемента 5 свидетельствует об окончании переключения триггера в рабочую фазу, а значение "1" - об окончании переключения триггера в спейсер - фазу хранения своего состояния, обеспечивая тем самым самосинхронность его функционирования.

Особенности данной схемы по сравнению с прототипом следующие.

Информационный вход триггера является однофазным, что позволяет использовать D-триггер в качестве элемента интерфейса между синхронной и самосинхронной схемами. Уточненный индикаторный выход фиксирует момент окончания переходных процессов во всех элементах триггера как тех, которые были в составе прототипа, так и вновь введенных, что обеспечивает индикацию всех элементов в составе самосинхронной схемы.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу однотактного D-триггера с однофазным информационным входом. Цель изобретения достигнута.

Кроме того, предлагаемый однотактный D-триггер позволяет вдвое сократить число информационных связей между многоразрядным источником входной информации и регистром на базе данного самосинхронного D-триггера.

Данный однотактный D-триггер не имеет входов установки "0" и "1", что в ряде практических случаев является существенным недостатком. Однако предлагаемый вариант легко преобразуется в триггер с предустановкой.

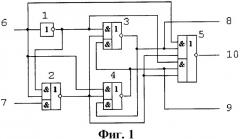

На фиг.2 изображена схема самосинхронного однотактного D-триггера с низким активным уровнем сигнала управления с входом установки "нуля" 11. Схема отличается от схемы на фиг.1 тем, что вторая группа входов И элемента И-ИЛИ-НЕ 4 содержит два входа, первый из которых подключен к входу установки "нуля" 11, а второй - к выходу элемента И-ИЛИ-НЕ 3, как и в схеме на фиг.1. Установка "нуля" осуществляется подачей на управляющий вход 7 высокого уровня, а на вход установки 11 - низкого уровня. В результате выход элемента 2 переключается в состояние низкого уровня, выход элемента И-ИЛИ-НЕ 4, формирующий инверсный выход триггера 9, переключается в состояние "логической единицы" (высокий уровень), а элемент И-ИЛИ-НЕ 3, формирующий прямой выход триггера 8, вслед за этим переходит в состояние низкого уровня, завершая установку.

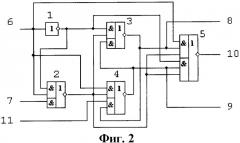

На фиг.3 изображена схема самосинхронного однотактного D-триггера с низким активным уровнем сигнала управления с установкой "единицы" 11. Схема отличается от схемы на фиг.1 тем, что вторая группа входов И элемента И-ИЛИ-НЕ 3 содержит два входа, первый из которых подключен к входу установки "единицы" 11, а второй - к выходу элемента И-ИЛИ-НЕ 4, как и в схеме на фиг.1. Установка "единицы" осуществляется подачей на управляющий вход 7 высокого уровня, а на вход установки 11 - низкого уровня. В результате выход элемента 2 переключается в состояние низкого уровня, выход элемента И-ИЛИ-НЕ 3, формирующий прямой выход триггера 8, переключается в состояние "логической единицы" (высокий уровень), а выход элемента И-ИЛИ-НЕ 4, формирующий инверсный выход триггера 9, вслед за этим переходит в состояние низкого уровня.

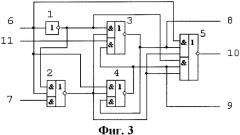

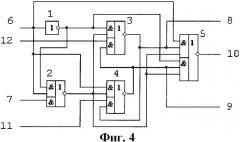

На фиг.4 изображена схема самосинхронного однотактного D-триггера с низким активным уровнем сигнала управления с установкой "единицы" и "нуля". Схема отличается от схемы на фиг.1 тем, что вторая группа входов И элемента И-ИЛИ-НЕ 4 содержит два входа, первый из которых подключен к входу установки "нуля" 11, а второй - к выходу элемента И-ИЛИ-НЕ 3, как и в схеме на фиг.1, вторая группа входов И элемента И-ИЛИ-НЕ 3 содержит два входа, первый из которых подключен к входу установки "единицы" 12, а второй - к выходу элемента И-ИЛИ-НЕ 4, как и в схеме на фиг.1. Установка "нуля" или "единицы" осуществляется способом, описанным выше. Одновременная подача на входы установки "нуля" 11 и "единицы" 12 низкого уровня запрещена.

На фиг.5 изображена схема самосинхронного однотактного D-тригтера с низким активным уровнем сигнала управления с однофазным входом данных и фазовым выходом 11, подключенным к выходу элемента И-ИЛИ-НЕ 2. Фазовый (инициирующий фазу работы D-триггера) выход связи служит для ускорения срабатывания устройства-источника информационного сигнала: разрешение на его переход в противоположную фазу работы выдается сразу, как только переключится элемент И-ИЛИ-НЕ 2 в составе триггера после прихода нового значения на управляющий вход 7, без ожидания окончания переключения остальных элементов в составе схемы триггера. Аналогичный выход может использоваться и во всех остальных вариантах D-триггера, описанных выше.

Источники информации

1. Шило В.Л. Популярные цифровые микросхемы: Справочник. 2-е изд., испр. - Челябинск: Металлургия, Челябинское отд., 1989 - рис.1.50а.

2. Астахановский А.Г., Варшавский В.И., Мараховский В.Б. и др. Апериодические автоматы. // Под ред. В.И.Варшавского. - М: Наука, 1976. - рис.2.7б.

1. Самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления, содержащий три элемента И-ИЛИ-НЕ, информационный вход, управляющий вход, прямой и инверсный информационные выходы и индикаторный выход, отличающийся тем, что в схему введены инвертор на информационном входе и еще один элемент И-ИЛИ-НЕ, информационный вход подключен к входу инвертора, второму входу первой группы входов И первого элемента И-ИЛИ-НЕ, первому входу первой группы входов И третьего элемента И-ИЛИ-НЕ и первому входу первой группы входов И четвертого элемента И-ИЛИ-НЕ, управляющий вход соединен с входом второй группы входов И первого элемента И-ИЛИ-НЕ, выход которого подключен ко вторым входам первых групп входов И второго и третьего элементов И-ИЛИ-НЕ и третьим входам первой и второй групп входов И четвертого элемента И-ИЛИ-НЕ, выход инвертора подключен к первым входам первых групп входов И первого и второго элементов И-ИЛИ-НЕ и первому входу второй группы входов И четвертого элемента И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ подключен ко второму входу первой группы входов И четвертого элемента И-ИЛИ-НЕ, входу второй группы входов И третьего элемента И-ИЛИ-НЕ и прямому информационному выходу триггера, выход третьего элемента И-ИЛИ-НЕ соединен со вторым входом второй группы входов И четвертого элемента И-ИЛИ-НЕ, входом второй группы входов И второго элемента И-ИЛИ-НЕ и инверсным информационным выходом триггера, выход четвертого элемента И-ИЛИ-НЕ подключен к индикаторному выходу триггера.

2. Самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления по п.1, отличающийся тем, что в него введен вход установки нуля, и вторая группа входов И третьего элемента И-ИЛИ-НЕ имеет два входа, первый из которых соединен с входом установки нуля, а второй вход подключен к выходу второго элемента И-ИЛИ-НЕ.

3. Самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления по п.1, отличающийся тем, что в него введен вход установки единицы, и вторая группа входов И второго элемента И-ИЛИ-НЕ имеет два входа, первый из которых соединен с входом установки единицы, а второй вход подключен к выходу третьего элемента И-ИЛИ-НЕ.

4. Самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления по п.2, отличающийся тем, что в него введен вход установки единицы, и вторая группа входов И второго элемента И-ИЛИ-НЕ имеет два входа, первый из которых соединен с входом установки единицы, а второй вход подключен к выходу третьего элемента И-ИЛИ-НЕ.

5. Самосинхронный однотактный D-триггер с низким активным уровнем сигнала управления по любому из пп.1-4, отличающийся тем, что в схему введен фазовый выход, соединенный с выходом первого элемента И-ИЛИ-НЕ.