Каскодный дифференциальный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями э.д.с. смещения нуля (ОУ)). Технический результат заключается в уменьшении напряжения смещения нуля. Каскодный дифференциальный усилитель (КДУ) с малым напряжением смещения нуля содержит первый (1) и второй (2) выходные транзисторы (Т) одного типа проводимости, объединенные базы которых подключены к источнику напряжения смещения (3), а эмиттеры соединены с соответствующими токовыми входами (4, 5), а также первым (6) и вторым (7) токостабилизирующими двухполюсниками, третий (8) и четвертый (9) выходные Т другого типа проводимости, эмиттеры которых объединены, а базы связаны друг с другом, причем коллектор четвертого (9) выходного Т соединен с коллектором второго (2) выходного Т и выходом (10) КДУ, а коллектор первого (1) выходного Т соединен с коллектором третьего (8) выходного Т. В схему введен согласующий повторитель тока (11), вход (12) которого соединен с объединенными коллекторами первого (1) и третьего (8) выходных Т, общий выход (13) подключен к объединенным базам третьего (8) и четвертого (9) выходных Т, а выход (14) связан с эмиттером второго (2) выходного Т. 3 з.п. ф-лы, 14 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями э.д.с. смещения нуля (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах [1-36], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ, на их модификации выдано более 100 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

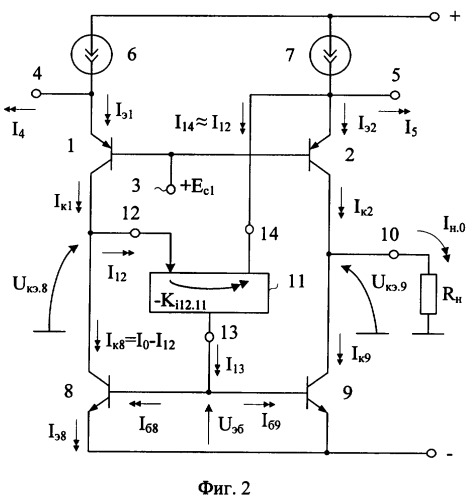

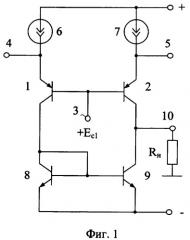

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте фирмы Texas Instruments (США) №6.304.143, содержащий первый 1 и второй 2 выходные транзисторы одного типа проводимости, объединенные базы которых подключены к источнику напряжения смещения 3, эмиттеры соединены с соответствующими токовыми входами 4, 5, а также первым 6 и вторым 7 токостабилизирующими двухполюсниками, третий 8 и четвертый 9 выходные транзисторы другого типа проводимости, эмиттеры которых объединены, а базы связаны друг с другом, причем коллектор четвертого 9 выходного транзистора соединен с коллектором второго 2 выходного транзистора и выходом 10 каскодного дифференциального усилителя, а коллектор первого выходного транзистора 1 соединен с коллектором третьего 8 выходного транзистора.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет сравнительно большое значение напряжения смещения нуля (Uсм), что отрицательно сказывается на статических параметрах различных аналоговых устройств на его основе.

Основная цель предлагаемого изобретения состоит в уменьшении напряжения смещения нуля.

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 выходные транзисторы одного типа проводимости, объединенные базы которых подключены к источнику напряжения смещения 3, эмиттеры соединены с соответствующими токовыми входами 4, 5, а также первым 6 и вторым 7 токостабилизирующими двухполюсниками, третий 8 и четвертый 9 выходные транзисторы другого типа проводимости, эмиттеры которых объединены, а базы связаны друг с другом, причем коллектор четвертого 9 выходного транзистора соединен с коллектором второго 2 выходного транзистора и выходом 10 каскодного дифференциального усилителя, а коллектор первого выходного транзистора 1 соединен с коллектором третьего 8 выходного транзистора, предусмотрены новые элементы и связи - в схему введен согласующий повторитель тока 11, вход 12 которого соединен с объединенными коллекторами первого 1 и третьего 8 выходных транзисторов, общий выход 13 подключен к объединенным базам третьего 8 и четвертого 9 выходных транзисторов, а выход 14 связан с эмиттером второго 2 выходного транзистора.

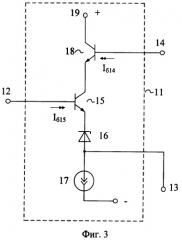

Схема усилителя-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.2 формулы изобретения. На чертеже фиг.3, в соответствии с п.3 формулы изобретения, показан частный случай выполнения согласующего повторителя тока 11, который содержит первый 15 дополнительный транзистор, эмиттер которого соединен через источник опорного напряжения 16 с общим выходом 13 согласующего повторителя тока 11 и вспомогательным источником тока 17, база является входом 12 согласующего повторителя тока 11, коллектор подключен к эмиттеру второго дополнительного транзистора 18, причем база второго дополнительного транзистора 18 является выходом 14 согласующего повторителя тока 11, а коллектор транзистора 18 соединен с источником питания 19.

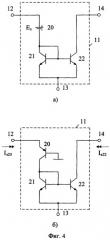

На чертеже фиг.4, соответствующем п.4 формулы изобретения, показан другой частный случай выполнения согласующего повторителя тока 11, который содержит цепь смещения 20, включенную между входом 12 согласующего повторителя тока 11 и дополнительным p-n переходом 21, выходной вспомогательный транзистор 22, база которого подключена к первому выводу дополнительного p-n перехода 21 и цепи смещения 20, эмиттер соединен с общим выходом 13 согласующего повторителя тока 11 и вторым выводом дополнительного p-n перехода 21, а коллектор является выходом 14 согласующего повторителя тока 11. В частном случае (фиг.4б) цепь смещения реализована на транзисторе.

На чертеже фиг.5 представлена схема КДУ, в котором согласующий повторитель тока 11 реализован в соответствии с фиг.3.

Схема операционного усилителя на базе предлагаемого КДУ с входным каскадом на элементах 23 и 24 и выходным каскадом на основе типового буферного усилителя 25 для случая, когда согласующий повторитель тока 11 соответствует фиг.4, показана на чертеже фиг.6.

Другой частный случай КДУ фиг.2 при выполнении согласующего повторителя тока 11 в соответствии со схемой фиг.4а представлен на чертеже фиг.7.

Схема КДУ-прототипа в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» показана на чертеже фиг.8. В этой схеме Uсм=-10,2 мВ.

Схема предлагаемого КДУ фиг.6 в среде PSpice показана на чертеже фиг.9. В этой схеме без каких-либо регулировок Uсм=713 мкв.

На чертеже фиг.10а представлена макромодель p-n-p транзистора минского НПО «Интеграл», а на чертеже фиг.10б - зависимость его β от тока коллектора.

На чертеже фиг.11 показана модель операционного усилителя на основе КДУ-прототипа на интегральных транзисторах минского НПО «Интеграл». Здесь Uсм=1,74 мВ.

На чертеже фиг.12 показана схема ОУ на базе заявляемого КДУ фиг.5 в среде PSpice на моделях интегральных транзисторов НПО «Интеграл». Здесь Uсм=113,5 мкВ.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 выходные транзисторы одного типа проводимости, объединенные базы которых подключены к источнику напряжения смещения 3, а эмиттеры соединены с соответствующими токовыми входами 4, 5, а также первым 6 и вторым 7 токостабилизирующими двухполюсниками, третий 8 и четвертый 9 выходные транзисторы другого типа проводимости, эмиттеры которых объединены, а базы связаны друг с другом, причем коллектор четвертого 9 выходного транзистора соединен с коллектором второго 2 выходного транзистора и выходом 10 каскодного дифференциального усилителя, а коллектор первого выходного транзистора 1 соединен с коллектором третьего 8 выходного транзистора. В схему введен согласующий повторитель тока 11, вход 12 которого соединен с объединенными коллекторами первого 1 и третьего 8 выходных транзисторов, общий выход 13 подключен к объединенным базам третьего 8 и четвертого 9 выходных транзисторов, а выход 14 связан с эмиттером второго 2 выходного транзистора.

Рассмотрим работу заявляемого каскодного дифференциального усилителя на примере анализа схемы фиг.2.

Статический режим по току КДУ фиг.2 устанавливается двухполюсниками 6 и 7 с учетом токов входов 14 и 15, формируемых источником сигнала. При этом токи в элементах схемы, соответствующие обозначениям на чертеже фиг.2 при идентичных напряжениях коллектор-эмиттер транзисторов 8 и 9 Uкэ.8=Uкэ.9 (п.2 формулы изобретения)

Iк1=α1I0,

Iк2=α2(I0-I14),

Iк8=Iк1-I12=α1I0-I12,

Iэ8=α8 -1(α1I0-I12)=Iэ9,

I14=I12Ki12.11,

I9=α9Iэ9,

где Iкij - коллекторные токи транзисторов;

I4, I5 - статические токи входов 4 и 5 КДУ;

αi≈1 - статические коэффициенты передачи по току эмиттера транзисторов КДУ;

- коэффициент передачи по току согласующего повторителя тока 11.

Таким образом, ток ошибки в нагрузке Rн КДУ фиг.2

.

После преобразований последнюю формулу можно представить в виде

,

где ;

.

В схеме КДУ-прототипа Kcom=0, так как отсутствует дополнительная передача тока I12 на выход КДУ.

В заявляемом устройстве при α1=α2, α9=α8 ток в нагрузке, обусловленный структурными погрешностями схемы, существенно уменьшается

Iн.0=I12(1-Kcom)<<I12.

Это уменьшает одну составляющую напряжения смещения нуля в Nc-раз, где

.

Кроме этого за счет повышения симметрии статического режима по напряжению коллектор-эмиттер транзисторов 8 и 9 Uкэ.8=Uкэ.9 (п.2 формулы изобретения) уменьшается другая составляющая Uсм, которая обусловлена внутренней обратной связью в транзисторах (эффектом Эрли).

Как показывает компьютерное моделирование, в предлагаемом КДУ Uсм уменьшается без каких-либо регулировок более чем на порядок.

Данный вывод справедлив для КДУ, выполненных как на интегральных транзисторах минского НПО «Интеграл», так и транзисторах ФГУП НПП «Пульсар».

Следовательно, в схеме фиг.2 созданы условия, при которых устраняется систематическая ошибка усиления сигналов постоянного тока, обусловленная структурными особенностями КДУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

2. Патент США №6.218.900, фиг.1

3. Патентная заявка US 2002/0196079

4. Патент США №6.788.143

5. Патент США №3.644.838, фиг.2

6. Патент США Re 30.587

7. Патент ЕР 1.227.580

8. Патент США №6.714.076

9. Патент США №5.786.729

10. Патент США №5.327.100

11. Патентная заявка US 2004/0090268 A1

12. Патент США №4.274.061

13. Патент США №5.422.600, фиг.2

14. Патент США №6.788.143, фиг.2

15. Патент США №4.959.622, фиг.1

16. Патент США №4.406.990, фиг.4

17. Патент США №5.418.491

18. Патент США №6.018.268

19. Патент США №5.952.882

20. Патент США №4.723.111

21. Патент США №4.293.824

22. Патент США №6.580.325

23. Патент США №6.965.266

24. Патент США №6.867.643

25. Патент США №6.236.270

26. Патент США №5.323.121

27. Патент США №6.229.394

28. Патент США №5.734.296

29. Патент США №5.477.190

30. Патент США №5.091.701

31. Патент США №6.717.474

32. Патент США №6.084.475

33. Патент США №3.733.559

34. Патентная заявка US 2005/0001682 A1

35. Патент США №6.300.831

1. Каскодный дифференциальный усилитель с малым напряжением смещения нуля, содержащий первый (1) и второй (2) выходные транзисторы одного типа проводимости, объединенные базы которых подключены к источнику напряжения смещения (3), а эмиттеры соединены с соответствующими токовыми входами (4), (5), а также первым (6) и вторым (7) токостабилизирующими двухполюсниками, третий (8) и четвертый (9) выходные транзисторы другого типа проводимости, эмиттеры которых объединены, а базы связаны друг с другом, причем коллектор четвертого (9) выходного транзистора соединен с коллектором второго (2) выходного транзистора и выходом (10) каскодного дифференциального усилителя, а коллектор первого выходного транзистора (1) соединен с коллектором третьего (8) выходного транзистора, отличающийся тем, что в схему введен согласующий повторитель тока (11), вход (12) которого соединен с объединенными коллекторами первого (1) и третьего (8) выходных транзисторов, общий выход (13) подключен к объединенным базам третьего (8) и четвертого (9) выходных транзисторов, а выход (14) связан с эмиттером второго (2) выходного транзистора.

2. Устройство по п.1, отличающееся тем, что статическое напряжение коллектор-эмиттер третьего выходного транзистора (8) приблизительно равно статическому напряжению коллектор-эмиттер четвертого (9) выходного транзистора.

3. Устройство по п.1, отличающееся тем, что согласующий повторитель тока (11) содержит первый (15) дополнительный транзистор, эмиттер которого соединен через источник опорного напряжения (16) с общим выходом (13) согласующего повторителя тока (11) и вспомогательным источником тока (17), база является входом (12) согласующего повторителя тока (11), коллектор подключен к эмиттеру второго дополнительного транзистора (18), причем база второго дополнительного транзистора (18) является выходом (14) согласующего повторителя тока (11), а коллектор транзистора (18) соединен с источником питания (19).

4. Устройство по п.1, отличающееся тем, что согласующий повторитель тока (11) содержит источник напряжения смещения (20), включенный между входом (12) согласующего повторителя тока (11) и дополнительным p-n переходом (21), выходной вспомогательный транзистор (22), база которого подключена к первому выводу дополнительного p-n перехода (21) и источнику напряжения смещения (20), эмиттер соединен с общим выходом (13) согласующего повторителя тока (11) и вторым выводом дополнительного p-n перехода (21), а коллектор является выходом (14) согласующего повторителя тока (11).