Устройство автоматического управления нагружением при программных испытаниях механических конструкций на усталостную прочность

Иллюстрации

Показать всеИзобретение относится к области систем автоматического управления испытательными машинами и стендами для прочностных испытаний механических конструкций. Технический результат - повышение точности нагружения испытываемых конструкций в точках локальных экстремумов испытательной программы, что значительно повышает точность определения ресурса изделий, а также поддержание постоянной средней скорости нагружения испытываемых конструкций. Для решения поставленной задачи для каждой подгруппы локальных экстремумов (максимумов и минимумов), включающей в свой состав одноименные экстремумы одинаковой величины, используются свои накопители разностей, обеспечивающие коррекцию экстремумов управляющего сигнала программы для каждой подгруппы. Разности для каждой подгруппы накапливаются до тех пор, пока разность между экстремумом сигнала обратной связи и соответствующим ему экстремумом программного сигнала не станет равной нулю. Для правильного вычисления поправок, корректирующих экстремумы управляющего сигнала в устройство дополнительно введены элементы, определяющие моменты вычисления указанных поправок и регламентирующие порядок пересылки информации между отдельными узлами устройства. К этим элементам относятся задержки служебных сигналов, формирователи длины импульсов служебных сигналов, ключи, регистры, содержащие обновляемую от участка к участку программы информацию о номерах экстремумов и их ординатах, а также памяти, поочередно хранящие после интерполяции все промежуточные точки о генерируемых в данный момент участках программы. Для поддержания постоянства средней скорости нагружения в устройстве используется сумматор, вычисляющий размах участка программы, регистры для временного хранения этой информации и делители, делящие опорную частоту в зависимости от величины размаха участка программы так, что обеспечивается постоянная средняя скорость генерации каждого участка программы независимо от изменения величины его размаха. 4 ил.

Реферат

Изобретение относится к системам автоматического управления испытательными машинами и экспериментальными стендами для прочностных усталостных испытаний механических конструкций, в частности авиационных. Анализ эксплуатационных разрушений и нагруженности конструкций позволяет выделить группы машин, их деталей и элементов, для которых разрабатываются определенные виды программ нагружения (Воробьев А.З., Картамышев А.И., Райхер В.Л., Свирский Ю.А. «Типизированные программы нагружения. Комплексное обеспечение ресурса авиационных конструкций» Сб. докладов научно-технической конференции, кн. 5, ЦАГИ, 1984; «Схематизация процессов нагружения» ГОСТ 2307-78 Государственный комитет по стандартам М. 1978).

В простейшем случае это циклические или многоступенчатые циклические программы, в более сложном - типизированные или псевдослучайные, содержащие большое количество локальных максимумов и минимумов. Локальные максимумы и минимумы по своим уровням относятся к нескольким подгруппам (например 40), имеющим детерминированные значения. Чередование экстремумов носит случайный характер.

Подобные программы изменения усилий, нагружающих конструкцию, разрабатывались в США, Германии, Англии, например, TWIST, FALSTAFF. В России (в ЦАГИ) разработаны аналогичные программы ПУСК и ПРИМА.

Важным вопросом применения этих программ является точность их задания, а также точность отслеживания средствами автоматического управления экспериментом. Основным требованием с точки зрения накопления усталостных повреждений является точность воспроизведения локальных экстремумов нагрузки, воздействующей на конструкцию.

Известны системы автоматического управления циклическими испытаниями (см. Литвак В.И. «Автоматизация усталостных испытаний натурных конструкций», М. Машиностроение, 1972, стр.102-120). Система автоматического управления в известном аналоге построена по традиционному принципу и содержит следящий гидравлический сервопривод, создающий нагружающее воздействие на испытуемую механическую конструкцию. На вход этого следящего гидропривода подается управляющий циклический сигнал от программно-задающего устройства, построенного на базе генератора гармонических функций.

Следящий гидропривод сравнивает управляющий сигнал с сигналом обратной связи и формирует воздействие на исполнительный орган (гидроцилиндр), который создает силовое воздействие на объект испытаний.

Недостатком известных систем является зависимость точности воспроизведения нагружающих воздействий от динамических характеристик следящего привода и объектов испытаний и неинвариантность точности работы этих систем к изменению динамических характеристик объекта и привода в процессе испытаний. Погрешность нагружения в точках экстремумов изменяется от 2% до 10%, что приводит к большим погрешностям при определении ресурса конструкций по кривым выносливости:

где σ - величина механических напряжений в конструкции в экстремальных точках изменяющегося нагружающего усилия;

m - показатель степени, изменяющийся в пределах от 4 до 10;

K - число циклов нагружения с амплитудой σ до появления трещины.

Наиболее близким к предлагаемому техническому решению является «Устройство для управления циклическим нагружением при прочностных испытаниях» Гуков Б.Ф., Еремеев Ю.М., Свирский Ю.А., Стерлин А.Я. (а.с. №943758 (СССР) опубликовано 15.07.1982, Бюл. №26, М.кл. G06G 7/26).

Достоинством прототипа по отношению к аналогам является коррекция величин экстремумов генерируемой циклической функции, таким образом, что экстремумы управляющего сигнала, поступающего на вход следящего привода, изменяются на величину, равную разности между фактическим сигналом, измеряемым датчиком обратной связи (датчиком нагрузки) и сигналом с выхода программо-задающего устройства, который будем считать эталонным. Измеренные разности в максимумах и минимумах в каждом цикле функции суммируются в двух накопителях (один для максимумов, другой для минимумов), а затем от цикла к циклу прибавляются к соответствующим экстремумам эталонного программного сигнала до тех пор, пока разность между экстремумом эталонного сигнала и экстремумом сигнала обратной связи не станет равной нулю (до точности работы устройства, вычисляющего указанную разность).

Устройство, принятое за прототип, содержит блок задания ступеней нагрузки (программный задатчик), датчик обратной связи (датчик нагрузки), экстрематор, две параллельные цепи для коррекции максимумов и минимумов, каждая из которых состоит из блока сравнения (компаратора), накопителя и сумматора. Выходы сумматоров каждой цепи соединены с входами интерполятора, выход которого связан с входом следящего исполнительного привода (следящего исполнительного блока).

Недостатком известного устройства является то, что оно непригодно для коррекции локальных экстремумов при реализации типизированных и псевдослучайных программ нагружения, т.к. в прототипе используются только два накопителя - один для коррекции максимума, а другой минимума, которые на каждой ступени программы постоянны, что ограничивает применение прототипа только для циклических функций нагружения с постоянной амплитудой. Кроме того, при изменении величины экстремумов изменяется средняя скорость генерируемого участка программы, что искажает оптимальную скорость, заданную программой.

Задачей настоящего изобретения является устранение выше перечисленных недостатков, а именно обеспечение возможности корректировать экстремумы, не только циклических программ нагружения, но и экстремумы типизированных и псевдослучайных программ, задавая при этом постоянную (оптимальную) среднюю скорость нагружения на каждом участке программы испытаний.

Технический результат предлагаемого изобретения состоит в снижении погрешности в локальных экстремумах нагрузки, воздействующей на конструкцию до 0,1% и сокращении времени реализации программ испытаний за счет обеспечения оптимальной скорости нагружения.

Решение поставленной задачи и технический результат в предлагаемом изобретении достигаются тем, что принципиально изменены составы и схемные решения программного задатчика и интерполятора. Введены дополнительные элементы, обеспечивающие накопление и хранение корректирующих разностей для всех подгрупп локальных экстремумов, а также постоянство средней скорости нагружения на любых участках программы. При этом устройство содержит программный задатчик, датчик нагрузки, подключенный к входу устройства, последовательно включенные интерполятор и следящий исполнительный привод, экстрематор и две параллельные цепи коррекции максимумов и минимумов управляющего программного сигнала, каждая из которых состоит из компаратора, накопителя и сумматора, причем первые входы компараторов соответственно соединены с первыми выходами максимума и минимума программного задатчика, а вторые входы компараторов с одноименными выходами экстрематора, вход которого соединен с выходом датчика нагрузки, входы сумматоров в каждой цепи соответственно соединены со вторыми выходами максимума и минимума программного задатчика и с выходами относящихся к ним накопителей. Программный задатчик в составе предлагаемого устройства содержит блок задания номера участка программы, два блока памяти, состоящих из нескольких подгрупп максимумов и нескольких подгрупп минимумов, два регистра временного хранения номера восходящих участков программы N+1 и N, два дешифратора считывания максимумов и минимумов, первый и второй дополнительные регистры временного хранения максимумов и минимумов предыдущего участка программы, первый элемент «ИЛИ», триггер, первый элемент задержки и три формирователя длины импульсов служебных сигналов с' d', d", два дешифратора записи разностей между экстремумами программы и соответствующими экстремумами сигнала датчика нагрузки, несколько накопителей по одному для каждой подгруппы экстремумов. Кроме того, в устройство введены два регистра временного хранения скорректированных величин максимумов и минимумов управляющего программного сигнала, компаратор размаха каждого участка программы. Интерполятор в предлагаемом устройстве содержит блок вычисления промежуточных точек участков программной управляющей функции, два блока памяти восходящих и нисходящих участков программы, два буферных регистра временного хранения величин размахов восходящих и нисходящих участков программы, два рабочих регистра временного хранения размахов восходящих и нисходящих участков программы, два делителя опорной частоты, генератор опорной частоты, первый и второй ключи передачи частотных сигналов, реверсивный счетчик, первый и второй ключи передачи адресных кодов, второй элемент «ИЛИ». Дополнительно в устройство введены второй и третий элементы задержки, а также два коммутатора разности экстремумов программного сигнала и соответствующих экстремумов сигнала датчика нагрузки. При этом информационный выход блока задания номера участка программы соединен с информационным входом регистра временного хранения номера восходящего участка N+1, выход этого регистра соединен с информационными входами дешифраторов считывания максимумов и минимумов из блоков памяти, а также с входом регистра хранения номера предыдущего восходящего участка N. Выходы дешифраторов считывания максимумов и минимумов соответственно соединены с адресными входами считывания блоков памятей подгрупп максимумов и минимумов и соответствующих им накопителей разностей. Выход блока памяти подгрупп максимумов соединен с входом первого дополнительного регистра временного хранения максимума предыдущего участка программы. Выход блока памяти подгрупп минимумов соединен со входом второго дополнительного регистра временного хранения минимумов предыдущих участков программы. Выход первого дополнительного регистра соединен со входом компаратора в цепи коррекции максимумов управляющего программного сигнала. Выход второго дополнительного регистра соединен со входом компаратора в цепи коррекции минимумов управляющего программного сигнала. Выход регистра хранения номера предыдущего восходящего участка программы N соединен с входами дешифраторов записи разностей между программными экстремумами и одноименными экстремумами сигнала датчика нагрузки. Выходы указанных дешифраторов соединены с адресными входами записи вычисленных разностей в соответствующие накопители. Выход первого элемента «ИЛИ» соединен со входом триггера, выход триггера «d» соединен с входом первого формирователя длины служебных импульсов «d'» и через элемент задержки с входом второго формирователя длины служебных импульсов «d"», а также с управляющими входами первых ключей передачи частотных сигналов и адресных кодов. Выход триггера «с» соединен с входом третьего формирователя служебных импульсов «с'», а также с управляющими входами вторых ключей передачи частотных сигналов и адресных кодов. Выходы сумматоров в цепях максимумов и минимумов соответственно соединены с входами регистров временного хранения скорректированных максимумов и минимумов управляющего программного сигнала. Выходы этих регистров соединены с входами компаратора размаха генерируемого участка, а также с двумя входами блока вычисления промежуточных точек участков программной управляющей функции. Выход блока вычисления соединен с цифровыми входами блоков памяти восходящих и нисходящих участков программы. Выходы блоков памятей объединены и образуют выход интерполятора. Входы управления считыванием информации из блоков памятей восходящих и нисходящих участков через соответствующие два ключа передачи адресных кодов соединены с цифровым выходом реверсивного счетчика. Частотный вход реверсивного счетчика через два ключа передачи частотных сигналов соединен с выходами соответствующих делителей опорной частоты, на один вход которых поступает частотный сигнал с генератора опорной частоты, другой вход каждого из этих делителей связан с выходами рабочих регистров временного хранения размаха восходящих и нисходящих участков программы. Входы этих регистров соединены с выходами одноименных буферных регистров. Входы буферных регистров объединены и подключены к выходу компаратора размаха генерируемого участка. Выход формирователя длины служебного импульса «d'» соединен с управляющими входами дешифратора считывания максимумов, блока памяти нисходящих участков программы и рабочего регистра временного хранения размахов нисходящих участков программы. Выход формирователя длины служебного импульса «d"» соединен с управляющими входами блока задания номера участка программы, регистра временного хранения скорректированных величин максимумов управляющего программного сигнала и буферного регистра хранения размахов восходящих участков. Выход формирователя длины служебных импульсов «с'» соединен с управляющими входами блока памяти восходящих участков программы, рабочего регистра временного хранения размахов восходящих участков программы и первого дополнительного регистра. Выходы обнуления и переполнения реверсивного счетчика соединены с входами второго элемента «ИЛИ». Выход этого элемента «ИЛИ» соединен с одним из входов первого элемента «ИЛИ», на другой вход которого поступает сигнал «ПУСК». Выход признака максимума экстрематора «сэ» связан с входами второго и третьего элементов задержки и с управляющим входом коммутатора разностей максимумов программного сигнала и сигнала датчика нагрузки. Выход второго элемента задержки «с"» связан с управляющими входами регистра хранения номера предыдущего восходящего участка N и дешифратора считывания минимумов. Выход третьего элемента задержки «с"'» соединен с управляющими входами регистра хранения номера восходящего участка N+1, двух дешифраторов записи разностей между экстремумами программы и соответствующими экстремумами сигнала датчика нагрузки, регистра временного хранения скорректированных минимумов управляющего программного сигнала, буферного регистра временного хранения размахов нисходящих участков программы и второго дополнительного регистра. Выход признака минимума экстрематора «dэ» связан с управляющим входом коммутатора разностей минимумов программного сигнала и соответствующих минимумов сигнала датчика нагрузки. Выходы коммутаторов указанных разностей соединены с входами соответствующих накопителей в цепях коррекции максимумов и минимумов управляющей программной функции.

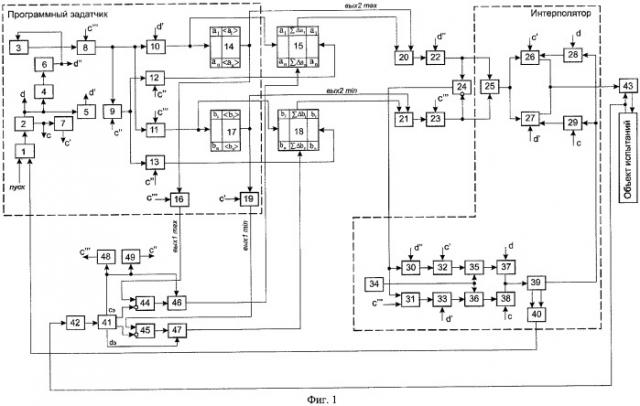

Для пояснения изобретения обратимся к фиг.1, 2, 3, 4. На фиг.1 приведена структура устройства.

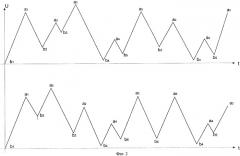

На фиг.2 приведены выборки псевдослучайного процесса нагружения. Эти выборки отличаются друг от друга только последовательностью чередования экстремумов. Величины и число экстремумов в этих выборках совпадает, т.к. этого требует сама методика испытаний.

На фиг.3 приведена циклограмма служебных импульсов, обеспечивающих последовательность пересылки информации между элементами устройства.

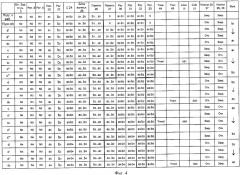

На фиг.4 приведена таблица состояний основных элементов устройства, показывающая передвижение информации между этими элементами по возникновению импульсов, приведенных на циклограмме фиг.3.

Предварительно перед описанием предлагаемого устройства поясним процедуру подготовки исходных данных псевдослучайных программ нагружения (самый сложный случай), т.к. в этих программах последовательность генерации отдельных участков программы недетерминирована. В остальных видах программ эта последовательность строго задана.

Особенность генерации псевдослучайных сигналов состоит в подготовке исходных данных для работы программного устройства. Локальные максимумы разбиваются на подгруппы, в каждую из которых входят максимумы, имеющие одинаковую величину. Таким же образом на подгруппы разбиваются локальные минимумы. Номера подгрупп i=1…n максимума и минимума одинаковых восходящих участков программы совпадают (фиг.2), т.е. восходящие участки носят детерминированный характер. Однако порядок следования восходящих участков в программе носит случайный характер, поэтому параметры нисходящих участков недетерминированы.

Выбор величины скорости изменения управляющих сигналов основывается на одном из постулатов методики ресурсных испытаний, утверждающем, что изменения в определенных пределах частоты или скорости приложения нагружающих воздействий не влияют на ресурс конструкции, если при этом строго соблюдается задание экстремумов нагружающей функции. Поэтому время генерации каждого участка можно строго связать с размахом участка, то есть:

где τ - время генерации участка (сегмента) программы;

µ - постоянный коэффициент;

А - размах участка (разность ординат его начала и конца).

Коэффициент µ практически определяет постоянную среднюю скорость изменения нагружающего воздействия на каждом сегменте программы. Эта средняя скорость выбирается из условия наилучшей работы следящего привода и энергетических возможностей источников энергоснабжения стенда и в этом смысле ее необходимо держать постоянной.

Схема устройства приведена на фиг.1. Это устройство содержит: первый элемент «ИЛИ» 1, триггер 2, блок 3 задания номера участка программы, первый элемент задержки 4, формирователи длины импульсов служебных сигналов d', d", с' 5, 6, 7, регистры временного хранения номеров восходящих участков программы N+1, N 8, 9 (В регистре (8) хранится N+1 номер восходящего участка программы, в регистре (9) номер N предыдущего восходящего участка программы. N и N+1 могут принимать любые значения из множества i=1…n), дешифраторы считывания максимумов и минимумов 10, 11, дешифраторы записи разности между экстремумами программы соответствующими им экстремумами сигнала датчика нагрузки 12, 13, блок памяти подгрупп максимумов аi 14 и соответствующие им накопители корректирующих сигналов ΣΔаi 15, первый дополнительный регистр временного хранения максимумов предыдущих участков программы 16, блок памяти подгрупп минимумов 6, 17 и соответствующие им накопители корректирующих сигналов ΣΔbi 18, второй дополнительный регистр временного хранения минимумов предыдущих участков программы 19, сумматоры 20, 21, определяющие сумму каждого экстремума программы и соответствующего ему корректирующего сигнала; регистры 22, 23 временного хранения скорректированных величин максимумов и минимумов управляющего программного сигнала, компаратор 24 размаха каждого участка программы, блок вычисления 25 промежуточных точек участков управляющей программной функции, блок памяти восходящих участков программы 26, хранящий последовательную информацию обо всех промежуточных точках очередного восходящего участка программы, блок памяти нисходящих участков программы 27, хранящий последовательную информацию об очередном нисходящем участке программы, первый и второй ключи передачи адресных кодов 28, 29, обеспечивающие поступление кодовых сигналов для считывания с блоков памяти 26, 27, буферные регистры временного хранения размахов восходящих и нисходящих участков программы 30, 31, рабочие регистры временного хранения размахов восходящих и нисходящих участков программы 32, 33, генератор 34 опорной частоты, делители опорной частоты 35, 36, вырабатывающие нужную частоту импульсов в зависимости от размаха участка программы, первый и второй ключи передачи частотных сигналов 37, 38, поочередно подающие частотный сигнал на вход реверсивного счетчика 39, обеспечивающего опрос блоков памяти 26, 27, второй элемент «ИЛИ» 40, подающий сигнал об изменении направления работы реверсивного счетчика на первый элемент «ИЛИ» 1, экстрематор 41, определяющий локальные максимумы и минимумы сигнала, получаемого от датчика нагрузки 42, следящий исполнительный привод 43, компараторы 44, 45, определяющие разницу между экстремумами программного сигнала и соответствующими экстремумами сигнала датчика нагрузки; коммутаторы разности 46, 47, соединяющие выходы компараторов 44, 45 с накопителями ΣΔаi, ΣΔbi 15, 18 когда появляются экстремумы (max, min); второй и третий элементы задержки 48, 49.

Элементы 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 16, 17, 19 входят в состав программного задатчика. Все элементы от 25 до 40 входят в состав интерполятора.

Между собой элементы устройства соединены следующим образом. Выход первого элемента «ИЛИ» 1 соединен с входом триггера 2. Один выход триггера 2, именуемый «d», соединен с входом формирователя длины служебных импульсов «d'» 5. Выход «d» триггера 2 через элемент задержки 4 и формирователь длины служебных импульсов «d"» 6 соединен с управляющим входом блока 3 задания номера участка программы. Другой выход триггера 2, именуемый «с», соединен с формирователем длины служебных импульсов «с'» 7. Информационный выход блока 3 соединен с информационным входом регистра 8, в который записывается по импульсному сигналу «с'"» номер (N+1)-го восходящего участка программы. Цифровой выход регистра 8 соединен с информационными входами регистра 9, а также дешифраторов считывания 10, 11. Запись информации в регистр 9 происходит по сигналу «с"», в дешифратор 10 по сигналу «d'», в дешифратор 11 по сигналу «с'"». Выходы дешифраторов 10, 11 соответственно соединены с входами, управляющими считыванием информации из блоков памятей подгрупп максимумов и минимумов 14, 17. Выход регистра 9 соединен с цифровыми входами двух дешифраторов 12, 13 записи разности между экстремумами программы и соответствующими экстремумами сигнала датчика нагрузки. Запись в дешифраторы 12, 13 производится по импульсному сигналу «с"». Выходы дешифраторов 12, 13 соединены с входами, управляющими записью Δаi и Δbi в накопители ΣΔai, ΣΔbi 15, 18. Выход блока памяти подгрупп максимумов 14 (являющийся вторым выходом максимумов программного задатчика), обеспечивающий передачу информации об очередном максимуме программы аi, и выход накопителей ΣΔai 15 соединены с входами сумматора 20. Кроме того, выход блока 14 соединен с входом первого дополнительного регистра 16, выход которого является первым выходом максимумов программного задатчика. Запись в регистр 16 производится сигналом «с'"». Выход блока памяти подгрупп минимумов 17 (являющийся вторым выходом минимумов программного задатчика), обеспечивающий передачу информации об очередном минимуме программы bi, и выход накопителей ΣΔbi 18 соединены с входами сумматора 21. Кроме того, выход блока 17 соединен с входом второго дополнительного регистра 19, выход которого является первым выходом минимумов программного задатчика. Запись в регистр 19 производится сигналом «с'». Выходы сумматоров 20, 21 соответственно соединены с входами регистров 22, 23 временного хранения скорректированных величин максимумов и минимумов управляющего программного сигнала. Запись в регистр 22 производится по сигналу «d"», а в регистр 23 по сигналу «с'"». Выходы регистров 22, 23 соединены с входами компаратора 24 размаха очередного генерируемого участка программы. Величина размаха для восходящих участков программы имеет вид (аN-bN), для нисходящих участков - (аN-bN+1). Кроме того, выходы регистров 22, 23 подключены к входам блока вычисления 25 промежуточных точек участков программной управляющей функции, подготавливаемых к генерации.

Выход блока вычисления 25 подключен к входам блоков памятей восходящих и нисходящих участков программы 26, 27, запись в которые производится соответственно сигналами «с'» и «d'». В блок памяти 26 записывается информация о восходящих участках программы (аN…bN). В блок памяти 27 записывается информация о нисходящих участках программы (аN…bN+1). Выходы блоков памяти 26, 27 объединены и поданы на вход следящего исполнительного привода 43. Считывание информации из блока памяти 26 производится сигналами, приходящими с первого ключа передачи адресных кодов 28, открываемого сигналом «d». Считывание информации из блока памяти 27 производится сигналами, приходящими со второго ключа передачи адресных кодов 29, открываемого сигналом «с». Величина размаха участка программы, подготавливаемого к генерации, с выхода компаратора 24 поступает на входы буферных регистров временного хранения величин размахов восходящих и нисходящих участков программы 30, 31. Запись в эти регистры производится соответственно по служебным сигналам «d"» и «с'"». В буферный регистр 30 записывается информация о размахе восходящих участков программы. В буферный регистр 31 - о размахе нисходящих участков. С выходов буферных регистров 30, 31 информация записывается в соответствующие рабочие регистры временного хранения величин размахов восходящих и нисходящих участков программы 32, 33. В регистр 32 - по сигналу «с'», в регистр 33 - по сигналу «d'». Выходы рабочих регистров 32, 33 соединены со входами делителей 35, 36. Информация с рабочих регистров, поступающая на информационные входы делителей, представляет собой делитель. На другие входы делителей поступают импульсы опорной тактовой частоты от генератора опорной частоты 34. Эта тактовая частота является делимым. Поделенная частота с выходов делителей 35, 36 поступает на первый и второй ключи передачи частотных сигналов 37, 38. Выходы ключей 37, 38 объединены и подключены к входу реверсивного счетчика 39. Ключ 37 открывается сигналом «d», ключ 38 - сигналом «с». Цифровой выход реверсивного счетчика 39 соединен со входами ключей 28, 29. Ключ 28 открывается сигналом «d», ключ 29 - сигналом «с». Сигналы переполнения и обнуления с импульсных выходов счетчика 39, говорящие об изменении направлении счета, через второй элемент «ИЛИ» 40 поступают на один из входов первого элемента «ИЛИ» 1, на другой вход этого элемента поступает сигнал «ПУСК». Сигнал от датчика нагрузки 42 следящего привода 43 поступает на вход экстрематора 41. Сигнал о величине максимума нагрузки с экстрематора 41 поступает на вход компаратора 44, на другой вход этого компаратора поступает сигнал с первого дополнительного регистра 16. Разность между указанными величинами Δаi с выхода компаратора 44 подается на первый коммутатор разностей 46, который открывается импульсным сигналом «сэ», вырабатываемым экстрематором 41 при достижении сигналом датчика нагрузки локального максимума. С выхода коммутатора 46 вычисленная разность Δаi подается в соответствующий накопитель ΣΔai 17. Кроме того, этот же импульсный сигнал «сэ» с экстрематора подается на вторую и третью задержки 48, 49, которые формируют сигналы «с'"» и «с"». При достижении сигналом обратной связи минимума, экстрематор 41 выдает величину минимума на вход компаратора 45, на другой вход этого компаратора подается величина программного минимума со второго дополнительного регистра 19. Разность между этими величинами Δbi с выхода компаратора 45 подается на второй коммутатор разностей 47, который открывается импульсным сигналом «dэ» экстрематора 41, появляющимся при достижении минимума сигналом датчика нагрузки. С выхода коммутатора 47 информация о величине Δbi поступает в соответствующий накопитель ΣΔbi 18.

Устройство работает следующим образом. Перед запуском системы все ее элементы приводятся в начальное состояние, которое таково. В блоке памяти 26 записаны все дискретные значения (например, 100 ступеней) первого участка программы от b1 до а1. В блоке памяти 27 записаны нули. В регистре 22 хранится информация о максимуме а1, а в регистре 23 информация о минимуме b2. В компараторе 24 содержится информация а1-b2. Блок вычисления 25 определяет все промежуточные точки участка (а1…b2). В буферном регистре 30 записана величина a1-d1, в буферном регистре 31 - величина а1-b2. В рабочем регистре 32 записана разность а1-b1, которая подана на один из входов делителя 35, на второй вход делителя поступает частотный сигнал от генератора 34 опорной частоты. На выходе делителя 35 опорная частота поделена пропорционально величине а1-b1. В рабочем регистре 33 записан ноль. Деление на ноль запрещено, поэтому на выходе делителя 36 отсутствует частотный сигнал. Ключи 28, 37 закрыты. В регистре 8 записан номер второго восходящего участка N2 программы, в регистре 9 - номер первого восходящего участка N1 программы. С выхода аi блока памяти 14 на сумматор 20 подается величина а1, являющаяся максимумом первого участка программы. В регистре 16 записана величина а1, тем самым на первом выходе максимума программного задатчика также находится величина а1. С выхода накопителя ΣΔаi 15 на другой вход сумматора 20 подается нулевой сигнал. С выхода сумматора 20 на вход регистра 22 поступает сигнал а1+0. С выхода bi блока памяти 17 на сумматор 21 поступает сигнал b2, являющийся минимумом второго участка программы, с выхода накопителя ΣΔbi 18 на другой вход сумматора 21 подается нулевой сигнал. В регистре 19 записан ноль, тем самым, на первом выходе минимумов программного задатчика находится ноль. С выхода сумматора 21 на вход регистра 23 поступает сигнал b2+0. В соответствии с состоянием регистров 22 и 23 на входе максимума блока вычисления 25 будет величина первого локального максимума программы а1, на входе минимума блока вычисления 25 будет величина b2. На выходе блока 3 задания номера участка находится номер второго восходящего участка программы N2.

По сигналу «Пуск» триггер 2 переходит в состояние «d». Сигнал «d» открывает ключи 28, 37 в результате чего сигнал опорной частоты, поделенный на величину а1-b1, поступает на вход реверсивного счетчика 39. Коды с выхода реверсивного счетчика через открытый ключ 28 поступают на управляющие входы блока памяти 26. С выхода блока памяти 26 ординаты промежуточных точек первого участка программы (в виде электрических сигналов) поочередно поступают на вход следящего исполнительного привода 43, тем самым производится генерация первого участка программы. В процессе генерации первого участка программы по сигналу «d» (в начале программы это сигнал «ПУСК») в устройстве происходят следующие подготовительные операции для генерации последующих участков программы:

1. Сигнал «d» в формирователе импульсов 5 преобразуется в импульсный сигнал «d'». По сигналу «d'» в дешифратор считывания 10 с регистра 8 передается номер второго восходящего участка N2. Согласно номеру «i» восходящего участка N2 из блока памяти 14 выбирается значение аi - максимум второго восходящего участка (эталонная величина) (для простоты пояснения примем i=2), т.е.выбирается величина а,. Эта величина подается на вход сумматора 20, на другой вход сумматора 20 из накопителя ΣΔа2 15 подается величина, равная нулю, т.к. для коррекции еще не получено никакой корректирующей величины. По сигналу «d'» информация из блока вычисления 25 об участке (а1…b2) переписывается в блок памяти 27, а информация а1-b2 из буферного регистра 31 переписывается в регистр 33. Тем самым подготавливается генерация участка (а1…b2).

2. По импульсному сигналу «d"» вырабатываемому формирователем импульсов 6 в регистр 22 поступает ордината максимума à2. С выхода регистра 22 величина à2 поступает на вход максимума блока вычисления 25 (ордината минимума b2 на входе минимумов вычислителя была уже введена в процессе подготовки прибора к работе). При поступлении ординаты а2 вычислитель определяет все промежуточные значения программного сигнала на интервале (а2, b2). Компаратор 24 по сигналу «d"» вычисляет величину а2-b2 и по этому же сигналу записывает полученную разность в буферный регистр 30. Таким образом, в процессе генерации первого участка программы подготавливается информация для генерации второго восходящего участка, который с учетом нисходящего участка программы (а1, b2) будет третьим в программе (фиг.2). Такая последовательность подготовки информации сохраняется в течение всей работы устройства. Кроме того, по сигналу «d"» блок 3 задания номера участка программы подготавливает номер третьего восходящего участка программы N3 (с учетом нисходящих участков программы это будет пятый участок). Если генерируются детерминированные программы испытаний, то это номер выбирается из заданной последовательности, если генерируется псевдослучайная программа, то этот номер определяется генератором случайных чисел. После процедуры определения номера восходящего участка программы N3, он подается на информационный вход регистра 8, однако в него не записывается до поступления служебного сигнала «с'"», речь о котором пойдет ниже.

В момент окончания генерации первого участка программы (b1, а1) реверсивный счетчик 39 выдает сигнал переполнения, который через элементы «ИЛИ» 40, 1 поступает на вход триггера 2 и переводит его в состояние «с». Одновременно с сигналом «с» появляется сигнал «с'», который записывает в блок памяти 26 информацию об участке (b2, а2), в рабочий регистр 32 размаха этого участка - (а2-b2), а в регистр 19 - величину b2.

Сигнал с датчика нагрузки 42 поступает на вход экстрематора 41. Этот сигнал при устойчивой работе системы регулирования (следящего привода) отстает по фазе от программного сигнала (фиг.3), т.е. локальный максимум программного сигнала а1 появляется раньше локального максимума сигнала датчика нагрузки (обратной связи) ymax 1, поэтому чтобы вычислить поправку Δаi=аi-ymax i, на первом шаге коррекции локального максимума программы а1 из регистра 16 на один вход компаратора 44 поступает величина а1, а на другой вход - сигнал ymax 1 с выхода max экстрематора 41. В момент появления максимума сигнала датчика нагрузки ymax 1 экстрематор 41 вырабатывает импульсный сигнал «сэ», открывающий коммутатор 46, передающий Δa1=a1-ymax 1 в ячейку накопителя ΣΔа1 15. Кроме того, импульсный сигнал «сэ», соответствующий локальным максимумам, с экстрематора 41 через второй элемент задержки 49 преобразуется в сигнал «с"», который записывает в регистр 9 с регистра 8 номер следующего участка N2 программы. По этому же сигналу информация с регистра 9 передается в дешифраторы 12, 13.

Кроме регистра 9, импульсный сигнал «сэ» через третий элемент задержки 48 в виде сигнала «с'"» поступает на управляющий вход регистра 8 и с блока 3 задания номера участка программы записывает в регистр 8 номер участка программы, на единицу опережающий номер участка, записанного на регистр 9, т.е. в регистре 8 будет записан номер N3. Следует пояснить, что индексы 1, 2, 3,…, у номера N показывают порядковый номер только восходящих участков программы (нисходящим участкам блок задания 3 номеров не присваивает). По сигналу «с'"» в регистр 23 записывается минимум b3, в буферный регистр 31 записывается величина а2-b3, а в регистр 16 величина а2.

В процессе генерации второго участка программы (а1, b2), о котором говорилось выше, достигается первый минимум - b2. При этом реверсивный счетчик 39 выдает сигнал обнуления, который через элементы «ИЛИ» 40,1 переводит триггер 2 в состояние «d». По сигналу «d» открываются ключи 28, 37 и тем самым на вход следящего исполнительного привода 43 подключается блок памяти 26, в которой уже записана вся информация об участке (а2…b2) (см. выше подготовительные операции для генерации последующих участков программы, п.2). Начинается генерация участка (а2…b2) с частотой развертки этого участка, определяемой величиной a2-b2, записанной в регистре 32 (см. выше п.2). В результате фазового запаздывания сигнала обратной связи (как упоминалось выше) первый локальный минимум обратной связи ymin 1 появится на участке (а2…b2) позже программного минимума b2. Так как, в это время в регистре 19 хранится величина b2, то она находится и на первом входе компаратора 45, поэтому при поступлении величины ymin 2 на другой вход компаратора, на его выходе появится разность Δb2=b2-ymin 2. По импульсному сигналу «dэ» экстрематора, говорящему о достижении минимума сигнала датчика нагрузки, открывается коммутатор 47 и Δb2 за