Токовое зеркало

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве функционального узла различных устройств усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), стабилизаторах напряжения, компараторах). Технический результат заключается в повышении точности передачи по току. Токовое зеркало содержит входной (1) и выходной (2) транзисторы, базы которых объединены, а эмиттеры подключены к шине (3) первого источника питания, причем коллектор входного транзистора (1) связан со входом 4 токового зеркала, а коллектор выходного транзистора (2) соединен с выходом (5) токового зеркала. В схему введены первый (6) и второй (7) дополнительные транзисторы и вспомогательный инвертирующий усилитель тока (8), вход (9) которого соединен с коллектором первого (6) дополнительного транзистора, а выход (10) связан с выходом (5) токового зеркала, эмиттер второго дополнительного транзистора (7) соединен с эмиттером первого дополнительного транзистора 6 и подключен ко входу (4) токового зеркала, базы первого (6) и второго (7) дополнительных транзисторов соединены с цепью установления статического потенциала (11), причем коллектор второго дополнительного транзистора (7) связан с базами входного (1) и выходного (2) транзисторов. 4 з.п. ф-лы, 23 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве функционального узла различных устройств усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), стабилизаторах напряжения, компараторах).

Основой большинства современных операционных усилителей, стабилизаторов напряжения, компараторов являются так называемые «токовые зеркала» (повторители тока), которые по существу являются управляемыми источниками опорного тока [1-56]. В патентной литературе эти устройства с одним и тем же функциональным назначением присутствуют в классе H03F, а также классах G05F, Н03К МПК. Качественные показатели многих аналоговых устройств определяются параметрами токовых зеркал. Именно этим объясняется большое число патентов, посвященных данному подклассу функциональных узлов [1-56].

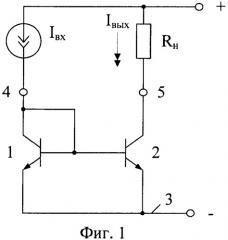

Ближайшим прототипом (фиг.1) заявляемого устройства является токовое зеркало, описанное в патенте фирмы Analog Devices (США) 6.573.795 (фиг.1), содержащее входной 1 и выходной 2 транзисторы, базы которых объединены, а эмиттеры подключены к шине 3 первого источника питания, причем коллектор входного транзистора 1 связан со входом 4 токового зеркала, а коллектор выходного транзистора 2 соединен с выходом 5 токового зеркала. Кроме этого данное техническое решение описано в патентах США №3.906.386, 4.158.178, 4.352.057, 4.965.510, 4.700.144, 3.950.708, 6.163.216, 5.220.289, 6.429.744.

Существенный недостаток известного токового зеркала состоит в том, что оно не обеспечивает высокую точность передачи по току в том случае, если статические потенциалы на коллекторах входного 1 и выходного 2 транзисторов существенно отличаются друг от друга. Следует отметить, что такой режим работы токовых зеркал характерен при их использовании в схемах многих операционных усилителей (ОУ) с типовой архитектурой. Кроме этого погрешность передачи входного тока в схеме фиг.1 зависит от коэффициента усиления по току базы транзистора 2 (β2). Вследствие этих недостатков известного устройства напряжение смещения нуля ОУ на его основе измеряется единицами милливольт. В большинстве случаев это неприемлемо.

Основная цель предлагаемого изобретения состоит в повышении точности передачи по току токового зеркала и, как следствие, в уменьшении напряжения смещения нуля Uсм и повышении коэффициента ослабления входного синфазного сигнала (Кос.сф) в операционных усилителях на его основе. Дополнительная цель - повышение на 1-2 порядка коэффициента усиления по напряжению (Ку) ОУ.

Поставленная цель достигается тем, что в токовом зеркале фиг.1, содержащем входной 1 и выходной 2 транзисторы, базы которых объединены, а эмиттеры подключены к шине 3 первого источника питания, причем коллектор входного транзистора 1 связан со входом 4 токового зеркала, а коллектор выходного транзистора 2 соединен с выходом 5 токового зеркала, предусмотрены новые элементы и связи - в схему введены первый 6 и второй 7 дополнительные транзисторы и вспомогательный инвертирующий усилитель тока 8, вход 9 которого соединен с коллектором первого 6 дополнительного транзистора, а выход 10 связан с выходом 5 токового зеркала, эмиттер второго дополнительного транзистора 7 соединен с эмиттером первого дополнительного транзистора 6 и подключен ко входу 4 токового зеркала, базы первого 6 и второго 7 дополнительных транзисторов соединены с цепью установления статического потенциала 11, причем коллектор второго дополнительного транзистора 7 связан с базами входного 1 и выходного 2 транзисторов.

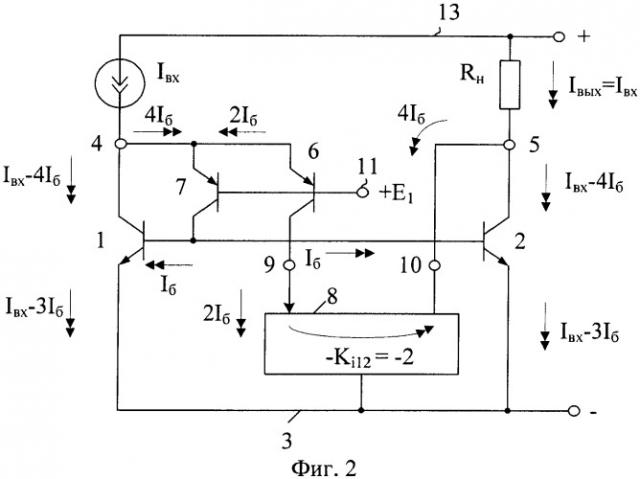

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

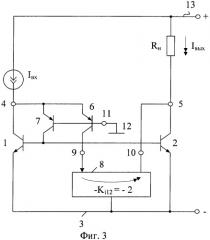

На фиг.3 показана схема токового зеркала фиг.2 в соответствии с п.2 и п.3 формулы изобретения для случая, когда в качестве цепи установления статического потенциала 11 используется общая шина 12 первого 3 и второго 13 источников питания. При этом входной токовый сигнал моделируется источником Iвх, а свойства нагрузки - двухполюсником R4.

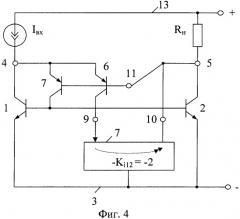

На фиг.4 изображен другой вариант построения токового зеркала (п.4 формулы изобретения) для случая, когда в качестве цепи установления статического потенциала 11 используется выход 5 токового зеркала.

Схема фиг.5 соответствует п.5 формулы изобретения. Она включает дополнительный неинвертирующий усилитель тока 14, у которого Кi=1.

На фиг.6 в качестве примера представлена схема «перегнутого» каскодного усилителя на базе заявляемого токового зеркала.

На фиг.7 показана схема операционного усилителя на базе токового зеркала - прототипа в среде компьютерного моделирования РSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь напряжение смещения нуля Uсм=-4,4 мВ.

На фиг.8 в среде PSpice представлена схема операционного усилителя на основе заявляемого токового зеркала фиг.5, на базе которой производилось измерение величины напряжения смещения нуля. Здесь Uсм=0,44 мВ (без учета случайного разброса параметров элементов).

На фиг.9 показаны графики частотной зависимости коэффициента усиления по напряжению ОУ фиг.7 и фиг.8. Они показывают, что предлагаемое токовое зеркало увеличивает Ку на 48 дБ, т.е. более чем в 100 раз.

На фиг.10 представлена схема токового зеркала-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.11 - зависимость его выходного тока от входного. Фиг.12 иллюстрирует зависимость относительной погрешности передачи тока от численных значений Iвх.

На фиг.13 показана схема токового зеркала, соответствующего фиг.4, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.14 и фиг.15 - его основные характеристики.

На фиг.16 приведена схема токового зеркала, соответствующего фиг.3, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.17 - зависимость относительной погрешности передачи тока от численных значений Iвх.

На фиг.18 приведена другая модификация схемы токового зеркала, соответствующего фиг.4, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.19 и фиг.20 - его основные характеристики.

На фиг.21 приведена другая модификация схемы токового зеркала, соответствующего фиг.3, в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.22 и фиг.23 - его основные характеристики.

Следует заметить, что схемы фиг.21, фиг.18 отличаются от других более низкими значениями относительной погрешности передачи тока за счет введения симметрирующих p-n переходов в коллекторную цепь транзистора 1.

Токовое зеркало фиг.2 содержит входной 1 и выходной 2 транзисторы, базы которых объединены, а эмиттеры подключены к шине 3 первого источника питания, причем коллектор входного транзистора 1 связан со входом 4 токового зеркала, а коллектор выходного транзистора 2 соединен с выходом 5 токового зеркала. В схему введены первый 6 и второй 7 дополнительные транзисторы и вспомогательный инвертирующий усилитель тока 8, вход 9 которого соединен с коллектором первого 6 дополнительного транзистора, а выход 10 связан с выходом 5 токового зеркала, эмиттер второго дополнительного транзистора 7 соединен с эмиттером первого дополнительного транзистора 6 и подключен ко входу 4 токового зеркала, базы первого 6 и второго 7 дополнительных транзисторов соединены с цепью установления статического потенциала 11, причем коллектор второго дополнительного транзистора 7 связан с базами входного 1 и выходного 2 транзисторов.

Во всех предлагаемых схемах коэффициент передачи по току вспомогательного инвертирующего усилителя тока 8 близок к двум единицам.

В схеме фиг.3. в качестве цепи установления статического потенциала 11 используется общая шина 12 первого 3 и второго 13 источников питания.

В схеме фиг.4 в качестве цепи установления статического потенциала 11 используется выход 5 токового зеркала.

В схеме фиг.5 выход 10 вспомогательного инвертирующего усилителя тока 8 связан с выходом 5 токового зеркала через дополнительный неинвертирующий усилитель тока 14.

Рассмотрим работу заявляемого устройства фиг.2.

В статическом режиме в схеме фиг.2 устанавливаются следующие токи

Iк1=Iвх-4Iб,

Iэ1=Iк1+Iб=Iвх-3Iб,

Iк6=2Iб, I10=Ki122Iб=4Iб,

Iэ2=Iэ1=Iвх-3Iб,

Iк2=Iэ2-Iб=Iвх-4Iб,

Iвых=Iк2+I10=Iвх,

где Кi12=2 - модуль коэффициента усиления по току инвертирующего усилителя тока 8;

Iб - ток базы; Iк- ток коллектора; I э- ток эмиттера транзисторов; Iвх- входной ток.

Таким образом, без учета эффекта Эрли транзистора 6 коэффициент передачи по току предлагаемого устройства равен единице, так как:

Iвых=Iвх.

В устройстве-прототипе данная составляющая коэффициента передачи определяется формулой:

,

где β2=5÷20 - коэффициент усиления по току базы транзистора 2.

Таким образом, заявляемое устройство более качественно выполняет функции токового зеркала и может применяться в аналоговых устройствах по данному функциональному назначению. При этом единичный коэффициент передачи по току обеспечивается в широком диапазоне изменения Iвx (два-три порядка).

Особенность предлагаемого токового зеркала состоит также в том, что в нем обеспечивается «выравнивание» статических напряжений на входе 4 и выходе 5 за счет соответствующего выбора напряжения цепи установления статического потенциала 11. Это также существенно уменьшает Uсм. Кроме этого, подключение базы транзисторов 6 и 7 к выходу 5 токового зеркала создает условия для уменьшения погрешности токового зеркала за счет взаимной компенсации эффектов Эрли в транзисторах 1 и 2.

Замечательная особенность токового зеркала фиг.4 состоит также в том, что при его использовании в операционных усилителях коэффициент усиления по напряжению (Ку) повышается более чем на два порядка (фиг.9). Это связано с эффектом взаимной компенсации влияния на коэффициент усиления паразитных выходных проводимостей транзисторов 1 и 2 в выходном узле 5 токового зеркала.

За счет предлагаемого токового зеркала в ОУ на его основе также существенно повышается коэффициент ослабления синфазных сигналов (Кос.сф) и коэффициент подавления помехи по питанию (Кпп). Этот эффект объясняется тем, что коэффициент передачи по току предлагаемого токового зеркала более близок к единице, чем в известном устройстве. В целом это повышает Кос.сф и Кпп, уменьшает Uсм.

Полученные выше выводы подтверждаются результатами моделирования предлагаемой схемы в среде PSpice.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №1.329.639

2. Патент США №3.681.623

3. Патент США №3.813.607

4. Патент США №3.835.410

5. Патент США №4.008.441, H03f3/16

6. Патент США №4.013.973

7. Патент США №4.030.044 (фиг.3)

8. Патент США №4.057.763

9. Патент США №4.095.189

10. Патент США №4.117.417

11. Патент США №4.241.315

12. Патент США №4.345.213

13. Патент США №4.412.186, H03f3/04

14. Патент США №4.462.005, H03f3/04

15. Патент США №4.471.236

16. Патент США №4.473.794

17. Патент США №4.567.444

18. Патент США №4.591.804, H03f3/04

19. Патент США №4.769.619

20. Патент США №4.855.686

21. Патент США №4.879.524, H03f3/26

22. Патент США №4.897.614

23. Патент США №4.937.515, G05f3/26

24. Патент США №4.990.864

25. Патент США №5.053.718

26. Патент США №5.079.518, Н03К 3/16

27. Патент США №5.164.658

28. Патент США №5.357.188, G05f3/26

29. Патент США №5.373.253

30. Патент США №5.394.079, G05f3/16

31. Патент США №5.399.991

32. Патент США №5.512.815, G05f3/16

33. Патент США №5.572.114

34. Патент США №5.633.612

35. Патент США №5.721.512

36. Патент США №5.933.055

37. Патент США №5.969.574

38. Патент США №5.986.507

39. Патент США №6.016.050

40. Патент США №6.570.438

41. Патент США №6.573.795

42. Патент США №6.586.918

43. Патент США №6.606.001

44. Патент США №6.291.977

45. Патент США №6.300.803

46. Патент США №6.528.981

47. Патент США №6.630.818

48. Патент США №6.633.198

49. Патент США №6.639.452

50. Патент США №6.657.481

51. Патент США №6.677.807

52. Патент США №6.680.605

53. Патент США №6.816.014

54. Патент РФ RU 2193273

55. Патентная заявка США 2004/081688

56. Патентная заявка США 2003/0030492

1. Токовое зеркало, содержащее входной (1) и выходной (2) транзисторы, базы которых объединены, а эмиттеры подключены к шине (3) первого источника питания, причем коллектор входного транзистора (1) связан со входом (4) токового зеркала, а коллектор выходного транзистора (2) соединен с выходом (5) токового зеркала, отличающееся тем, что в схему введены первый (6) и второй (7) дополнительные транзисторы и вспомогательный инвертирующий усилитель тока (8), вход (9) которого соединен с коллектором первого (6) дополнительного транзистора, а выход (10) связан с выходом (5) токового зеркала, эмиттер второго дополнительного транзистора (7) соединен с эмиттером первого дополнительного транзистора (6) и подключен ко входу (4) токового зеркала, базы первого (6) и второго (7) дополнительных транзисторов соединены с цепью установления статического потенциала (11), причем коллектор второго дополнительного транзистора (7) связан с базами входного (1) и выходного (2) транзисторов.

2. Устройство по п.1, отличающееся тем, что коэффициент передачи по току вспомогательного инвертирующего усилителя тока (8) близок к двум единицам.

3. Устройство по п.1, отличающееся тем, что в качестве цепи установления статического потенциала (11) используется общая шина (12) первого (3) и второго (13) источников питания.

4. Устройство по п.1, отличающееся тем, что в качестве цепи установления статического потенциала (11) используется выход (5) токового зеркала.

5. Устройство по п.1, отличающееся тем, что выход (10) вспомогательного инвертирующего усилителя тока (8) связан с выходом (5) токового зеркала через дополнительный неинвертирующий усилитель тока (14).