Система доступа к памяти с адаптивно подстраиваемой скоростью работы

Иллюстрации

Показать всеСистема содержит шину общего доступа, внешнюю память, подключенную к шине общего доступа, модуль управления сигналом синхронизирующей тактовой частоты, основной мастер-модуль, сохраняющий исключительный доступ к памяти при работе системы в режиме сохранения энергии, мастер-модули, подключенные к шине и генерирующие запросы на доступ к ней, шинный арбитр. Для автоматического выбора скорости работы она снабжена счетным устройством полезных тактов шины, счетным устройством полных тактов шины и устройством сравнения и управления тактовой частотой шинного арбитра и внешней памяти. 2 ил.

Реферат

Изобретение относится к вычислительной технике, а именно к области обработки потоковых данных в многопроцессорной системе на кристалле.

Область обработки потоковых данных (компрессия, декомпрессия видео) является быстроразвивающимся направлением. Возрастают разрешающие способности оборудования (камеры и экраны высокой четкости) и качество обработки изображения. При этом устройства становятся компактнее, возрастают требования к энергопотреблению изделия, а средства их удовлетворения все еще недостаточны в полной мере.

Известны технические решения [1, 2], выполняющие доступ к общей внешней памяти без регулировки скорости обращения, что является существенным недостатком данного решения систем, т.к. они обладают высокой потребляемой мощностью, что ухудшает потребительские свойства системы.

Наиболее близким техническим решением является система, использующая шинный арбитр для выключения [3], включающая:

- шину общего доступа,

- внешнюю память, подключенную к шине общего доступа,

- модуль управления сигналом синхронизирующей тактовой частоты,

- основной мастер-модуль, сохраняющий исключительный доступ к памяти при работе системы в режиме сохранения энергии,

- мастер-модули, подключенные к шине и генерирующие запросы на доступ к ней,

- выключающий мастер-модуль,

- шинный арбитр.

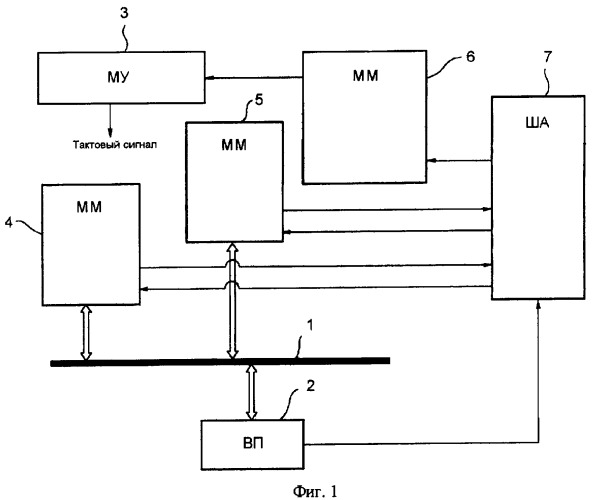

Функциональная схема прототипа [3] представлена на фигуре 1.

На представленной схеме сделаны обозначения, где: 1 - шина общего доступа, 2 - внешняя память, 3 - модуль управления сигналом синхронизирующей тактовой частоты, 4 - основной мастер-модуль, сохраняющий исключительный доступ к памяти при работе системы в режиме сохранения энергии, 5 - мастер-модули, подключенные к шине и генерирующие запросы на доступ к ней, 6 - выключающий мастер-модуль, 7 - шинный арбитр.

Как следует из описания системы прототипа [3] и из функциональной схемы, представленной на фиг.1, система имеет недостатки:

1. Активность на шине и определения условий входа системы в режим сохранения энергии наблюдаются программно внешними средствами. Внешнее управление скоростью существенно снижает быстродействие и скорость реагирования системы на изменения.

2. В режиме сохранения энергии право доступа на шину принадлежит исключительно одному мастер-модулю 4, шина не используется, что существенно снижает функциональные возможности системы.

Задачей изобретения является нахождение технического решения, заключающегося в автоматическом выборе скорости работы системы с внешней памятью, повышающем скорость настройки системы под общий уровень нагрузки, и обеспечении доступа на шину всех мастер-модулей во всех режимах работы в результате добавления в систему счетного устройства полезных тактов шины, счетного устройства полных тактов шины и устройства сравнения и управления.

Для достижения названного технического результата в систему, использующую шинный арбитр для выключения [3], содержащую:

- шину общего доступа,

- внешнюю память, подключенную к шине общего доступа,

- модуль управления сигналом синхронизирующей тактовой частоты,

- основной мастер-модуль, сохраняющий исключительный доступ к памяти при работе системы в режиме сохранения энергии,

- мастер-модули, подключенные к шине и генерирующие запросы на доступ к ней,

- шинный арбитр

включают блоки, являющиеся отличительными признаками изобретения:

- счетное устройство полезных тактов шины,

- счетное устройство полных тактов шины,

- устройство сравнения и управления тактовой частотой шинного арбитра и внешней памяти.

Проведенные патентные исследования показали, что совокупность признаков предлагаемого изобретения является новой, что доказывает новизну заявляемого прибора.

Кроме того, патентные исследования показали, что в литературе отсутствуют данные, показывающие влияние отличительных признаков заявляемого изобретения на достижение технического результата, что подтверждает изобретательский уровень предлагаемой конструкции прибора.

Данная совокупность отличительных признаков позволяет достичь названный технический результат.

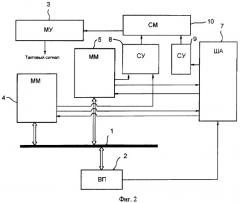

Функциональная схема устройства согласно предполагаемому изобретению иллюстрируется на фиг.2.

Устройство, представленное на фиг.2, содержит: 1 - шину, 2 - внешнюю память, 3 - модуль управления, 4 - основной мастер-модуль, 5 - мастер-модули, 7 - шинный арбитр, 8 - счетное устройство полезных тактов шины, 9 - счетное устройство полных тактов шины, 10 - устройство сравнения и управления тактовой частотой шинного арбитра и внешней памяти.

В предлагаемой нами системе, где нагрузка на общий массив памяти меняется в зависимости от режима, можно значительно сэкономить энергию, уменьшив скорость работы с общей внешней памятью до минимально необходимого для данного режима. Также возможны устойчивые продолжительные изменения в уровне нагрузки на общую внешнюю память при работе в выбранном режиме.

Логика работы шины доступа к общей внешней памяти с адаптивной подстраиваемой скоростью работы рассмотрена ниже.

Начальные условия: устанавливается максимальная тактовая частота внешней памяти и шинного арбитра. Система обработки потоковых данных (многопроцессорная системе на кристалле) работает согласно своему алгоритму. Каждый мастер-модуль запрашивает доступ к внешней памяти и осуществляет доступ к ней через шинный арбитр. Во время доступа каждого мастер-модуля счетным устройством полезных тактов шины (8) суммируется общая активность всех устройств «K». В то же время осуществляется подсчет «k» полных тактов шины (полной возможной пропускной способности шины и внешней памяти) счетным устройством полных тактов шины (9).

Устройство сравнения (10) находит отношение полезной скорости обменов «K» на шине к полной возможной скорости «k» на данной (максимальной) тактовой частоте. Отношение будет меньше (или равно) единицы.

При меньшем отношении (неполной загрузке шины) сравнивающий модуль устанавливает другое (меньшее) значение тактовой частоты шинного арбитра и внешней памяти.

Сетка значений «N» тактовых частот «F(N)» определяется как пошаговое увеличение минимальной базовой тактовой частоты системы. Так, например, для системы обработки видео, использующей стандартную внешнюю SDRAM память с максимальной тактовой частотой работы до 200 МГц, предлагается использовать шаг сетки частот, равный 27 МГц (кратное частоте вывода и приема входных данных значение).

В данной системе шаг сетки частот будет следующий:

| Номер шага сетки (N) | Значение тактовой частоты F(N) (МГц) | Отношение Mmin(N)=F(N)/F(N+1) |

| 1 | 27 | 0,5 |

| 2 | 54 | 0,66 |

| 3 | 81 | 0,75 |

| 4 | 108 | 0,8 |

| 5 | 135 | 0,833 |

| 6 | 162 | 0,857 |

| 7 | 189 | 0,875 |

| 8 | (216) | - |

В устройстве сравнения и управления тактовой частотой шинного арбитра и внешней памяти (10) сравниваются значения и отношения K(N) и k(N) и, если K(N)/k(N)<Mmin(N), то выбирается следующее меньшее согласно сетке значение тактовой частоты, иначе, при K(N)/k(N)=1 выбирается следующее большее значение тактовой частоты. Если же Mmin(N)=<K(N)/k(N)<1, то значение сетки тактовой частоты не меняется.

Таким образом, скорость работы с внешней памятью адаптивно регулируется под уровень загрузки шины, минимизируется потребляемая мощность при работе внешней памяти на меньших скоростях.

Пример реализации, описанный выше, является частным случаем. Предполагаемая система может использоваться для задач любого другого типа не выходя за пределы патентных притязаний.

Литература

1. Philips semiconductors, Integrated MPEG AVGD decoders SAA7215; SAA7216; SAA7221, Preliminary specification, 2001 Mar 28, page 2. www.platan.ru/pdf/1dist/philips/SAA7215_7216_7221_

2. Robert Cravotta, 2002 DSP directory, www.ednmag.com, paper edn040402, April 2002 N4, page 56, TEXAS INSTRUMENTS' TMS320DSCX FAMILY.

3. US Patent Application 20070067652 System using bus arbiter to power down.

Система доступа к памяти с адаптивно подстраиваемой скоростью работы, содержащая шину общего доступа, внешнюю память, подключенную к шине общего доступа, модуль управления сигналом синхронизирующей тактовой частоты, основной мастер-модуль, сохраняющий исключительный доступ к памяти при работе системы в режиме сохранения энергии, мастер-модули, подключенные к шине и генерирующие запросы на доступ к ней, шинный арбитр, отличающаяся тем, что она снабжена счетным устройством полезных тактов шины, счетным устройством полных тактов шины и устройством сравнения и управления тактовой частотой шинного арбитра и внешней памяти.