Двухтактный транзисторный преобразователь

Иллюстрации

Показать всеИзобретение относится к преобразовательной технике, и может быть использовано в автономных источниках вторичного электропитания, и направлено на повышение быстродействия двухтактного транзисторного преобразователя в режиме заряда емкости выходного фильтра с повышением КПД и надежности его работы. Технический результат заключается в повышении быстродействия двухтактного преобразователя в режиме заряда емкости выходного фильтра с повышением КПД и надежности его работы. Сущность достигается тем, что в двухтактный транзисторный преобразователь введены первый и второй предварительные усилители, выходы которых соединены с первым и вторым вновь введенными входами блока управления преобразователем, третий вновь введенный вход которого соединен с выходом порогового элемента, также датчик тока, выходной фильтр, выходной выпрямитель и инвертор. 4 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к преобразовательной технике и может быть использовано в автономных источниках вторичного электропитания, преимущественно в электроприводах мощностью более 1 кВт.

Известен двухтактный транзисторный преобразователь с трансформаторным разделением цепей (В.С.Моин. Стабилизированные транзисторные преобразователи. - М.: Энергоатомиздат, 1986. 376 с., рис 4.15.), состоящий из двухтактного инвертора с выходным трансформатором, во вторичную цепь которого включен выпрямитель и дроссель, ограничивающий ток заряда выходной емкости в процессе пуска преобразователя.

Известен также двухтактный транзисторный преобразователь с токовой обратной связью (патент РФ №2061293), содержащий трансформатор с двумя обмотками со средней точкой, два транзистора, источник питания, нагрузку, диод, резистор и конденсатор, ток заряда которого в процессе пуска ограничен сопротивлением в цепи перехода Б-Э транзистора.

В подобных преобразователях не контролируется ни максимальное, ни среднее значение тока заряда емкости выходного фильтра. Для работы транзисторов в безопасной области процесс заряда емкости выходного фильтра затягивается. Это снижает быстродействие преобразователя как элемента системы управления, например, электропривода.

Наиболее близким по технической сущности к заявляемому решению является двухтактный транзисторный конвертор (патент РФ №2110133), выбранный за прототип, содержащий блок защиты с узлом задержки повторного включения, пороговый и ключевой элементы. В момент заряда выходной емкости узел задержки определяет периодичность, с которой осуществляется релейно-пусковой режим работы.

Недостатком данного двухтактного транзисторного конвертора являются паузы в зарядном токе, длительность которых определяется времязадающей цепью. Паузы в токе затягивают пуск конвертора, снижают быстродействие преобразователя как элемента системы управления, увеличивают переменную составляющую тока через конденсаторы входного и выходного фильтров, создают дополнительные перенапряжения в преобразователе, что снижает его КПД и надежность.

Изобретение направлено на повышение быстродействия двухтактного преобразователя в режиме заряда емкости выходного фильтра с повышением КПД и надежности его работы.

Это достигается тем, что в двухтактный транзисторный преобразователь, содержащий инвертор на силовых ключах, выходной выпрямитель, выходной фильтр, блок управления преобразователем, датчик тока, пороговый элемент, введены первый и второй предварительные усилители, причем датчик тока установлен в эмиттерных цепях силовых ключей инвертора и своим выходом соединен с входом порогового элемента, выход которого соединен с вновь введенным третьим входом блока управления преобразователем, первый и второй вновь введенные входы блока управления преобразователем соединены с соответствующими выходами первого и второго предварительных усилителей, а также с управляющими входами соответствующих силовых ключей инвертора, первый и второй выходы блока управления преобразователем соединены с соответствующими входами первого и второго предварительных усилителей.

Для обеспечения работоспособности преобразователя на первый и второй предварительные усилители, блок управления преобразователем, пороговый элемент, датчик тока подаются питающие напряжения от отдельного источника питания.

В соответствии с возможным вариантом практической реализации заявляемого технического решения вышеупомянутый блок управления преобразователем содержит первый и второй ограничители напряжения, первый, второй и третий триггеры Шмитта с объединением двух входов по & (2-И-НЕ), первый и второй инверторы, первый и второй трехвходовые элементы логического сложения (3-ИЛИ-НЕ), интегратор, диод и первый резистор, при этом входы первого и второго ограничителей напряжения являются первым и вторым входами блока управления преобразователем; выход первого ограничителя напряжения соединен со вторым входом первого триггера Шмитта с объединением двух входов по & (2-И-НЕ) и первым входом первого трехвходового элемента логического сложения (3-ИЛИ-НЕ); выход второго ограничителя напряжения соединен со вторым входом второго триггера Шмитта с объединением двух входов по & (2-И-НЕ) и первым входом второго трехвходового элемента логического сложения (3-ИЛИ-НЕ); первый вход второго триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с первым входом первого триггера Шмитта с объединением двух входов по & (2-И-НЕ), а также с третьими входами первого и второго трехвходовых элементов логического сложения (3-ИЛИ-НЕ) и является третьим входом блока управления преобразователем; выход первого триггера Шмитта с объединением двух входов по & (2-И-НЕ) через первый инвертор соединен с анодом диода, катод которого соединен со вторым входом третьего триггера Шмитта с объединением двух входов по & (2-И-НЕ), второй вход которого также через первый резистор соединен с выходом интегратора; выход второго триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с первым входом третьего триггера Шмитта с объединением двух входов по & (2-И-НЕ), выход третьего триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с входом второго инвертора и вторым входом первого трехвходового элемента логического сложения (3-ИЛИ-НЕ); выход второго инвертора соединен с входом интегратора и вторым входом второго трехвходового элемента логического сложения (3-ИЛИ-НЕ); выходы первого и второго трехвходовых элементов логического сложения (3-ИЛИ-НЕ) являются соответственно первым и вторым выходами блока управления преобразователем.

Вариант исполнения порогового элемента, для практической реализации заявляемого технического решения, представляет собой последовательно соединенные между собой резистивно-емкостной фильтр, четвертый триггер Шмитта с объединением двух входов по & (2-И-НЕ) и третий инвертор, причем первый и второй входы четвертого триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединены между собой и через второй резистор соединены с его выходом, при этом вход резистивно-емкостного фильтра является входом порогового элемента, а выход третьего инвертора является его выходом.

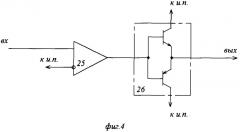

Вариант исполнения каждого предварительного усилителя представляет собой последовательно соединенные между собой компаратор и двухтактный усилитель мощности, причем неинвертирующий вход компаратора является входом предварительного усилителя, а выход двухтактного усилителя мощности является его выходом.

Вариант исполнения силового ключа инвертора, для практической реализации заявляемого технического решения, представляет собой последовательно соединенные между собой комплементарный ключ и биполярный транзистор, причем комплементарный ключ содержит p-канальный и n-канальный полевые транзисторы, при этом управляющим входом каждого из силовых ключей инвертора являются соединенные между собой затворы полевых транзисторов из состава комплементарного ключа, а коллектор биполярного транзистора является его выходом; истоки n-канального и p-канального полевых транзисторов соединены между собой и соединены с базой биполярного транзистора, сток n-канального полевого транзистора соединен с коллектором биполярного транзистора, сток p-канального полевого транзистора и эмиттер биполярного транзистора соединены с источником питания.

Материалы заявки поясняются графическими материалами, где:

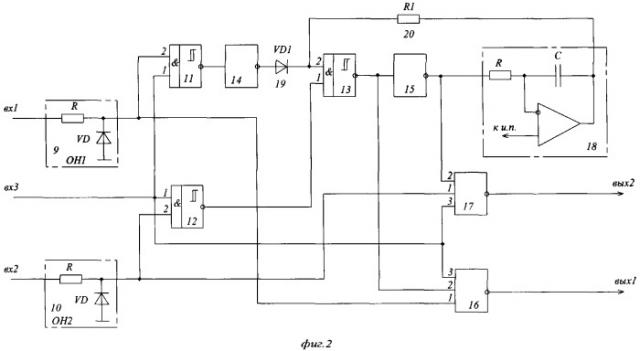

на фиг.1 представлена структурная схема двухтактного транзисторного преобразователя;

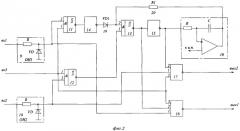

на фиг.2 - вариант исполнения блока управления преобразователем;

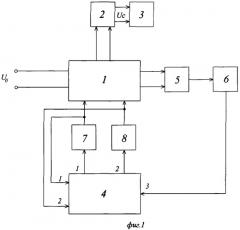

на фиг.3 - вариант исполнения порогового элемента;

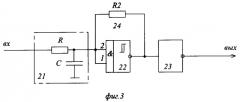

на фиг.4 - вариант исполнения предварительного усилителя;

на фиг.5 - вариант исполнения силового ключа инвертора;

на фиг.6 - осциллограммы работы двухтактного транзисторного преобразователя.

Двухтактный транзисторный преобразователь (фиг.1) содержит инвертор на силовых ключах 1, выходной выпрямитель 2, выходной фильтр 3, блок управления преобразователем 4, датчик тока 5, пороговый элемент 6, первый 7 и второй 8 предварительные усилители, причем датчик тока 5 установлен в эмиттерных цепях силовых ключей инвертора 1 и своим выходом соединен с входом порогового элемента 6, выход которого соединен с вновь введенным третьим входом блока управления преобразователем 4, первый и второй вновь введенные входы блока управления преобразователем 4 соединены с соответствующими выходами первого 7 и второго 8 предварительных усилителей, а также с управляющими входами соответствующих силовых ключей инвертора 1, первый и второй выходы блока управления преобразователем 4 соединены с соответствующими входами первого 7 и второго 8 предварительных усилителей.

Блок управления преобразователем (БУП) 4 (фиг.2) включает в себя первый 9 и второй 10 ограничители напряжения, первый 11, второй 12 и третий 13 триггеры Шмитта с объединением двух входов по & (2-И-НЕ), первый 14 и второй 15 инверторы, первый 16 и второй 17 трехвходовые элементы логического сложения (3-ИЛИ-НЕ), интегратор 18, диод 19, первый резистор 20, при этом входы первого 9 и второго 10 ограничителей напряжения являются первым и вторым входами блока управления преобразователем 4; выход первого 9 ограничителя напряжения соединен со вторым входом первого 11 триггера Шмитта с объединением двух входов по & (2-И-НЕ) и первым входом первого 16 трехвходового элемента логического сложения (3-ИЛИ-НЕ); выход второго 10 ограничителя напряжения соединен со вторым входом второго 12 триггера Шмитта с объединением двух входов по & (2-И-НЕ) и первым входом второго 17 трехвходового элемента логического сложения (3-ИЛИ-НЕ); первый вход второго 12 триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с первым входом первого 11 триггера Шмитта с объединением двух входов по & (2-И-НЕ), а также с третьими входами первого 16 и второго 17 трехвходовых элементов логического сложения (3-ИЛИ-НЕ) и является третьим входом блока управления преобразователем 4; выход первого 11 триггера Шмитта с объединением двух входов по & (2-И-НЕ) через первый инвертор 14 соединен с анодом диода 19, катод которого соединен со вторым входом третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ), второй вход которого также через первый резистор 20 соединен с выходом интегратора 18; выход второго 12 триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с первым входом третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ), выход которого соединен с входом второго 15 инвертора и вторым входом первого 16 трехвходового элемента логического сложения (3-ИЛИ-НЕ); выход второго 15 инвертора соединен с входом интегратора 18 и вторым входом второго 17 трехвходового элемента логического сложения (3-ИЛИ-НЕ); выходы первого 16 и второго 17 трехвходовых элементов логического сложения (3-ИЛИ-НЕ) являются соответственно первым и вторым выходами БУП 4.

Пороговый элемент (ПЭ) 6 (фиг.3) выполнен в виде последовательно соединенных между собой резистивно-емкостного фильтра 21, четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ), третьего инвертора 23, причем первый и второй входы четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединены между собой и через второй 24 резистор соединены с его выходом, при этом вход резистивно-емкостного фильтра 21 является входом порогового элемента 6, а выход третьего инвертора 23 является его выходом.

Каждый из предварительных усилителей (ПУ) 7 или 8 (фиг.4) выполнен в виде последовательно соединенных между собой компаратора 25 и двухтактного усилителя мощности (ДУМ) 26, причем неинвертирующий вход компаратора 25 является входом предварительного усилителя, а выход ДУМ 26 является его выходом.

Каждый из силовых ключей (СК) инвертора 1 (фиг.5) выполнен в виде последовательно соединенных между собой комплементарного ключа 27 и биполярного транзистора 28, причем комплементарный ключ 27 содержит р-канальный 29 и n-канальный 30 полевые транзисторы, при этом управляющим входом каждого из СК инвертора 1 являются соединенные между собой затворы полевых транзисторов 29 и 30 из состава комплементарного ключа 27, а коллектор биполярного транзистора 28 является его выходом; истоки n-канального и p-канального полевых транзисторов соединены между собой и соединены с базой биполярного транзистора 28, сток n-канального полевого транзистора 30 соединен с коллектором биполярного транзистора 28, сток p-канального полевого транзистора 29 и эмиттер биполярного транзистора 28 с источником питания.

Двухтактный транзисторный преобразователь работает следующим образом. Он преобразует с нерегулируемым коэффициентом постоянное напряжение одного уровня U0 (фиг.1) на входе в постоянное напряжение другого уровня Uc (фиг.1), формирующееся на емкости выходного фильтра 3. Это происходит благодаря промежуточному преобразованию входного напряжения U0 в переменное с помощью инвертора на силовых ключах 1, выполненного по схеме с нулевым выводом [1]. Переменное напряжение трансформируется силовым трансформатором инвертора 1, выпрямляется выходным выпрямителем 2 и сглаживается выходным фильтром 3. Преобразователь может работать в двух режимах: с нагрузкой, не превышающей номинальную, и в режиме токоограничения. Частный случай режима токоограничения - режим заряда емкости выходного фильтра 3. В каждом режиме формирование управляющих импульсов для СК инвертора 1 осуществляется БУП 4 по определенному алгоритму.

Рассмотрим формирование сигналов на управляющих входах каждого из СК инвертора 1 U5(t) и U6(t) (фиг.6) соответственно в режиме номинальной нагрузки. Третий 13 триггер Шмитта с объединением двух входов по & (2-И-НЕ) (фиг.2), второй инвертор 15, интегратор 18, первый резистор 20 в БУП 4 образуют генератор последовательности прямоугольных импульсов со скважностью 2, периодом Т (фиг.6), т.е. равными длительностями импульса и паузы, которая формируется на первом U3(t) и втором U4(t) выходах БУП 4. Генерация этих импульсов осуществляется за счет подачи преобразованного выходного напряжения U1(t) третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ) на его второй вход в фазе, способствующей возникновению колебаний. Это происходит следующим образом. Сигнал прямоугольной формы с выхода второго 15 инвертора путем интегрирования преобразуется в сигнал пилообразной формы U2(t) посредством интегратора 18 (фиг.2) и поступает через первый резистор 20 на второй вход третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ), и в моменты достижения пилообразным напряжением U2(t) (фиг.6) значений U min и U max (верхний и нижний пороги переключения триггера Шмитта) третий 13 триггер Шмитта с объединением двух входов по & (2-И-НЕ) изменяет логическое состояние своего выхода на противоположное, формируя на нем последовательность прямоугольных импульсов. С первого и второго выходов БУП 4 на управляющие входы инвертора 1 поступают сигналы, определяющие длительность включения каждого из них, при этом длительность "подъема" (интервалы t1-t2, t3-t4) пилообразного сигнала определяет время подачи открывающего импульса на один из СК инвертора 1, длительность "спада" (интервалы t0-t1, t2-t3) пилообразного сигнала определяет время подачи открывающего импульса на другой СК инвертора 1.

Сигналы на выходах БУП 4 представляют собой результат выполнения следующих логических операций:

Эти функции реализуются первым 15 и вторым 16 трехвходовыми элементами логического сложения (3-ИЛИ-НЕ). Как видно из (1), формирование открывающих импульсов на выходах БУП 4 возможно только в отсутствие сигнала на третьем входе БУП 4 U9(t) (фиг.6), а также пока напряжение на выходах первого 9 (UOH1) и второго 10 (UOH2) ограничителей напряжения (ОН) не снизилось до уровня логического "нуля". Напряжения на выходах первого 9 ОН и второго 10 ОН являются следующими функциями напряжений на управляющих входах СК инвертора 1 U5(t) и U6(t):

Сигналы с первого и второго выходов БУП 4 преобразуются и усиливаются первым 7 и вторым 8 предварительными усилителями соответственно. Они преобразуют напряжение, поступающее с первого и второго выходов БУП 4, уровня лог 1 в напряжение Uупр1, уровня лог 0 - в напряжение Uупр0, причем:

где

Uком1 - напряжение на выходе компаратора 25, если потенциал его неинвертирующего входа больше потенциала инвертирующего входа, В;

Uбэnpn - падение напряжения на открытом переходе npn транзистора, входящего в состав ДУМ 26, В;

Uком0 - напряжение на выходе компаратора 25, если потенциал его неинвертирующего входа меньше потенциала инвертирующего входа, В;

Uбэpnp - падение напряжения на открытом переходе pnp транзистора, входящего в состав ДУМ 26, В.

Напряжение Uупр1 соответствует открывающему импульсу, Uупр0 - закрывающему импульсу, подаваемому на управляющие входы инвертора 1.

Напряжение Uупр1, подаваемое на управляющий вход инвертора 1, запирает p-канальный 29 и отпирает n-канальный 30 полевые транзисторы из состава комплементарного ключа 27, током открытого n-канального 30 полевого транзистора открывается биполярный транзистор 28, СК инвертора 1 открыт. Напряжение Uупр0, подаваемое на управляющий вход инвертора 1, отпирает р-канальный 29 и запирает n-канальный 30 полевые транзисторы из состава комплементарного ключа 27, ток в базу биполярного транзистора 28 прекращает течь и СК инвертора 1 закрывается.

Рассмотрим процесс коммутации в режиме работы с номинальной нагрузкой. В этом случае момент выключения одного СК инвертора 1 отстает от включения другого СК инвертора 1 на интервал времени:

где

td - время задержки распространения сигнала между выходом БУП 4 и управляющим входом инвертора 1, с;

ton/toff - время задержки включения/выключения СК инвертора 1 с момента подачи соответствующего импульса на управляющий вход, за которое ток изменится незначительно, с.

Поскольку существует магнитная связь между обмотками силового трансформатора инвертора 1, ток из одной полуобмотки перераспределится, согласно закону полного тока в другие обмотки мгновенно, скачкообразно:

где

w1, w2 - число витков в первичных полуобмотках силового трансформатора инвертора 1, шт.;

w3 - число витков во вторичной обмотке силового трансформатора инвертора 1, шт.;

ic - ток заряда фильтра 2 (ток вторичной обмотки), А.

Такое перераспределение токов приводит к уменьшению пульсаций приведенного тока нагрузки, протекающего в СК инвертора 1.

В режиме работы с номинальной нагрузкой сигнал на выходе порогового элемента ПЭ 6 отсутствует (интервал t0-t4) (фиг.6).

Рассмотрим формирование импульсов на управляющих входах инвертора 1 в режиме токоограничения (заряда емкости выходного фильтра 3). Этот режим характеризуется формированием импульсов токоограничения на выходе ПЭ 6 при достижении током в СК инвертора 1 максимального значения I max. Датчик тока (ДТ) 5, выполненный, например, в виде датчика Холла, установленного в эмиттерных цепях СК инвертора 1, измеряет суммарное значение токов i1(t) и i2(t), протекающих через СК инвертора 1, формируя на своем выходе напряжение U7(t) (фиг.6):

где

kDT - коэффициент датчика тока 5, В/А.

Когда один из СК инвертора 1 открыт, а другой закрыт, сигнал на выходе ДТ5 пропорционален току, протекающему через открытый СК инвертора 1. Например, в момент времени t4, когда был сформирован открывающий импульс на первом выходе БУП 4 и закрывающий - на втором, произошло скачкообразное увеличение нагрузки. Импульс токоограничения будет сформирован в том случае, если ток i(t) СК инвертора 1 нарастет согласно (7) до значения Imax до того, как напряжение на выходе интегратора 18, входящего в состав БУП 4, достигнет значения U min.

где

U0 - напряжение источника питания, В;

uC(t) - напряжение на емкости выходного фильтра 3, В;

uCE(t) - падение напряжения на СК инвертора 1, В;

k - коэффициент трансформации силового трансформатора инвертора 1;

L - индуктивность рассеивания силового трансформатора инвертора 1, Гн.

Поступая через резистивно-емкостной фильтр 21 (фиг.3) на вход четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ) ПЭ 6, сигнал с ДТ 5 вызывает переключение четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ) в состояние логического "нуля" в момент времени (t5), когда напряжение на его входе U8(t) (фиг.6) достигнет верхнего порога переключения триггера Umax (фиг.6). Таким образом, величина I max определяется порогом срабатывания четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ) (фиг.3), соотношением резистора из состава резистивно-емкостного фильтра 21 и второго резистора 24, постоянной времени резистивно-емкостного фильтра 21, коэффициентом передачи ДТ 5.

Импульс токоограничения U9(t), проинвертированный инвертором 22, поступает на третий вход БУП 4, завершая согласно (1) формирование открывающего импульса на первом выходе БУП 4 и запрещая формирование открывающих импульсов на втором выходе БУП 4. Одновременно происходит переключение третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ) посредством формирования на выходе первого 11 и второго 12 триггеров Шмитта с объединением двух входов по & (2-И-НЕ) напряжений:

Напряжение на выходе третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ), с учетом первого инвертора 14 и диода 19:

Таким образом, после появления импульса токоограничения на выходе ПЭ 6 в момент времени t5 U9=1, UOH1=1→U10=0; UOH2=0→U11=1→U1=1.

На процесс коммутации СК инвертора 1 влияет индуктивность рассеивания силового трансформатора инвертора 1. На интервале td+toff ток ключа продолжает нарастать и достигает значения Imax. На интервале (t5+td+toff)-t5' (фиг.6) ток i1(t) в одном СК инвертора 1 спадет за счет индуктивности рассеивания до значения I min. Скорость спада тока i1(t) определяется следующим образом:

Поскольку поток рассеивания одной полуобмотки трансформатора инвертора 1 не связан с витками других обмоток, скорость его изменения не ограничивается значением напряжения питания и вызывает перенапряжение, равное UCE(i) на силовом ключе инвертора 1, в котором спадает ток, большее, чем 2U0. Таким образом, ток в данном СК инвертора 1 спадает быстрее, чем нарастает в противоположном.

Напряжение на входе четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ), из состава ПЭ 5, в момент времени t5' упадет до значения U min, снимая импульс токоограничения на выходе ПЭ 6. Согласно (9) напряжение на выходе третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ) не изменится. Согласно (1) на втором выходе БУП 3 будет сформирован открывающий импульс. Через интервал времени td+ton от момента t5' (фиг.6), когда ток i1(t) спадет до значения I min, включится другой СК инвертора 1. Таким образом, пауза между выключением одного СК инвертора 1 и включением другого СК инвертора 1 увеличивается на длительность импульса токоограничения U9(t), например, на длительность интервала t5-t5', пульсации тока возрастут по сравнению с режимом номинальной нагрузки.

Токи в полуобмотках в момент времени t5'' перераспределяются согласно (5) и станут равными (одинаковыми) и в сумме будут составлять значение I min. Ток в СК инвертора 1 будет нарастать согласно (7).

Второй импульс токоограничения будет сформирован в момент времени t6 в том случае, если напряжение на входе четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ) возрастет до значения U max до того, как напряжение на выходе интегратора 18, из состава БУП 4, достигнет значения U max. Импульс токоограничения поступает на третий вход БУП 4, запрещая согласно (1) формирование открывающих импульсов на первом и втором выходах БУП 4.

Одновременно происходит переключение третьего 13 триггера Шмитта с объединением двух входов по & (2-И-НЕ). После появления импульса токоограничения на выходе ПЭ 6 (интервал t6-t6') u9=1, uOH1=0→u10=1; uOH2=1→u11=0→u1=0. Напряжение на входе четвертого 22 триггера Шмитта с объединением двух входов по & (2-И-НЕ) из состава ПЭ 6 начинает уменьшаться. Когда оно достигнет значения U min (момент времени t6'') снимется импульс токоограничения на выходе ПЭ 6. На интервале t6''-t7 повторятся процессы, происходящие на интервале времени t5''-t6.

Работа преобразователя в режиме ограничения тока продолжается до тех пор, пока, согласно (7) напряжение на емкости выходного фильтра 3 Uc не вырастет до значения, при котором ток открытого СК инвертора 1 не будет успевать нарастать до значения I max за время Т/2.

Таким образом, ток заряда емкости выходного фильтра 3 ограничивается на некотором среднем уровне, не меньшем Ic0 (фиг.6):

где

Imax - максимальное значение тока СК инвертора 1, А.

Токи одновременно включенных СК инвертора 1 создают в сердечнике трансформатора инвертора 1 встречные потоки, и ток заряда емкости выходного фильтра 3 (ток вторичной обмотки после выпрямления) Ic(t), должен иметь кратковременный провал, определяемый, например, на интервале Δt1 следующим образом:

Однако за счет собственной индуктивности рассеивания вторичной обмотки, учтенной при измерении L по методике [4], ток I с на интервале Δt1 не спадает до нуля даже в моменты времени t5'', t6''.

Напряжение на емкости выходного фильтра 3 Uc(t) растет линейно до момента выхода из режима токоограничения. Время заряда tch:

где

С - величина емкости выходного фильтра 3, Ф.

Uc0 - напряжение на емкости выходного фильтра 3, при котором заканчивается токоограничение, В.

Uc0 определяется согласно (7) при dt=T/2 с учетом времени спада тока и значения

Imin

где

Т - период работы преобразователя в режиме номинальной нагрузки, с;

Imin - минимальное значение тока СК инвертора 1, А.

Импульсы токоограничения на выходе ПЭ 6 сокращают время "подъема" и "спада" пилообразного напряжения интегратора 18, из состава БУП 4, повышая частоту работы преобразователя. Частота преобразования в режиме токоограничения максимальна в начале заряда емкости и определяется как:

Для экспериментального образца преобразователя с индуктивностью рассеивания L силового трансформатора инвертора 1, измеренной по методике [4], равной 1 мкГн, при уровне ограничения тока СК инвертора 1 Imax=400 А, минимальном значении тока СК инвертора 1 Imin=100 A напряжении питания U0=27 В и емкости выходного фильтра 3 С=4·103 мкФ, периоде работы преобразователя в режиме номинальной нагрузки Т=100 мкс, падении напряжения на СК инвертора 1 UCE=2 В, коэффициенте трансформации силового трансформатора инвертора 1 k=9 расчетное значение UC0 составляет 9(27В-2В-2·1·10-6Гн·(400A-100A)·27B)/(100·10-6 c·27B-1·10-6Гн·(400A-100A))=164B, расчетное время заряда tch=2·9·4·103 мкФ·164В/400А=29,5 мс, максимальная частота преобразования fmax=27В·(27В-2B)/1·10-6 Гн(3·27B-2B)·(400A-100A)=28.5 кГц, что совпадает с экспериментальными данными, полученными на опытном образце.

Перераспределение токов в обмотках в момент коммутации влечет за собой увеличение постоянной составляющей приведенного тока нагрузки при сохранении максимального амплитудного значения тока СК инвертора 1, что ускоряет заряд емкости, уменьшает переменную составляющую тока источника питания, увеличивая КПД.

Поскольку выброс напряжения на закрывающемся СК инвертора 1, как правило, ограничивается запасенной на интервале спада тока энергией дополнительного конденсатора и пропорционален LI2, перераспределение тока в обмотках (магнитной энергии) уменьшает этот выброс, повышая надежность работы преобразователя.

Повышение надежности работы преобразователя связано также с тем, что полностью исключается возможность повторного включения одного и того же СК инвертора 1, что снижает вероятность одностороннего подмагничивания сердечника силового трансформатора инвертора 1.

Таким образом, при работе данного устройства ограничения тока контролируется максимальная величина тока и исключаются паузы в нем, время заряда емкости выходного фильтра 3 сокращается до минимально возможного, связанного с предельной частотой работы СК инвертора 1.

Данный двухтактный транзисторный преобразователь был изготовлен на предприятии и прошел испытания с положительными результатами.

Источники информации

1. В.С.Моин. Стабилизированные транзисторные преобразователи. - М.: Энергоатомиздат, 1986, - 376 с., рис.4.15.

2. Патент РФ №2061293.

3. Патент РФ №2110133.

4. М.Ю.Румянцев. Высокочастотные трансформаторы с пониженной индуктивностью рассеивания для источников вторичного электропитания. // Практическая силовая электроника. - 2005. - №19.

1. Двухтактный транзисторный преобразователь, содержащий инвертор на силовых ключах, где переменное напряжение трансформируется силовым трансформатором инвертора, выпрямляется выходным выпрямителем и сглаживается выходным фильтром, блок управления преобразователем, датчик тока, пороговый элемент, отличающийся тем, что в него введены первый и второй предварительные усилители, причем датчик тока установлен в эмиттерных цепях силовых ключей инвертора и своим выходом соединен с входом порогового элемента, выход которого соединен с вновь введенным третьим входом блока управления преобразователем, первый и второй вновь введенные входы блока управления преобразователем соединены с соответствующими выходами первого и второго предварительных усилителей, а также с управляющими входами соответствующих силовых ключей инвертора, первый и второй выходы блока управления преобразователем соединены с соответствующими входами первого и второго предварительных усилителей.

2. Двухтактный транзисторный преобразователь по п.1, отличающийся тем, что блок управления преобразователем включает в себя первый и второй ограничители напряжения, первый, второй и третий триггеры Шмитта с объединением двух входов по & (2-И-НЕ), первый и второй инверторы, первый и второй трехвходовые элементы логического сложения (3-ИЛИ-НЕ), интегратор, диод и первый резистор, при этом входы первого и второго ограничителей напряжения являются первым и вторым входами блока управления преобразователем; выход первого ограничителя напряжения соединен со вторым входом первого триггера Шмитта с объединением двух входов по & (2-И-НЕ) и первым входом первого трехвходового элемента логического сложения (3-ИЛИ-НЕ); выход второго ограничителя напряжения соединен со вторым входом второго триггера Шмитта с объединением двух входов по & (2-И-НЕ) и первым входом второго трехвходового элемента логического сложения (3-ИЛИ-НЕ); первый вход второго триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с первым входом первого триггера Шмитта с объединением двух входов по & (2-И-НЕ), а также с третьими входами первого и второго трехвходовых элементов логического сложения (3-ИЛИ-НЕ) и является третьим входом блока управления преобразователем; выход первого триггера Шмитта с объединением двух входов по & (2-И-НЕ) через первый инвертор соединен с анодом диода, катод которого соединен со вторым входом третьего триггера Шмитта с объединением двух входов по & (2-И-НЕ), второй вход которого также через первый резистор соединен с выходом интегратора; выход второго триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с первым входом третьего триггера Шмитта с объединением двух входов по & (2-И-НЕ), выход третьего триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединен с входом второго инвертора и вторым входом первого трехвходового элемента логического сложения (3-ИЛИ-НЕ); выход второго инвертора соединен с входом интегратора и вторым входом второго трехвходового элемента логического сложения (3-ИЛИ-НЕ); выходы первого и второго трехвходовых элементов логического сложения (3-ИЛИ-НЕ) являются соответственно первым и вторым выходами блока управления преобразователем.

3. Двухтактный транзисторный преобразователь по п.1, отличающийся тем, что пороговый элемент выполнен в виде последовательно соединенных между собой резистивно-емкостного фильтра, четвертого триггера Шмитта с объединением двух входов по & (2-И-НЕ), третьего инвертора, причем первый и второй входы четвертого триггера Шмитта с объединением двух входов по & (2-И-НЕ) соединены между собой и через второй резистор соединены с его выходом, при этом вход резистивно-емкостного фильтра является входом порогового элемента, а выход третьего инвертора является его выходом.

4. Двухтактный транзисторный преобразователь по п.1, отличающийся тем, что каждый из предварительных усилителей выполнен в виде последовательно соединенных между собой компаратора и двухтактного усилителя мощности, причем неинвертирующий вход компаратора является входом предварительного усилителя, а выход двухтактного усилителя мощности является его выходом.

5. Двухтактный транзисторный преобразователь по п.1, отличающийся тем, что каждый из силовых ключей инвертора выполнен в виде последовательно соединенных между собой комплементарного ключа и биполярного транзистора, причем комплементарный ключ содержит р-канальный и п-канальный полевые транзисторы, при этом управляющим входом каждого из силовых ключей инвертора являются соединенные между собой затворы полевых транзисторов из состава комплементарного ключа, а коллектор биполярного транзистора является его выходом; истоки п-канального и р-канального полевых транзисторов соединены между собой и соединены с базой биполярного транзистора, сток п-канального полевого транзистора соединен с коллектором биполярного транзистора, сток р-канального полевого транзистора и эмиттер биполярного транзистора соединены с источником питания.