Устройство для прогнозирования случайных событий

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и может быть использовано для оценки надежности и качества функционирования сложных автоматизированных и гибких производственных и телекоммуникационных систем произвольной структуры, в которых используется циклический характер производства, предоставления телекоммуникационных услуг и временное резервирование. Техническим результатом является повышение достоверности идентификации состояния производственной или телекоммуникационной системы в условиях недостоверности параметров моделируемых сигналов, характеризующих принадлежность конкретного сигнала состояния к пространству состояния безотказной работы системы либо к пространству отказов. Устройство содержит блок управления, блок модели системы, блок имитаторов состояний участков системы, блок формирования сигналов отказов, блок регистрации, блок проверки данных модели, блок коррекции данных модели. 2 з.п. ф-лы, 10 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано для оценки надежности и качества функционирования сложных автоматизированных и гибких производственных и телекоммуникационных систем произвольной структуры, в которых используется циклический характер производства, предоставления телекоммуникационных услуг и временное резервирование.

Известно устройство для прогнозирования случайных событий по авт. св. СССР № 1167619, G06F 15/46, 1985, бюл. №14, содержащее блок управления, блок модели системы и блок регистрации.

Недостатком данного устройства является относительно большое время определения численных значений оценок показателей качества функционирования производственных систем с циклическим характером работы.

Известно устройство для прогнозирования случайных событий, содержащее блок модели системы, блок формирования сигналов отказов и блок регистрации (см. авт. св. СССР № 1198484, G05В 23/02, 1985, бюл. № 26).

Однако данное устройство имеет относительно большое время процесса оценивания показателей надежности сложных производственных систем с временным резервированием.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство для прогнозирования случайных событий (см. авт. св. СССР № 1441421, G06F 15/46, 1988, бюл. № 44), содержащее блок управления, блок модели системы, блок имитаторов состояний участков системы, блок формирования сигналов отказов и блок регистрации. При этом информационный вход блока регистрации подключен к информационному выходу блока формирования сигналов отказов, управляющий вход которого подключен к управляющему выходу блока модели системы. Сбросовый выход блока управления соединен с сбросовыми входами блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации, М≥2 контрольных выходов блока управления подключены к соответствующим М контрольным входам блока модели системы. Синхронизирующий выход блока управления подключен к синхронизирующим входам блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации. Управляющий выход блока управления соединен с управляющим входом блока имитаторов состояний участков системы, N≥2 групповых входов которого подключены к соответствующим N групповым выходам блока модели системы, N групповых входов которого соединены с соответствующими N групповыми выходами блока имитаторов состояний участков системы. Вход блока управления подключен к выходу блока регистрации, сигнальный вход которого соединен с сигнальным выходом блока формирования сигналов отказов.

В прототипе реализуется возможность повышения скорости оценивания показателей надежности сложных производственных и телекоммуникационных систем с циклическим характером работы и временным резервированием.

Однако прототип имеет недостаток - относительно низкую достоверность идентификации состояния безотказной работы системы (выполнения сменных заданий за оперативное время) и противоположного состояния - отказа системы в условиях недостоверности (недостаточности, неполноты и противоречивости) параметров модели процесса функционирования исследуемой системы. Под «оперативным временем» понимается время, выделяемое для выполнения системой задания. Временной резерв системы и ее участков образуется за счет увеличения времени, выделяемого для выполнения задания.

Целью заявленного технического решения является создание устройства для прогнозирования случайных событий, обеспечивающего повышение достоверности идентификации состояния производственной или телекоммуникационной системы в условиях недостаточности (неполноты и противоречивости) данных об истинных значениях параметров моделируемых сигналов.

Возможность повышения достоверности идентификации состояния производственной или телекоммуникационной системы обеспечивается путем верификации (нейроанализа) данных, характеризующих неоднозначные (недостоверные, неполные) сигналы о наличии изделия, требующего обработки (или заявки на предоставление абоненту телекоммуникационной системы услуги) на модельных участках производственной системы, и изготовлении производственной системой изделия (или доведения до абонента телекоммуникационной системы услуг).

Указанная цель достигается тем, что в известное устройство для прогнозирования случайных событий, содержащее блок управления, блок модели системы, блок имитаторов состояний участков системы, блок формирования сигналов отказов и блок регистрации, выход которого подключен к входу блока управления, а информационный и сигнальный входы блока регистрации подключены соответственно к информационному и сигнальному выходам блока формирования сигналов отказов, сбросовый выход блока управления соединен со сбросовыми входами блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации, М≥2 контрольных выходов блока управления подключены к соответствующим М контрольным входам блока модели системы, синхронизирующий выход блока управления подключен к синхронизирующим входам блока имитаторов состояний участков системы, блока модели системы, блока формирования сигналов отказов и блока регистрации, управляющий выход блока управления соединен с управляющим входом блока имитаторов состояний участков системы, N≥2 групповых выходов которого подключены к соответствующими N групповыми входами блока модели системы, дополнительно включены блок проверки данных модели и блок коррекции данных модели. При этом сбросовые и синхронизирующие входы блока проверки данных модели и блока коррекции данных модели подключены соответственно к сбросовому и синхронизирующему выходам блока управления, N групповых выходов блока коррекции данных модели. N групповых выходов блока проверки данных модели подключены к соответствующим N групповым входам блока имитаторов состояний участков системы. Причем N-разрядный вход блока коррекции данных модели подключен к соответствующему N-разрядному выходу блока проверки данных модели, сигнальный выход которого подключен к сигнальному входу блока коррекции данных модели. Управляющий вход блока формирования сигналов отказов подключен к управляющим выходам блоков проверки данных модели и коррекции данных модели, а N групповых входов блока проверки данных модели соединены с соответствующими N групповыми выходами блока модели системы, управляющий выход которого подключен к управляющему входу блока проверки данных модели.

Блок проверки данных модели состоит из селектора исходных данных и преобразователя недостоверных данных. При этом N-разрядный выход преобразователя недостоверных данных является N-разрядным выходом блока проверки данных, запрещающий выход преобразователя недостоверных данных соединен с инверсным запрещающим входом селектора исходных данных, N групповых выходов которого являются N групповыми выходами блока проверки данных. Разрешающий вход преобразователя недостоверных данных подключен к разрешающему выходу селектора исходных данных, N групповых входов, управляющий, сбросовый и синхронизирующий входы которого соединены с соответствующими N групповыми входами, управляющим, сбросовым и синхронизирующим входами преобразователя недостоверных данных и являются соответствующими N групповыми входами, управляющим, сбросовым и синхронизирующим входами блока проверки данных модели. Сигнальный выход преобразователя недостоверных данных является сигнальным выходом блока проверки данных модели, а управляющий выход селектора исходных данных является управляющим выходом блока проверки данных модели.

Блок коррекции данных модели состоит из программируемого вычислителя, первичного и вторичного запоминающих элементов. При этом сигнальный и N-разрядный входы программируемого вычислителя являются соответственно сигнальным и N-разрядным входами блока коррекции данных модели. Синхронизирующий вход программируемого вычислителя является синхронизирующим входом блока коррекции данных модели, а сбросовый вход программируемого вычислителя являются соответственно сбросовым входом блока коррекции данных модели. При этом управляющий выход и N групповых выходов программируемого вычислителя соединены соответственно с управляющим входом первичного и N групповыми входами вторичного запоминающих элементов блока коррекции данных модели. Причем выход первичного и N групповых выходов вторичного запоминающих элементов являются соответственно управляющим и N групповыми выходами блока коррекции данных модели.

Благодаря новой совокупности существенных признаков, за счет введения блоков проверки данных модели и коррекции данных модели, обеспечивающих соответственно проверку данных, обработку и трансформирование неполных (недостаточных, противоречивых) параметров модели процесса функционирования исследуемой системы, т.е. множества числовых значений характеристик свойств конкретного процесса в данный момент времени и, как следствие, неполных (недостаточных, противоречивых) результатов прогнозирования случайных событий, т.е. соотношения времени выполнения сменного задания и количества изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг), к виду, пригодному для достоверной идентификации времени выполнения сменного задания и количества изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг). В заявленном устройстве это достигается путем предварительного анализа и верификации сигналов о наличии изделия, требующего обработки (или заявки на предоставление абоненту телекоммуникационной системы услуги) на модельных участках производственной системы, и изготовлении производственной системой изделия (или доведения до абонента телекоммуникационной системы услуг), что обуславливает повышение достоверности идентификации состояния производственной или телекоммуникационной системы в условиях недостоверности (недостаточности, неполноты, а зачастую и противоречивости) параметров модели процесса функционирования исследуемой системы.

Заявленное устройство поясняется чертежами, на которых представлены:

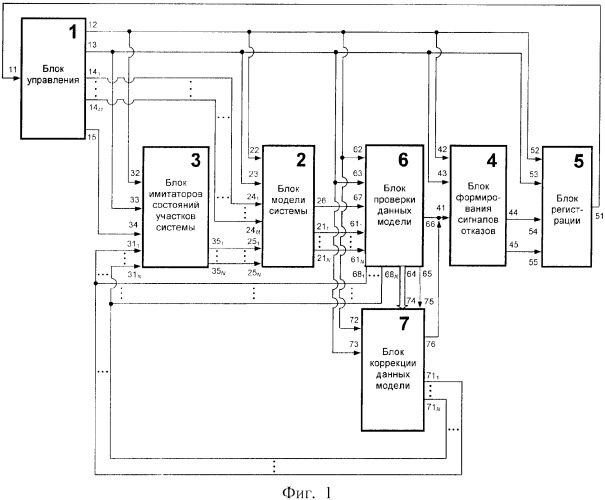

на фиг.1 - структурная схема устройства для прогнозирования случайных событий;

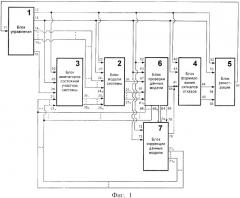

на фиг.2 - структурная схема блока проверки данных модели;

на фиг.3 - структурная схема блока коррекции данных модели;

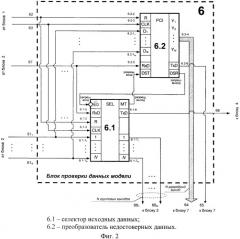

на фиг.4 - структурная схема блока управления;

на фиг.5 - пример структуры конкретной системы (из шести участков, N=6);

на фиг.6 - структурная схема блока модели системы;

на фиг.7 - структурная схема n-го () модельного элемента участка системы;

на фиг.8 - структурная схема блока имитаторов состояний участков системы;

на фиг.9 - структурная схема блока формирования сигналов отказов;

на фиг.10 - структурная схема блока регистрации.

Устройство для прогнозирования случайных событий, изображенное на фиг.1, состоит из блока управления 1, блока модели системы 2, блока имитаторов состояний участков системы 3, блока формирования сигналов отказов 4, блока регистрации 5, блока проверки данных модели 6, блока коррекции данных модели 7. При этом выход 51 блока регистрации 5 подключен к входу 11 блока управления 1, сбросовый выход 12 блока управления 1 соединен со сбросовым входом 32 блока имитаторов состояний участков системы 3, сбросовым входом 22 блока модели системы 2, сбросовым входом 42 блока формирования сигналов отказов 4, сбросовым входом 52 блока регистрации 5, сбросовым входом 62 блока проверки данных модели 6, сбросовым входом 72 блока коррекции данных модели 7. Причем М≥2 контрольных выходов 141-14M блока управления 1 подключены к соответствующим М контрольным входам 241-24M блока модели системы 2. Синхронизирующий выход 13 блока управления 1 подключен к синхронизирующему входу 33 блока имитаторов состояний участков системы 3, синхронизирующему входу 23 блока модели системы 2, синхронизирующему входу 43 блока формирования сигналов отказов 4, синхронизирующему входу 53 блока регистрации 5, синхронизирующему входу 63 блока проверки данных модели 6, синхронизирующему входу 73 блока коррекции данных модели 7. Управляющий выход 15 блока управления 1 соединен с управляющим входом 34 блока имитаторов состояний участков системы 3, N≥2 групповых входов 311-31N которого подключены к N групповым выходам 711-71N блока коррекции данных модели 7 и к N групповым выходам 681-68N блока проверки данных модели 6. N-разрядный выход 64 блока проверки данных модели 6 соединен с N-разрядным входом 74 блока коррекции данных модели 7, а сигнальный выход 65 блока проверки данных модели 6 соединен с сигнальным входом 75 блока коррекции данных модели 7. N групповых входов 611-61N блока проверки данных модели 6 соединены с соответствующими N групповыми выходами 211-21N блока модели системы 2, N групповых входов 251-25N которого соединены с соответствующими N групповыми выходами 351-35N блока имитаторов состояний участков системы 3. Информационный 54 и сигнальный 55 входы блока регистрации 5 соединены соответственно с информационным 44 и сигнальным 45 выходами блока формирования сигналов отказов 4, управляющий вход 41 которого подключен к управляющему выходу 66 блока проверки данных модели 6 и управляющему выходу 76 блока коррекции данных модели 7. Управляющий вход 67 блока проверки данных модели 6 подключен к управляющему выходу 26 блока модели системы 2.

Число «N (N≥2)» (элементов, входов, выходов и т.п.) определяется в соответствии с возможным количеством участков исследуемой производственной или телекоммуникационной системы и, как правило, составляет от 2 (двух) до 50 (пятидесяти).

Число «M, (M≥2)» характеризует возможное количество агрегатов участка исследуемой производственной или телекоммуникационной системы и, как правило, составляет от 2 (двух) до 20 (двадцати).

Блок проверки данных модели 6 (фиг.2) предназначен для анализа и регистрации истинных значений параметров моделируемых сигналов, полученных в результате моделирования производственного или телекоммуникационного процесса - время выполнения сменного задания и количество изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг) и характеризующих принадлежность конкретного сигнала состояния к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов, а также для преобразования данных, идентифицируемых неоднозначно (недостоверно, неполно), к виду, пригодному для получения однозначных (достоверных) результатов прогнозирования случайных событий, т.е. преобразование из параллельного кода в последовательный с целью последующего распознавания.

Блок проверки данных модели 6 состоит из селектора исходных данных 6.1 и преобразователя недостоверных данных 6.2. При этом N-разрядный выход 6.2-4 преобразователя недостоверных данных 6.2 является N-разрядным выходом 64 блока проверки данных модели 6. Запрещающий выход DSR преобразователя недостоверных данных 6.2 соединен с инверсным запрещающим входом селектора исходных данных 6.1, N групповых выходов 6.1-71 - 6.1-7N которого являются соответствующими N групповыми выходами 681-68N блока проверки данных модели 6. Разрешающий вход DST преобразователя недостоверных данных 6.2 подключен к разрешающему выходу МТ селектора исходных данных 6.1, N групповых входов 6.1-11 - 6.1-1N, управляющий 6.1-5, сбросовый 6.1-2 и синхронизирующий 6.1-3 входы которого соединены с соответствующими N групповыми входами 6.2-11 - 6.2-1N, управляющим 6.2-5, сбросовым 6.2-2 и синхронизирующим 6.2-3 входами преобразователя недостоверных данных 6.2 и являются соответствующими N групповыми входами 611-61N, управляющим 67, сбросовым 62 и синхронизирующим 63 входами блока проверки данных модели 6. Сигнальный выход 6.2-6 преобразователя недостоверных данных 6.2 является сигнальным выходом 65 блока проверки данных модели 6, а управляющий выход 6.1-6 селектора исходных данных 6.1 является управляющим выходом 66 блока проверки данных модели 6.

Селектор исходных данных 6.1 блока проверки данных модели 6 предназначен для осуществления процедуры селекции истинных значений параметров моделируемых сигналов, полученных в результате моделирования производственного или телекоммуникационного процесса и выбора данных, необходимых для распознавания принадлежности конкретного сигнала состояния к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов.

Селектор исходных данных 6.1 может быть технически реализован в виде серийно выпускаемого селектора на КМДП-структурах с одним инверсным запрещающим, сбросовым, синхронизирующим входами и одним разрешающим выходом, на базе интегральной микросхемы серии 564 (например, SEL К564КП2), как показано в литературе [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994. С.28-33].

Преобразователь недостоверных данных 6.2 блока проверки данных 6 предназначен для регистрации данных, необходимых для распознавания принадлежности конкретного сигнала состояния к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов и преобразования этих данных из параллельного кода в последовательный. Преобразователь недостоверных данных 6.2 может быть технически реализован в виде универсального программируемого синхронно-асинхронного приемопередатчика на базе интегральной микросхемы PCI КР580ИК51, описанной в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С.66-74, рис.3.14].

Блок коррекции данных модели 7 (фиг.3) предназначен для записи, хранения результатов анализа данных и математически корректного распознавания (определения) параметров, заданных как количественно, так и качественно (недостоверно, неполно, противоречиво) и полученных в результате моделирования производственного или телекоммуникационного процесса, соотношение которых характеризует состояние безотказной работы системы (выполнения сменных заданий за оперативное время) или противоположное состояние - отказ системы, и преобразования этих данных из последовательного кода в параллельный с целью последующего продолжения моделирования производственного или телекоммуникационного процесса.

Блок коррекции данных модели 7 состоит из программируемого вычислителя 7.1, первичного 7.2 и вторичного 7.3 запоминающих элементов, при этом сигнальный 7.1-1 и N-разрядный входы 7.1-2 программируемого вычислителя 7.1 являются соответственно сигнальным 75 и N-разрядным входами 74 блока коррекции данных модели 7, синхронизирующий вход 7.1-4 программируемого вычислителя 7.1 является синхронизирующим входом 73 блока коррекции данных модели 7, сбросовый вход 7.1-3 программируемого вычислителя 7.1 является соответственно сбросовым входом 72 блока коррекции данных модели 7, при этом управляющий выход 7.1-5 и N групповых выходов 7.1-61 - 7.1-6N программируемого вычислителя 7.1 соединены соответственно с управляющим входом 7.2-1 первичного 7.2 и N групповыми входами 7.3-11 - 7.3-1N вторичного 7.3 запоминающих элементов блока коррекции данных модели 7, причем выход 7.2-2 первичного 7.2 и N групповых выходов 7.3-21 - 7.3-2N вторичного 7.3 запоминающих элементов являются соответственно управляющим 76 и N групповыми 711-71N выходами блока коррекции данных модели 7.

Программируемый вычислитель 7.1 блока коррекции данных модели 7 предназначен для осуществления процедуры преобразования определенных (распознанных) неоднозначно (недостоверно, неполно) исходных данных, полученных в результате моделирования производственного или телекоммуникационного процесса, к виду, пригодному для однозначного принятия достоверного решения о принадлежности конкретного сигнала состояния к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов. Программируемый вычислитель 7.1 может быть технически реализован в виде серийно выпускаемой микропроцессорной секции (МПС или MPS - Micro-Processoring Section) типа MPS K1804BC1 с дополнительным сбросовым входом, подробно описанной в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С.243-281, рис.7.1 и 7.2]. Программируемый вычислитель 7.1 в виде микропроцессорной секции MPS K1804BC1 используется как программируемое параллельное арифметико-логическое устройство (АЛУ), обладающее возможностью наращивания разрядности и имеющий N-разрядный вход, синхронизирующий и сбросовый входы, а также N групповой выход.

Первичный 7.2 и вторичный 7.3 запоминающие элементы блока коррекции данных модели 7 аналогичны по структуре, функциональному предназначению и служат для записи и хранения кода, содержащего верифицированные результаты полученных данных в результате моделирования производственного или телекоммуникационного процесса - кода, соответствующего принадлежности конкретного сигнала состояния к пространству состояния безотказной работы системы либо к пространству отказов. Первичный 7.2 и вторичный 7.3 запоминающие элементы могут быть технически реализованы на базе серийно выпускаемого программируемого запоминающего устройства с N входами и N выходами, в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.197-199, рис.6.10].

Блок управления 1, входящий в общую структурную схему, предназначен для генерации сигналов управления - уровня "0" (режим, когда блоки устройства переводятся в исходное состояние) либо уровня "1" (соответствующего режиму "Работа"), генерации тактовых импульсов, обеспечивающих работу всего устройства по определенным циклам, и генерации единичных импульсов, синхронизирующих работу всех блоков устройства. Структура блока управления 1 известна, описана в прототипе (см. авт. св. СССР №1441421, G06F 15/46, 1988, бюл. № 44, фиг.2) и проиллюстрирована на фиг.4 данного описания. Блок управления 1 (см. фиг.4) содержит формирователь импульсов 1.1, генератор тактовых импульсов 1.2, переключатель 1.3, элемент И 1.4, синхронный счетчик 1.5 и дешифратор 1.6.

Блок модели системы 2, входящий в общую структурную схему, предназначен для моделирования процесса функционирования взаимосвязанных участков конкретной производственной или телекоммуникационной системы, пример структуры которой приведен на фиг.6. Структурная схема блока модели системы 2 известна, включает N≥2 модельных элементов участка системы, соединенных между собой в соответствии со структурой производственной или телекоммуникационной системы, детально описана в прототипе (см. авт. св. СССР № 1441421, G06F 15/46, 1988, бюл. № 44, фиг.8) и приведена на фиг.6, где, в качестве примера, количество участков N=6 и участки обозначены латинскими цифрами I, II, III, IV, V и VI.

Каждый из модельных элементов участка системы 2.1-2.N блока модели системы 2 предназначен для моделирования циклического процесса функционирования одного из участков производственной или телекоммуникационной системы с учетом отказов и восстановлений агрегатов участка, происходящих в случайные моменты времени. Структура каждого из модельных элементов участка системы 2.1-2.N известна, идентична для любого n-го () из участков системы, описана в прототипе (см. авт.св. СССР № 1441421, G06F 15/46, 1988, бюл. № 44, фиг.3) и проиллюстрирована в качестве примера для некоторого n-ого модельного элемента участка системы 2.n () на фиг.7 данного описания. При этом n-ый модельный элемент участка системы 2.n (см. фиг.7) содержит с первого по четвертый элементы ИЛИ 2.n.1 - 2.n.4, L (где L≥2) элементов И 2.n.51 - 2.n.5L, первичный элемент И 2.n.6, вторичный элемент И 2.n.7, первичный триггер 2.n.8, вторичный триггер 2.n.9, первичный счетчик 2.n.10, вторичный счетчик 2.n.11, первичный дешифратор 2.n.12 и вторичный дешифратор 2.n.13. Причем число «L, (L≥2)» характеризует возможное количество параллельно работающих участков исследуемой производственной или телекоммуникационной системы и, как правило, составляет от 2 (двух) до 20 (двадцати).

Блок имитаторов состояний участков системы 3, входящий в общую структурную схему, предназначен для имитации циклического процесса функционирования производственной или телекоммуникационной системы с учетом отказов и восстановлений агрегатов участка, происходящих в случайные моменты времени. Структура блока имитаторов состояний участков системы 3 известна, описана в прототипе (см. авт. св. СССР № 1441421, G06F 15/46, 1988, бюл. № 44, фиг.4) и представлена на фиг.8. Блок имитаторов состояний участков системы 3 (см. фиг.8) состоит из N≥2 имитаторов состояний участков системы 3.1-3.N, каждый из которых содержит, например, для имитатора состояний участков системы 3.1: элемент И 3.1.1, одновибратор 3.1.2, счетчик 3.1.3, дешифратор 3.1.4, элемент НЕ 3.1.5, М≥2 генераторов случайных импульсов 3.1.61 - 3.1.6M, элемент И-ИЛИ-НЕ 3.1.7 и элемент ИЛИ 3.1.8.

Блок формирования сигналов отказов 4 (фиг.9) предназначен для регистрации и дешифровки верифицированных результатов моделирования системы, поступающих с управляющего выхода блока проверки данных модели 6 или блока коррекции данных модели 7, а также учета и формирования численных значений количества изделий, изготовленных производственной системой, или количества доведенных до абонента телекоммуникационной системы услуг в текущую смену. Структурная схема блока формирования сигналов отказов 4 известна, подробно описана в прототипе (см. авт. св. СССР № 1441421, G06F 15/46, 1988, бюл. №44, фиг.5), а также приведена на фиг.9 данного описания. Блок формирования сигналов отказов 4 (см. фиг.9) содержит элемент ИЛИ 4.1, основной 4.2 и дополнительный 4.3 счетчики, основной 4.4 и дополнительный 4.5 дешифраторы.

Блок регистрации 5, входящий в общую структурную схему, предназначен для регистрации, учета и накопления статистических данных в интересах получения численных значений показателей надежности и качества функционирования производственной или телекоммуникационной системы. Структура блока регистрации 5 известна, описана в прототипе (см. авт. св. СССР № 1441421, G06F 15/46, 1988, бюл. № 44, фиг.6) и представлена на фиг.10 данного описания. Блок регистрации 5 (см. фиг.10) состоит из основного элемента И 5.1, К (где К≥2) элементов И 5.21 - 5.2K, делителя частоты 5.3, элемента ИЛИ 5.4, первичного 5.5, вторичного 5.6 и третичного 5.7 счетчиков, К≥2 счетчиков 5.81 - 5.8K, четверичного счетчика 5.9, первичного 5.10, вторичного 5.11, третичного 5.12 и четверичного 5.13 дешифраторов, одновибратора 5.14, переключателя 5.15 и элемента НЕ 5.16. Причем число “K, (К≥2)” характеризует возможное количество отказов системы за цикл работы, как правило, составляет от 2 (двух) до 50 (пятидесяти) и используется в интересах получения параметров эмпирического распределения наработки производственной или телекоммуникационной системы на отказ.

Устройство для прогнозирования случайных событий работает следующим образом.

Известно [1-7], что с точки зрения моделирования параметров, соотношение которых характеризует состояние безотказной работы системы (выполнения сменных заданий за оперативное время) и противоположное состояние - отказ системы, существует возможность распознавания (определения) этих параметров, заданных как количественно, так и качественно (недостоверно, неполно, противоречиво). Эта возможность реализуется с использованием нейросетевых вычислительных методов и алгоритмов, позволяющих путем последовательных нейросетевых преобразований данных, характеризующих состояние системы, осуществить переход от недостоверно (недостаточно, неполно) распознанных (определенных) данных, к виду данных, пригодному для однозначного принятия достоверного решения о принадлежности конкретного сигнала к пространству состояния безотказной работы системы (выполнения сменных заданий за оперативное время) либо к пространству отказов.

Рассмотренный в [1, 2, 5, 6] и детально описанный в [3] нейросетевой экстраполирующий вычислительный алгоритм, или так называемая экстраполирующая нейронная сеть (ЭНС), является разновидностью известных вычислительных моделей ассоциативной памяти и позволяет математически корректно, в рамках моделирования реального процесса функционирования сложных автоматизированных и гибких производственных и телекоммуникационных систем произвольной структуры, устранить неопределенность (недостоверность, неполноту) параметров при идентификации численных значений и соотношения ключевых параметров моделируемого процесса (времени выполнения сменного задания и количества изделий, изготовленных производственной системой (или количества доведенных до абонента телекоммуникационной системы услуг)), тем самым повысить достоверность идентификации состояния производственной или телекоммуникационной системы, а в конечном итоге повысить достоверность оценивания численных значений показателей надежности и качества функционирования таких систем в условиях, присущих реальной динамике процесса функционирования систем - в условиях неопределенности (недостоверности, недостаточности, неполноты и противоречивости) параметров моделируемых сигналов.

С учетом этого осуществляется прогнозирование случайных событий в заявленном устройстве. Перед началом работы устройства с помощью переключателя 1.3 блока управления 1 на второй вход 1.4-2 элемента И 1.4 блока управления 1 и на стробирующий вход 3.1.4-2 дешифратора 3.1.4 блока имитаторов состояний участков системы 3 подается "0". Затем, с выхода 1.1-1 формирователя импульсов 1.1 через сбросовый выход 12 блока управления 1 подается короткий импульс для установки блоков устройства в исходное состояние. По этому импульсу сбрасываются в ноль синхронный счетчик 1.5 блока управления 1, первичный 2.n.10 и вторичный 2.n.11 счетчики каждого из модельных элементов участка системы (в нашем примере - элемента 2.n, где ) блока модели системы 2, счетчик 3.1.3 блока имитаторов состояний участков системы 3, основной 4.2 и дополнительный 4.3 счетчики блока формирования сигналов отказов 4, первичный 5.5, вторичный 5.6, третичный 5.7, четверичный 5.9 счетчики, К счетчиков 5.81 - 5.8K блока регистрации 5, 6.1 селектор исходных данных и 6.2 преобразователь недостоверных данных блока проверки данных модели 6, программируемый вычислитель 7.1 блока коррекции данных модели 7.

Кроме того, при получении данного импульса первичный 2.n.8 и вторичный 2.n.9 триггеры каждого из модельных элементов участка системы (в нашем случае на примере некоторого элемента 2.n - фиг.7) блока модели системы 2 и делитель частоты 5.3 блока регистрации 5 устанавливаются в единичное состояние, М генераторов случайных импульсов 3.1.61 - 3.1.6M каждого из имитаторов 3.1-3.N блока имитаторов состояний участков системы 3 приводятся в исходное состояние, соответствующее работоспособному состоянию всех агрегатов производственной или телекоммуникационной системы. После этого устройство готово к работе.

С помощью переключателя 1.3 блока управления 1 подается уровень "1", соответствующий режиму "Работа", на второй вход 1.4-2 элемента И 1.4 блока управления 1 (на первом входе 1.4-1 которого в этот момент присутствует "1") и на стробирующий вход 3.1.4-2 дешифратора 3.1.4 блока имитаторов состояний участков системы 3, тем самым разрешая его работу. На выходе 1.4-4 элемента И 1.4 блока управления 1 появляются импульсы генератора тактовых импульсов 1.2, распределитель импульсов на синхронном счетчике 1.5 и дешифраторе 1.6 начинает работать. На М контрольных выходах 141-14M блока управления 1 поочередно появляются единичные импульсы, синхронизирующие работу всего устройства. Контрольные выходы 141-14M блока управления 1 подключены к контрольным входам 241-24M блока модели системы 2, соединенным с контрольными входами 2.n-21 - 2.n-2M каждого из модельных элементов участка системы (в нашем случае - на примере элемента 2.n, см. фиг.7) блока модели системы 2.

Каждый из N модельных элементов участка системы (например, элемент 2.n () блока модели системы 2, совместно с соответствующим имитатором 3.n () состояния участков системы блока имитаторов состояний участков системы 3) предназначен для моделирования циклического процесса функционирования одного из участков производственной или телекоммуникационной системы с учетом отказов и восстановлений агрегатов участка, происходящих в случайные моменты времени.

Работу каждого из N имитаторов состояний участков системы блока имитаторов состояний участков системы 3 поясним на примере имитатора состояний участков системы 3.1 (т.е. n=1). Имитатор состояний участков системы 3.1. работает следующим образом (фиг.8).

На второй вход 3.1-3 имитатора 3.1 через синхронизирующий вход 33 блока имитаторов состояний участков системы 3 при работе устройства поступает тактовая последовательность импульсов с синхронизирующего выхода 13 (с выхода 1.6-3 дешифратора 1.6) блока управления 1. Помимо этого тактовая последовательность импульсов с синхронизирующего выхода 13 блока управления 1 поступает на синхронизирующий вход 23 блока модели системы 2, синхронизирующий вход 43 блока формирования сигналов отказов 4, синхронизирующий вход 53 блока регистрации 5, синхронизирующий вход 63 блока проверки данных модели 6, синхронизирующий вход 73 блока коррекции данных модели 7. Частота импульсов последовательности задает масштаб моделирования процесса функционирования производственной или телекоммуникационной системы, т.е. интервалу времени между двумя соседними импульсами последовательности соответствует определенный интервал реального времени функционирования производственной или телекоммуникационной системы.

На третьем входе 3.1-4 имитатора 3.1 во время работы устройства присутствует единичный сигнал, поступающий через управляющий вход 34 блока имитаторов состояний участков системы 3 с управляющего выхода 15 блока управления 1. На четвертом входе 3.1-1 имитатора 3.1, соединенном с одним из N возможных групповых выходов 711-71N блока коррекции данных модели 7 и с одним из N возможных групповых выходов 681-68N блока проверки данных модели, единичный сигнал появляется в момент поступления требующего обработки изделия на участок системы. По переднему фронту этого сигнала одновибратор 3.1.2 формирует короткий импульс, сбрасывающий в ноль счетчик 3.1.3 имитатора состояний участков системы 3.1 блока имитаторов состояний участков системы 3.

Счетчик 3.1.3 и дешифратор 3.1.4 (фиг.8) используются для распределения импульсов - задания циклограммы работы агрегатов участка производственной или телекоммуникационной системы. После сброса счетчика 3.1.3 в ноль на его счетный вход 3.1.3-1 начинают поступать тактовые импульсы. Моменты включения и выключения отдельных агрегатов участка моделируются появлением и исчезновением единичных импульсов на соответствующих агрегатам выходах 3.1.4-31 - 3.1.4-3M дешифратора 3.1.4. Единичный сигнал с m-го (m=1, …, М) выхода 3.1.4-3m дешифратора 3.1.4 поступает на управляющий вход 3.1.6-2m m-го генератора случайных импульсов 3.1.6M, и обеспечивает в нем процессы, имитирующие возможный отказ m-го агрегата во включенном состоянии (принимается допущение, что в выключенном состоянии износа агрегата не происходит и он отказать не может).

В случае, если m-й агрегат находится в работоспособном состоянии, чему соответствует нулевой