Активная нагрузка дифференциальных усилителей

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях). Активная нагрузка (АН) дифференциальных усилителей (ДУ) содержит выходной транзистор (1), база которого подключена к токовому входу (2) активной нагрузки, коллектор - к токовому выходу (3) активной нагрузки, а эмиттер соединен с базой входного транзистора (4) и вспомогательным p-n переходом (5), выходной транзистор (6) эмиттерного повторителя напряжения (7), база которого соединена с токовым выходом (3) активной нагрузки, а эмиттер подключен к коллектору вспомогательного транзистора (8) и потенциальному выходу (9) активной нагрузки, причем эмиттер вспомогательного транзистора (8) связан с эмиттером входного транзистора (4) и шиной (10) источника питания, а вход (2) активной нагрузки соединен с коллектором входного транзистора (4). База вспомогательного транзистора (8) соединена с коллектором входного транзистора (4). Техническим результатом при использовании АН в соответствии с изобретением является улучшение статических параметров ДУ. 2 з.п. ф-лы, 12 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, дифференциальных (ДУ) и операционных (ОУ) усилителях).

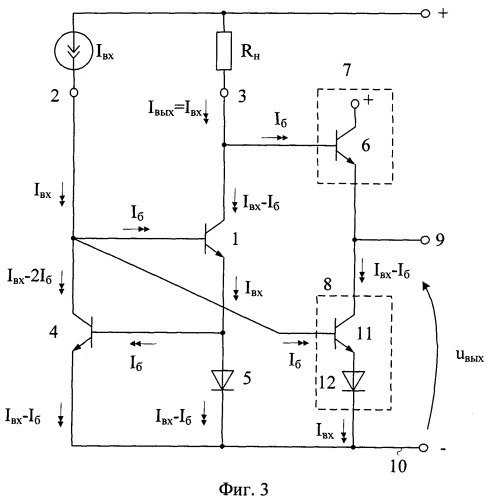

Известны схемы активных нагрузок дифференциальных усилителей (АН), реализованных на основе так называемых «токовых зеркал» [1-56] (фиг.1). Проблема повышения их точности (обеспечения единичной передачи тока со входа на выход) является одной из актуальных проблем аналоговой микросхемотехники. Однако в практических схемах аналоговых устройств получение единичной передачи по току токового зеркала Ki=Iвых.i/Iвх.i=1 решает проблему минимизации напряжения смещения нуля (Uсм) только в том случае, когда выходной буферный усилитель АН (фиг.1) имеет нулевой входной ток (Iвх.БУ=0). Если Iвх.БУ≠0, то необходим некоторый разбаланс входного напряжения ДУ Uвх=Ucм, при котором IДУ=Iвх.БУ+Iвых.i. Данное обстоятельство создает проблему обеспечения малых Uсм при использовании типовых активных нагрузок ДУ в практических схемах операционных усилителей. Комплексное решение этой задачи состоит в специальном построении токового зеркала и буферного усилителя, при котором в широком диапазоне температур, радиационных воздействий и статических токов обеспечивается равенство токов IДУ=Iвх.i+Iвых.i+Iвх.БУ.

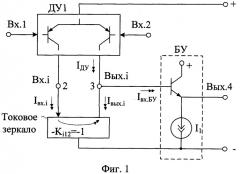

Ближайшим прототипом (фиг.2) заявляемого устройства является активная нагрузка дифференциальных усилителей, описанная в патенте США №5515005 (фиг.21, элементы Q10÷Q12, Q23, Q21), содержащая выходной транзистор 1, база которого подключена к токовому входу 2 активной нагрузки, коллектор - к токовому выходу 3 активной нагрузки, а эмиттер соединен с базой входного 4 транзистора и вспомогательным p-n переходом 5, выходной транзистор 6 эмиттерного повторителя напряжения 7, база которого соединена с токовым выходом активной нагрузки 3, а эмиттер подключен к коллектору вспомогательного транзистора 8 и потенциальному выходу активной нагрузки 9, причем эмиттер вспомогательного транзистора 8 связан с эмиттером входного транзистора 4 и шиной 10 источника питания, а вход 2 активной нагрузки соединен с коллектором входного транзистора 4. Данная структура АН используется также в операционных усилителях 154УДЗ, НА2520 и др., а также в ОУ по патенту US 5512859.

Существенный недостаток известного устройства состоит в том, что оно не обеспечивает единичную передачу по току, что является основной причиной смещения нуля дифференциальных усилителей на его основе.

Основная цель предлагаемого изобретения состоит в повышении точности передачи тока при ненулевом входном токе буферного усилителя. Это позволяет улучшить ряд статических параметров дифференциальных усилителей с АН, стабилизаторов напряжения и т.п.

Поставленная цель достигается тем, что в активной нагрузке дифференциальных усилителей фиг.2, содержащей выходной транзистор 1, база которого подключена к токовому входу 2 активной нагрузки, коллектор - к токовому выходу 3 активной нагрузки, а эмиттер соединен с базой входного 4 транзистора и вспомогательным p-n переходом 5, выходной транзистор 6 эмиттерного повторителя напряжения 7, база которого соединена с токовым выходом активной нагрузки 3, а эмиттер подключен к коллектору вспомогательного транзистора 8 и потенциальному выходу активной нагрузки 9, причем эмиттер вспомогательного транзистора 8 связан с эмиттером входного транзистора 4 и шиной 10 источника питания, а вход 2 активной нагрузки соединен с коллектором входного транзистора 4, предусмотрены новые связи - база вспомогательного транзистора 8 соединена с коллектором входного 4 транзистора.

На фиг.1 показана обобщенная функциональная схема известных АН.

На фиг.2 представлена схема АН-прототипа.

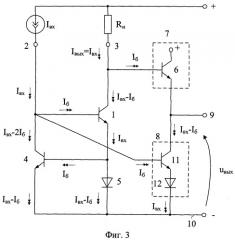

На фиг.3 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

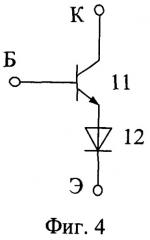

На фиг.4 показан частный случай выполнения вспомогательного транзистора 8 как составного активного элемента.

На фиг.5 - в соответствии с п.3 формулы изобретения вход активной нагрузки 2 связан с коллектором входного транзистора 4 через вспомогательный p-n переход 13.

На фиг.6 представлена схема заявляемой АН (фиг.3) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 представлен график зависимости выходного тока заявляемого устройства от входного.

На фиг.8 показана зависимость относительной погрешности передачи тока заявляемой АН от Iвх.

На фиг.9 представлена другая схема заявляемой АН (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.10 показана зависимость относительной погрешности передачи тока заявляемой АН фиг.5 от Iвх.

На фиг.11 представлена схема операционного усилителя на базе заявляемой АН (фиг.3) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь напряжение смещения нуля ОУ Uсм≈200 мкВ (при отсутствии разброса параметров элементов).

На фиг.12 представлена схема операционного усилителя на базе другой заявляемой АН (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Здесь напряжение смещения нуля ОУ Uсм≈200 мкВ (при отсутствии разброса параметров элементов).

Активная нагрузка дифференциальных усилителей фиг.3 содержит выходной транзистор 1, база которого подключена к токовому входу 2 активной нагрузки, коллектор - к токовому выходу 3 активной нагрузки, а эмиттер соединен с базой входного 4 транзистора и вспомогательным p-n переходом 5, выходной транзистор 6 эмиттерного повторителя напряжения 7, база которого соединена с токовым выходом активной нагрузки 3, а эмиттер подключен к коллектору вспомогательного транзистора 8 и потенциальному выходу активной нагрузки 9, причем эмиттер вспомогательного транзистора 8 связан с эмиттером входного транзистора 4 и шиной 10 источника питания, а вход 2 активной нагрузки соединен с коллектором входного транзистора 4. База вспомогательного транзистора 8 соединена с коллектором входного 4 транзистора.

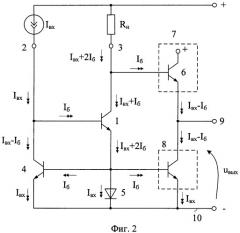

На фиг.4 в соответствии с п.2 формулы изобретения вспомогательный транзистор 8 выполнен в виде составного транзистора на базе основного биполярного транзистора 11 и дополнительного p-n перехода 12, включенного в его эмиттерную цепь.

На фиг.5 в соответствии с п.3 формулы изобретения вход активной нагрузки 2 связан с коллектором входного транзистора 4 через вспомогательный p-n переход 13.

Рассмотрим работу схемы фиг.3.

Если на вход 2 АН фиг.3 подается (от некоторого дифференциального каскада) ток

Iвх, то это создает в элементах схемы токи, показанные на чертеже фиг.3. В результате выходной ток АН Iвых равен входному току независимо от его численных значений. Это является необходимым условием обеспечения нулевого напряжения смещения нуля в ДУ, использующего АН фиг.3 (фиг.11, 12).

В известном устройстве (фиг.2) выходной ток отличается от входного на величину

2Iб, где Iб - ток базы транзисторов схемы при IЭ≈IВХ. То есть погрешность передачи входного тока в АН-прототипе

где β=10÷40 - коэффициент усиления по току базы транзисторов АН.

В схеме фиг.5 также обеспечивается высокий уровень «повторения» входного тока АН: здесь Iвых=Iвх (фиг.10).

Сравнение численных значений погрешности передачи тока известной (1) и предлагаемой АН [фиг.6 (см. фиг.8), фиг.9 (см. фиг.10)] показывает, что заявляемое устройство характеризуется на порядок более высокой точностью.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №1329639

2. Патент США №3681623

3. Патент США №3813607

4. Патент США №3835410

5. Патент США №4008441, H03f 3/16

6. Патент США №4013973

7. Патент США №4030044 (фиг.3)

8. Патент США №4057763

9. Патент США №4095189

10. Патент США №4117417

11. Патент США №4241315

12. Патент США №4345213

13. Патент США №4412186, H03f 3/04

14. Патент США №4462005, H03f 3/04

15. Патент США №4471236

16. Патент США №4473794

17. Патент США №4567444

18. Патент США №4591804, H03f 3/04

19. Патент США №4769619

20. Патент США №4855686

21. Патент США №4879524, H03f 3/26

22. Патент США №4897614

23. Патент США №4937515, G05f 3/26

24. Патент США №4990864

25. Патент США №5053718

26. Патент США №5079518, Н03K 3/16

27. Патент США №5164658

28. Патент США №5357188, G05f 3/26

29. Патент США №5373253

30. Патент США №5394079, G05f 3/16

31. Патент США №5399991

32. Патент США №5512815, G05f 3/16

33. Патент США №5572114

34. Патент США №5633612

35. Патент США №5721512

36. Патент США №5933055

37. Патент США №5969574

38. Патент США №5986507

39. Патент США №6016050

40. Патент США №6570438

41. Патент США №6573795

42. Патент США №6586918

43. Патент США №6606001

44. Патент США №6291977

45. Патент США №6300803

46. Патент США №6528981

47. Патент США №6630818

48. Патент США №6633198

49. Патент США №6639452

50. Патент США №6657481

51. Патент США №6677807

52. Патент США №6680605

53. Патент США №6816014

54. Патент RU 2193273

55. Патентная заявка США 2004/081688

56. Патентная заявка США 2003/0030492

1. Активная нагрузка дифференциальных усилителей, содержащая выходной транзистор (1), база которого подключена к токовому входу (2) активной нагрузки, коллектор - к токовому выходу (3) активной нагрузки, а эмиттер соединен с базой входного (4) транзистора и вспомогательным p-n переходом (5), выходной транзистор (6) эмиттерного повторителя напряжения (7), база которого соединена с токовым выходом активной нагрузки (3), а эмиттер подключен к коллектору вспомогательного транзистора (8) и потенциальному выходу активной нагрузки (9), причем эмиттер вспомогательного транзистора (8) связан с эмиттером входного транзистора (4) и шиной (10) источника питания, а вход (2) активной нагрузки соединен с коллектором входного транзистора (4), отличающаяся тем, что база вспомогательного транзистора (8) соединена с коллектором входного (4) транзистора.

2. Устройство по п.1, отличающееся тем, что вспомогательный транзистор (8) выполнен в виде составного транзистора на базе основного биполярного транзистора (11) и дополнительного p-n перехода (12), включенного в его эмиттерную цепь.

3. Устройство по п.1, отличающееся тем, что вход активной нагрузки (2) связан с коллектором входного транзистора (4) через вспомогательный p-n переход (13).