Система телевидения

Иллюстрации

Показать всеИзобретение относится к технике радиосвязи, может быть использовано для цифрового телевещания. Техническими результатами являются снижение в 3 раза энергоемкости системы по отношению к прототипу и увеличение яркости воспроизводимого изображения. Результаты достигаются передачей информации по одному радиоканалу и приемом ее одним трактом, а также тем, что в систему телевидения на передающей стороне вводится в фотоэлектрический преобразователь матрица ПЗИ, три кодера и передатчик выполняется одноканальным, на приемной стороне имеется один тракт приема и обработки кодов видеосигналов, а устройство отображения видеоинформации представляется плоскопанельным светодиодным экраном. 19 ил., 2 табл.

Реферат

Изобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания.

Прототипом принята "Цифровая система телевидения" [1], содержащая на передающей стороне фотоэлектрический преобразователь /ФЭП/, формирующий три аналоговых цветовых сигнала R, G, В, три АЦП видеосигнала, задающий генератор и синтезатор частот, два АЦП сигнала звука, три формирователя кодов, два самоходных распределителя импульсов /СРИ/ и передатчик радиосигналов из трех каналов, на приемной стороне содержащая блок управления, три тракта приема и обработки кодов видеосигналов, каждый из которых включает блок приема радиосигнала, усилитель радиочастоты, двухполярный амплитудный детектор и канал обработки кодов сигнала /R, G, В/, включающий первый и второй формирователи импульсов, два регистра, блок обработки кодов /удвоения числа отсчетов в строке/, первый блок задержек, сумматор и второй блок задержек, на приемной стороне шесть блоков импульсных усилителей, блок модуляции излучений, блоки строчной и кадровой развертки, два усилителя и два пьезодефлектора, матовый экран, канал формирования управляющих сигналов и два канала звука. На передающей стороне раздельно кодируются сигналы R, G, В в 550-и строках кадра по 1000 отсчетов в строке. Частота кадров 25 Гц, каждый из двух полей. Информация передается тремя каналами, для каждого цветового сигнала свой канал, используются две несущие частоты. Приемная сторона принимает параллельно три радиосигнала тремя трактами, выделяет строчные и кадровые синхроимпульсы ССИ, КСИ, выполняет удвоение числа отсчетов в каждой строке и удвоение числа строк в кадре. Выдерживаем на приемной стороне 2000отсч×1100строк×25 Гц. Изображение воспроизводится электронно-оптической разверткой /строчной и кадровой/ и проецированием кадра на матовый экран. Недостатки прототипа: высокая энергоемкость системы /передача информации по трем каналам и прием ее тремя трактами/, необходимость прецизионной юстировки ФЭП, недостаточная яркость воспроизводимого изображения на матовом экране.

Цель изобретения - уменьшение энергоемкости системы, увеличение яркости воспроизводимого изображения и исключение строчной и кадровой разверток на приемной стороне. Техническими результатами являются снижение в три раза энергоемкости системы, изменение конструкции ФЭП и увеличение яркости воспроизводимого изображения. Технические результаты достигаются передачей информации по одному радиоканалу и приемом ее одним трактом, введением в ФЭП матрицы ПЗИ /прибора с зарядовой инжекцией/, выполненной по технологии Foveon ХЗ [2, с.552], и введением на приемной стороне плоскопанельного светодиодного экрана /СД-экрана/.

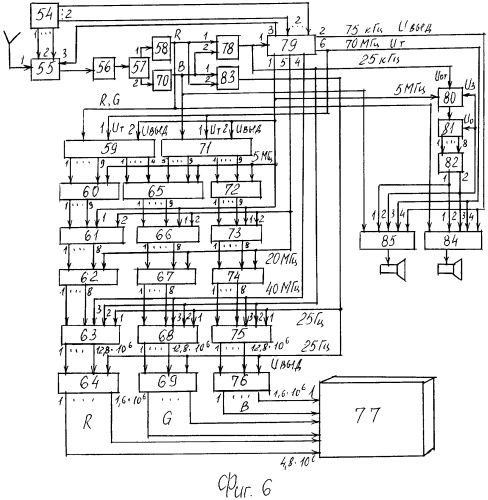

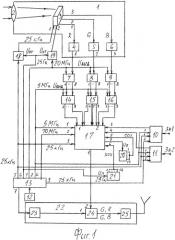

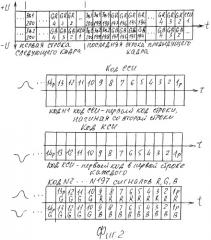

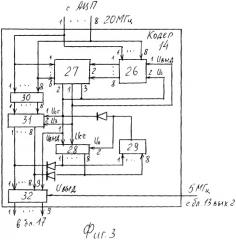

Сущность изобретения в том, что в систему телевидения на передающей стороне вводятся в ФЭП матрица ПЗИ, три кодера и передатчик выполняется одноканальным, на приемной стороне имеется один тракт приема радиосигнала и вводятся два приемных регистра, и в каждый канал цветового сигнала R, G, В вводятся декодер, накопитель кодов кадра и формирователь управляющих сигналов, а устройство отображения видеоинформации представляется плоскопанельным светодиодным экраном. Передающая сторона на фиг.1, структура цифрового штока на фиг.2, кодер на фиг.3, диаграммы работы кодера на фиг.4, формирователь кодов на фиг.5, приемная сторона на фиг.6, спектр амплитудно-модулированного сигнала на фиг.7, двухполярный амплитудный детектор на фиг,8, декодер на фиг.9, блок обработки кодов на фиг.10, накопитель кодов кадра на фиг.11, блок регистров на фиг.12, 13, (формирователь управляющих сигналов на фиг.14, блок выделения кодов ССИ /КСИ/ на фиг.15, СД-ячейка на фиг.16, элемент матрицы на фиг.17, расположение элементов матрицы в СД-экране на фиг.18, временные диаграммы работы системы на фиг.19. На передающей стороне применяется видеорежим 800×1000×25 Гц, где: 800 - число кодируемых отсчетов в строке, 1000 - число кодируемых строк в кадре, 25 Гц - частота кадров. Частота дискретизации при аналого-цифровом преобразовании сигналов R, G, В составляет:

fацп=25 Гц × 1000строк × 800отсч=20 МГц,

частота строк: 25 Гц × 1000стр=25 кГц. При формировании цифрового изображения всегда будут последовательные коды, равные по величине, и чем выше частота дискретизации /20 МГц/, тем равных кодов будет больше. При сжатии потока каждого цветового сигнала кодером принимается нижний коэффициент сжатия, равный 4. При сжатии потока кодов в четыре раза частота дискретизации на выходе каждого кодера будет равна После кодеров формируются два потока кодов: первый состоит из 13-разрядных суммарных кодов, который включает в себя один 9-разрядный код сигнала R и четыре разряда /с 1-го по 4-й/ сигнала G, второй поток состоит из 14-разрядных суммарных кодов, который включает в себя один 9-разрядный код сигнала В и пять разрядов /с 5-го по 9-й/ сигнала G.

Следующий за кодерами формирователь кодов из двух потоков формирует на своем выходе один поток кодов.

Тактовая частота при формировании общего одного потока кодов составляет:

fт=5 МГц × 14=70 МГц,

где: 5 МГц - частота дискретизации кодов в кодерах,

14 - число разрядов в суммарном коде потока.

Период следования кодов в потоке на выходе кодера период следования разрядов в коде 14,28 нс

Несущая частота передатчика принимается:

fн=70 МГц × 15=1050 МГц.

Верхняя боковая частота fв=1050+70 МГц=1120 МГц.

Нижняя боковая частота fнн=1050-70 МГц=980 МГц.

На приемной стороне число отсчетов в строке удваивается, и воспроизводится видеорежим: 1600×1000стр×25 Гц.

Разрешение кадра составляет 1600×1000=1,6×106 пикселов.

Передающая сторона включает /фиг.1/ фотоэлектрический преобразователь 1 /ФЭП/, являющийся датчиком трех основных цветов R, G, B и содержащий объектив 2, в фокальной плоскости которого расположена фоточувствительная сторона матрицы ПЗИ 3 - прибора с зарядовой инжекцией, выполненного по технологии фирмы Foveon ХЗ из трехслойного КМОП-датчика [2, с.552, 3, с.832-835], с оптическим разрешением 1600×1000 и обеспечивающая 24-битную глубину цвета, с первого по третий выводы матрицы ПЗИ 3 подключены соответственно к входам предварительных усилителей 4 /R/, 5 /G/, 6 /В/, передающая сторона включает первый 7, второй 8, третий 9 АЦП видеосигналов, первый 10 и второй 11 АЦП сигнала звука, последовательно соединенные задающий генератор 12 синусоидальных колебаний и синтезатор 13 частот, первый 14, второй 15, третий 16 кодеры, формирователь 17 кодов, первый 18 и второй 19 ключи, первый самоходный распределитель 20 импульсов /СРИ/, формирующий код строчных синхроимпульсов ССИ, второй СРИ 21, формирующий код кадрового синхроимпульса КСИ, и передатчик 22, включающий последовательно соединенные усилитель 23 несущей частоты, амплитудный модулятор 24 и выходной усилитель 25. Амплитудный модулятор 24 состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [4, с.234], в кольцевом модуляторе подавляется несущая частота, полосовой фильтр отфильтровывает нижнюю боковую частоту. Верхняя модулированная боковая частота 1120 МГц с информацией кодов К, G, В блоком 24 выдается в выходной усилитель 25, при стабильности несущей частоты в 10-7 она занимает в эфире полосу ±112 Гц или всего 224 Гц. АЦП 7, 8, 9 выполнены идентично и принимаются без изменений из прототипа [1, c.9, фиг.3]. АЦП 10, 11 сигнала звука принимаются также из прототипа бее изменений [1, с.9, фиг.4]. АЦП 10, 11 преобразуют звуковые сигналы в 14-разрядные коды, которые поступают с дискретизацией 75 кГц с АЦП 10 на третий информационный вход блока 17, с АЦП 11 на четвертый информационный вход блока 17.

Кодеры 14, 15, 16 идентичны, каждый включает /фиг.3/ последовательно соединенные регистр 26, схему 27 сравнения /компаратор/, счетчик 28 импульсов и дешифратор 49, последовательно соединенные блок 30 элементов задержек, блок 31 ключей и буферный накопитель 32 кодов кадра. Информационными входами являются поразрядно объединенные первый-восьмой входы регистра 26, первые входы 1-8 схемы 27 сравнения и входы блока 30 элементов задержек. Выходами являются первый-девятый выходы буферного накопителя 32 кодов кадра, объем которого составляет не менее 200×103 кодов кадра девятиразрядных. Управляющим входом является управляющий вход /5 МГц/ блока 32. Формирователь 17 кодов включает /фиг.5/ четыре канала, первый и второй каналы идентичны. Первый канал включает последовательно соединенные первый блок 33 элементов И, первый 34 и второй 35 элементы ИЛИ, первый выходной ключ 36 и первый СРИ 37, второй канал включает второй блок 38 элементов И, третий 39 и четвертый 40 элементы ИЛИ, второй выходной ключ 41 и второй СРИ 42. Третий канал включает третий блок 43 элементов И, пятый 44 элемент ИЛИ и третий СРИ 45, четвертый канал включает четвертый блок 46 элементов И, шестой элемент ИЛИ 47 и четвертый СРИ 48. Формирователь 17 кодов включает первый 49, второй 50, третий 53 ключи и последовательно соединенные счетчик 51 импульсов и дешифратор 52. Информационными входами блока 17 являются: первым - первые с первого по 14 входы блока 33, содержащего 14 элементов И, вторым - первые с первого по 14-й входы блока 38 элементов И, содержащего 14 элементов И, третьим - первые входы 14-и элементов И блока 43, четвертым - первые входы 14-и элементов И блока 46, пятым - третий вход второго элемента ИЛИ 35, подключенный к выходу СРИ 20 через ключ 53, шестым - третий вход четвертого элемента ИЛИ 40, подключенный к выходу СРИ 21. Первым выходом блока 17 являются объединенные выходы выходных ключей 36, 41, вторым - является третий выход дешифратора 52, подключенный к входу СРИ 20, подавая на его вход сигнал Uп пуска. Управляющими входами блока 17 являются: первым - объединенные входы ключей 49, 50 и счетный вход счетчика 51 импульсов /5 МГц/, вторым - объединенные сигнальные входы /70 МГц/ выходных ключей 36, 41, третьим - управляющий вход /25 кГц/ счетчика 51 импульсов, четвертым - управляющий вход третьего ключа 53 /Uп 25 Гц/. Первый выход дешифратора 52 подключен к первому управляющему входу ключа 49, второй выход его подключен к второму управляющему входу ключа 49 и к первому входу ключа 50, третий выход дешифратора 52 подключен к второму управляющему входу ключа 50 и является вторым выходом блока 17. Вторые входы блоков 33, 38, 43 и 46 подключены соответственно к выходам ПРИ 37, 42, 45, 48.

Выход первого ключа 49 подключен к входам СРИ 37 и 42, выход второго ключа 50 подключен к входам /Uп/ СРИ 45 и 48. Вход третьего ключа 53 является пятым информационным входом блока 17, выход ключа подключен к третьему входу первого элемента ИЛИ 35.

Приемная сторона включает /фиг.6/ антенну, блок 54 управления /выбор каналов/ и тракт приема и обработки кодов видеосигналов, устройство отображения видеоинформации, канал формирования управляющих сигналов и два идентичных канала звукового сопровождения. Тракт приема и обработки кодов видеосигналов производит прием и обработку кодов видеосигналов R, G, В и включает последовательно соединенные блок 55 приема радиосигналов, усилитель 56 радиочастоты и двухполярный амплитудный детектор 57, канал сигнала R, канал сигнала G и канал сигнала В. Канал сигнала R включает последовательно соединенные первый формирователь 58 импульсов, первый приемный регистр 59, содержащий 14 разрядов, регистр 60 сигнала R, декодер 61, блок 62 обработки /удвоения/ кодов, накопитель 63 кодов кадра и формирователь 64 управляющих сигналов. Канал сигнала G включает последовательно соединенные регистр 65 сигнала G, декодер 66, блок 67 обработки /удвоения/ кодов, накопитель 68 кодов кадра и формирователь 69 управляющих сигналов. Канал сигнала В включает последовательно соединенные второй формирователь 70 импульсов, второй приемный регистр 71, содержащий 14 разрядов, регистр 72 сигнала В, декодер 73, блок 74 обработки /удвоения/ кодов, накопитель 75 кодов кадра и формирователь 76 управляющих сигналов. Выходы формирователей 64, 69, 76 управляющих сигналов подключены к соответствующим входам плоскопанельного светодиодного экрана 77 /СД-экрана/. Порядок работы приемной стороны определяет канал формирования управляющих сигналов, включающий последовательно соединенные блок 78 выделения строчных синхроимпульсов /ССИ/, синтезатор 79 частот, ключ 80, счетчик 81 импульсов, дешифратор 82 и блок 83 выделения кадровых синхроимпульсов /КСИ/. Каналы звукового сопровождения 84, 85 идентичны, применяются без изменений, как в прототипе, каждый из них содержит преобразователь кодов звука в аналоговые сигналы /ЦАП/, усилитель мощности и громкоговоритель. Декодеры идентичны, и каждый декодер 31, 66, 73 включает /фиг.9/ последовательно соединенные первый девятиразрядный регистр 86, накопитель 87 кодов кадра емкостью на 200000 9-разрядных кодов /200отсч×1000строк/,второй девятиразрядный регистр 88, первый блок 89 ключей из восьми ключей и третий восьмиразрядный регистр 90, последовательно соединенные второй блок 91 ключей /из восьми ключей/, восьмиразрядный вычитающий счетчик 92 и дешифратор 93, первый 94, второй 95, третий 96 и четвертый 97 ключи. Информационным входом декодера являются первый-девятый входы первого регистра 86, выходом - первый-восьмой выходы третьего регистра 90. Управляющими входами являются: первым - объединенные управляющий вход регистра 86 и сигнальный вход /5 МГц/ третьего ключа 96, вторым - объединенные сигнальные входы /20 МГц/ ключей 94, 95, 97. Выход девятого разряда второго регистра 88 подключен параллельно к первому управляющему входу второго ключа 95, к вторым управляющим входам третьего 96 и четвертого 97 ключей и первого ключа 93, к второму управляющему входу первого блока ключей и к первому управляющему входу второго блока ключей. Выход первого ключа 94 подключен к первому управляющему входу третьего регистра 90, второй управляющий вход которого подключен к выходу второго ключа 95, к которому подключен и счетный вход вычитающего счетчика 92 импульсов, выход дешифратора 93 подключен параллельно к первому управляющему входу первого блока 89 ключей, к второму управляющему входу второго блока 91 ключей, к первым управляющим входам ключей 94, 96, 97 и к второму управляющему входу второго ключа 95. Выход третьего ключа 96 подключен к управляющему входу накопителя 87 кодов кадра, выход четвертого ключа 97 подключен к управляющему входу второго регистра 88. Блоки 62, 37, 74 обработки кодов идентичны, каждый включает /фиг.10/ триггер 98, вход которого является управляющим входом блока, первый 99 и второй 100 блоки ключей /каждый из 8 ключей/, первый 101, второй 102, третий 103, четвертый 104 регистры, сумматор 105, пятый 106 и шестой 107 регистры, выполняющие хранение кодов 50 нс, и 16 диодов. Информационным входом блока обработки кодов являются поразрядно объединенные 1-8 входы блоков 99, 100 ключей. Выходом являются поразрядно объединенные выходы 0-7 сумматора 105 и выходы /1-8/ регистров 106, 107. Входы регистров 101 и 102 поразрядно объединены и подключены к 1-8 выходам первого блока 99 ключей, выходы этих регистров 102 и 101 через диоды поразрядно объединены и подключены к первой группе входов сумматора 105. Входы регистров 103 и 104 поразрядно объединены и подключены к 1-8 выходам второго блока 100 ключей, выходы ключей 104 и 103 через диоды поразрядно объединены и подключены к второй группе входов сумматора 105. Выход 1 триггера параллельно подключен к управляющим входам второго 102, третьего 103 и пятого 106 регистров и к управляющему входу блока 99 ключей. Второй выход триггера 98 подключен параллельно к управляющим входам первого 101, четвертого 104 и шестого 107 регистров и к управляющему входу второго блока 100 ключей. Накопители 63, 68, 75 кодов кадра идентичны, каждый включает /фиг.11/ блоки 108 регистров по числу строк в кадре 1081-1000.

Информационным входом накопителя кодов кадра являются поразрядно объединенные 1-8 входы всех блоков 108 регистров. Выходами являются выходы всех блоков регистров 108, всего выходов 12,8×106 /1600×8×1000/. Управляющими входами являются: первым - первый управляющий вход Uк /25 Гц/ первого блока 1081 регистров, вторым - объединенные вторые управляющие входы блоков 108 регистров /25 кГц/, третьим - объединенные третьи управляющие входы Uд /40 МГц/ блоков 108 регистров. Управляющий выход каждого предыдущего блока регистров является первым управляющим входом для каждого последующего блока 108 регистров. Управляющий выход последнего /1000-го/ блока 108 регистров подключен параллельно к четвертым управляющим входам всех блоков 108 регистров. Блоки 108 регистров идентичны, каждый включает /фиг.12, 13/ первый 109 и второй 110 ключи, распределитель 111 импульсов и восемь регистров 1121-8, каждый из которых включает по 1600 разрядов /по числу отсчетов в строке/. Информационными входами блока регистров являются поразрядно объединенные с первого по восьмой третьи входы разрядов восьми регистров 112. Выходами являются параллельные выходы всех разрядов /1600/ восьми регистров, всего выходов с блока 108 12800 /1600×8/. Выходы 1000 блоков регистров являются выходами каждого блока накопителя кодов 63, 68, 75 - 12,8×106. Управляющими входами блока 108 регистров являются: первым - первый управляющий вход /25 Гц/ первого ключа 109, вторым - сигнальный вход Uвыд /25 кГц/ второго ключа 110, третьим - сигнальный вход Uд /40 МГц/ первого ключа 109, четвертым - первый управляющий вход второго ключа 110. Последний выход /1600/ блока 111 является управляющим выходом каждого блока 108, подключен к первому управляющему входу первого ключа 109 в следующем блоке 108 регистров. Выход первого ключа 109 подключен к входу распределителя 111 импульсов, выходы которого последовательно, начиная с первого, подключены к первым /тактовым/ входам разрядов параллельно восьми регистров 112. Выход второго ключа подключен параллельно к вторым входам разрядов восьми регистров 112 и к второму управляющему входу своего 110 ключа, прошедший один импульс Uвыд закрывает ключ 110. Выходы накопителей 63, 66, 75 кодов кадра подключены /фиг.6/ к информационным входам своих формирователей 64, 69, 76 управляющих сигналов, назначение которых выполнять преобразование "код - число импульсов излучений" для каждого поступающего кода, формируя скважность излучений светодиодов за период кадра. Каждый из блоков 64, 68, 76 включает преобразователи "код - число импульсов излучений" по числу отсчетов в строке /1600/ и числу отрок /1000/ в кадре, т.е. 1,6×106. Блоки 64, 69, 76 идентичны, каждый включает /фиг.14/ блок 113 формирователей импульсов, содержащий идентичные схемы формирования импульсов по числу преобразователей 1,6×106, вход блока 113 является управляющим входом /25 Гц/ блока 64 /69, 76/ и включает преобразователи "код - число импульсов излучений", которых по числу разрешения кадра 1,6×106. Каждый преобразователь включает последовательно соединенные дешифратор 114, информационные входы которого 1-8 являются информационными входами преобразователя, блок 115 ключей из 255 ключей и выходной ключ 116, включает самоходный распределитель 117 импульсов /СРИ/, вход /Uп/ которого подключен к соответствующему выходу в блоке 113, а 255 выходов 255 разрядов которого подключены к сигнальным входам соответствующих ключей в блоке 115, и включает источник питания 118, 255 выходов дешифратора 114 подключены к первым управляющим входам /Uот/ 255 ключей блока 115, выходы которых объединены, объединенный выход подключен к управляющему входу /Uот/ выходного ключа 116, сигнальный вход которого подключен к выходу источника 118 питания. Информационными входами блока 64 являются информационные входы всех дешифраторов 114, выходами являются выходы выходных ключей 116. Исходное состояние выходных ключей 116 и ключей в блоках 115 закрытое.

На управляющий вход /25 Гц/ блока 113 поступает сигнал Uк /25 Гц/, который параллельно поступает на входы схем формирователей импульсов, формирующих импульсы Uп соответствующей амплитуды и длительности для СРИ 117. С приходом кода на входы дешифратора 114 сигналы с его соответствующих выходов открывают соответствующие ключи в блоке 115, через которые проходят сигналы с выходов соответствующих разрядов СРИ 117 и поступают на управляющий вход Uот выходного ключа 116, который в открытом состоянии запитывает свой светодиод в СД-экране. Световые импульсы светодиодов одной длительности. Выходной ключ 116 открывается каждый раз на длительность 156 мкс , 40 мс длительность кадра, 255 - разрешение 8-разрядного кода, т.е. число выходов с блока 117. Светодиод за период кадра через равные интервалы времени выдает число импульсных излучений пропорционально величине кода цветового сигнала. Чем больше код, тем больше импульсных излучений за период кадра. Пример распределения импульсов излучений за кадр соответственно величинам кодов в таблице I.

| Таблица 1 | |||||||||

| Код на входе блока 114 | Распределение импульсов излучений в периоде кадра | Число излучений | |||||||

| 00000000 | 00… | 000 | 0 | ||||||

| 00000001 | 00… | 128 | 00 | 1 | |||||

| 00000010 | 00… | 88 | 176 | 00 | 2 | ||||

| 00000011 | 00… | 64 | 128 | 192 | 00 | 3 | |||

| . | . | . | |||||||

| . | . | . | |||||||

| . | . | . | |||||||

| 11111110 | 1,2,3,4… | 254 | 00 | 254 | |||||

| 11111111 | 1,2,3,4… | 254 | 255 | 255 | |||||

| 0 - отсутствие излучения, | |||||||||

| 1,2,3 - 255 - номера следования импульсов излучений в периоде кадра. |

Следование импульсов излучений в периоде кадра через равные интервалы времени способствует естественному восприятию изображения зрением человека по достоверности цветопередачи и по яркости. Инерционность светодиодов должна быть до 1 мкс. С окончанием периода кадра в блоках 63, 68, 75 сосредотачиваются все коды кадра сигналов R, G, В, которые с приходом сигнала с последнего блока 1081000 регистров /фиг.11/ выдаются в формирователи 64, 69, 76 управляющих сигналов, в которых вое коды параллельно преобразуются в число импульсов излучений светодиодами СД-экрана. Современные технологии в электронике позволяют выполнить каждый из блоков 63, 68, 75 и 64, 69, 76 одной микросхемой. Плоскопанельный СД-экран 77 представляет совокупность излучающих элементов в матрице по числу разрешения кадра 1,6×106, которые выполняются в стекле /или другом соответствующем материале/ СД-экрана 77, СД-экран включает экранное стекло и матрицу из излучающих элементов по числу разрешения кадра. Каждый излучающий элемент включает три светодиодных ячейки /СД-ячейки/, каждая ив которых излучает один из основных цветов R, G, В. СД-ячейка содержит /фиг.16/ светодиод 122 белого свечения и соответствующий цветной светофильтр 123. Три СД-ячейки составляют излучающий элемент матрицы /фиг.17/, расположение элементов матрицы и СД-ячеек в экране на фиг.18. Уровень яркости излучения СД-ячейки воспринимается зрением пропорционально числу импульсов излучений светодиода за период кадра, которых может быть от одного /156 мкс/ до 255 /40 мс/. Суммарное излучение трех основных цветов тремя СД-ячейками формирует и яркость, и цветовой тон одного пиксела на экране. В качестве светодиодов /по мере готовности технологии их изготовления/ могут применяться светодиоды с полимерными органическими молекулами - светодиоды технологии СДТ /или РLЕД/ [5, c.43], или сверхъяркие светодиоды фирм "Nichia", "Ledtronics" [6, с.47]. Светодиоды как технологии CДТ, так и сверхъяркие исполняются в экранном материале методом микроэлектронной технологии. Размеры сверхъярких светодиодов принимаются диаметром в 0,5 мм /фиг.16/, размер одного излучающего элемента в этом случае будет 1×1 мм /фиг.17/, а размер СД-экрана 77 составит:

по горизонтали 1600×1 мм=1600 мм,

по вертикали 1000×1 мм=1000 мм,

по диагонали 188 см или 74".

Блок 78 выделения строчных синхроимпульсов ССИ и блок 83 выделения кадровых синхроимпульсов /КСИ/ идентичны, каждый включает /фиг.15/ счетчик 119 импульсов, дешифратор 120, элемент НЕ 121 и два диода. Счетчик 119 4-разрядный. Информационным входом блока 78 /83/ является - ее счетный вход 1 счетчика 119 импульсов, управляющим входом является управляющий вход 2 счетчика 119, который через диод подключается к выходу второго формирователя 70 импульсов /фиг.6/. В блоке 83 выделения КСИ информационный вход блока подключается к выходу формирователя 70 импульсов, а управляющий вход также через диод подключается к выходу формирователя 58 импульсов. Выходом блока 78, 83 является выход дешифратора 120, который через диод подключен и к выходу элемента НЕ 121, и вместе они подключены к управляющему входу счетчика 119 импульсов после диода. Код ССИ представляется 14-разрядным кодом из одних единиц. Код КСИ является также 14-разрядным кодом из 14 единиц. Код ССИ поступает на счетный вход блока 78, код КСИ поступает на счетный вход блока 83 с формирователя 70 импульсов, а управляющий вход блока 83 подключен к выходу блока 58.

Работа блоков 78 /83/, фиг.15.

С поступлением кода ССИ на счетный вход счетчика 119 он ведет счет 14 импульсов подряд /код 1110/. В результате на выходах первого-третьего разрядов счетчика 119 появляются сигналы, которые дешифрируются дешифратором 120, и на выходе блока 78 появляется строчный синхроимпульс ССИ. При поступлении кода ССИ на счетный вход счетчика 119 с выхода блока 70 /фиг.6/ импульсов кода нет /фиг.2/. Начиная с второго кода строки с блока 70 пойдут коды на управляющий вход 2 счетчика 119, и с приходом каждой единицы кода счетчик 119 будет обнуляться и не сможет достигнуть счета 14 /1110/. Параллельно и на счетный вход счетчика 119 также идут с блока 58 коды, в которых всегда есть и единицы, и нули, а по каждому нулю элемент НЕ 121 выдает сигнал, который тоже обнуляет счетчик 119 импульсов. В добавление при выходе ССИ с выхода дешифратора 120 он через диод поступает и на управляющий вход счетчика 119 и обнуляет его. Таким образом, схема блока 78 /83/ исключает появление на выходе ложного сигнала ССИ /КСИ/. В блоке 83 при поступлении с формирователя 70 импульсов кода КСИ на счетный вход счетчика 119 на выходах 1-3 разрядов счетчика 119 появляются сигналы, которые дешифрируются блоком 120, и на выходе блока 83 появляется кадровый синхроимпульс КСИ. При поступлении кода КСИ на счетный вход блока 83 на его управляющий вход с выхода блока 58 импульсы не идут. Далее работа блока 83 аналогична работе блока 78. Фотоэлектрический преобразователь 1 матрицей ПЗИ 3 формирует три аналоговых видеосигнала основных цветов. Объектив 2 создает изображение в фокальной плоскости, в которой расположена фоточувствительная сторона матрицы ПЗИ 3. Оптическое разрешение матрицы не менее 800×1000строк. Матрица ПЗИ выполнена трехслойной по технологии ХЗ [3, c.832]. Ha каждый из трех слоев матрицы ПЗИ с ключа 18 поступают импульсы 25 кГц частоты строк для считывания сигналов пикселов по вертикали, на второй вход матрицы ПЗИ с ключа 19 поступают импульсы 20 МГц для считывания сигналов R, G, В пикселов по горизонтали [3, с.832]. Аналоговые сигналы с матрицы ПЗИ 3 поступают на входы предварительных усилителей 4, 5, 6, с выходов которых поступают на входы AЦП соответственно 7, 8, 9, с выходов которых 8-разрядные коды цветовых сигналов с дискретизацией 20 МГц поступают на входы своих кодеров 14, 15, 16. Синхронизация считывания сигналов с матрицы ПЗИ выполняется сигналом частоты кадров 25 Гц открытием ключей 18, 19 на длительность кадра 40 мс. Синтезатор 13 частот выдает с первого выхода импульсы 20 МГц дискретизации кодов в АЦП 7-9 и на сигнальный вход ключа 19, со второго выхода импульсы 5 МГц сигналы Uвыд с кодеров 14-15, с третьего выхода импульсы 75 кГц дискретизации кодов звука, с четвертого - тактовые импульсы 70 МГц для формирователя 17 кодов, с пятого - импульсы 25 кГц частоты строк на сигнальный вход ключа 18, на третий вход блока 17 и на третьи входы АЦП 10, 11, с шестого выхода импульсы 25 Гц частоты кадров на управляющие входы ключей 18, 19, с седьмого выхода синусоидальные колебания несущей частоты 1050 МГц в передатчик 22 со стабильностью 10-7. АЦП 7, 8, 9 преобразуют аналоговые сигналы в 8-разрядные коды, поступающие в параллельном виде в кодеры 14, 15, 16.

Работа кодеров, фиг.3.

8-разрядные коды в параллельном виде поступают на 1-8 входы регистра 26, на первые входы схемы сравнения 27 и на входы блока 30 элементов задержек. Исходное состояние ключей в блоке 31 открытое. Код в блоке 30 задерживается на время срабатывания схемы сравнения /18 нс/ и поступает через открытые ключи блока 31 на 1-8 входы буферного накопителя 32 кодов кадра емкостью 200×103 9-разрядных кодов. Схема сравнения 27 выполняет сравнение по величине каждого предыдущего и последующего кодов с целью выявления их равенства или неравенства. При следовании неравных кодов они проходят через блок 30, открытые ключи блока 31 и поступают на первый - восьмой входы буферного накопителя 32 кодов. Выдача кодов из блока 32 выполняется сигналом Uвыд 5 МГц с выхода 2 блока 13. Поступление кодов в блок 32 при следовании неравных кодов идет с частотой 20 МГц. В общем потоке кодов имеется большое число и равных по величине кодов. Кодер выполняет сжатие потока кодов с плавающим коэффициентом от 1 до 255. Наименьший общий коэффициент сжатия принимается равным 4, поэтому частота выдачи кодов с блока 32 и принимается в 5 МГц . При коэффициенте сжатия выше 4 эта частота 5 МГц выдачи будет тем более удовлетворять. Схема 27 сравнения выполняет сравнение кодов по величине и представляется двумя микросхемами 530CП1 с временем срабатывания 18 нс [9, c.279]. При неравенстве А>В появляется сигнал на выходе 2 блока 27 /в микросхеме выход 5 [9 c.272 рис.2.190]/, при равенстве кодов А=В сигнал с выхода 1 /в микросхеме выход 7/. При равенстве кодов сигнал с выхода 1 блока 27, закрывает ключи в блоке 31, поступает счетным импульсом в счетчик 28 импульсов и как сигнал Uвыд на первый управляющий вход регистра 26. Счетчик 28 производит счет импульсов с выхода 1 блока 27, пока идут коды, равные по величине. Счетчик 28 восьмиразрядный, максимальный код в нем 11111111 /255/, отсюда и максимальный коэффициент сжатия 255. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [9, c.428]. При появлении неравных кодов со схемы 27 следует сигнал с выхода 2 или 3 /А<В/, которые объединены, сигнал с них используется для выдачи кода числа равных кодов из счетчика 28 через диоды в 1-8 входы блока 32 и для заполнения в блоке 32 девятого разряда, с которого сигнал используется для опознания по нему кода числа равных кодов при декодировании. Этот же сигнал открывает ключи в блоке 31 /вход 1/ и обнуляет регистр 26 вход 2. Выданный перед этим с блока 32 код является первым кодом последовательности, по диаграмме I фиг.4 они помечены крестиками. Коды, равные по величине и подсчитанные счетчиком 28, исключаются из потока, диаграмма III фиг.4, за счет их и идет сжатие. Емкость буферного накопителя 32 кодов соответствует числу 9-разрядных кодов в кадре /200×103/ для обеспечения темпа следования с частотой 5 МГц. При следовании подряд кодов, равных по величине, более 255 в работу вступает дешифратор 29. При коде 11111111 дешифратор 29 выдает сигнал, который одновременно открывает ключи в блоке 31 /вход 1/, обнуляет регистр 26, сигналом Uвыд выдает код из счетчика 28 /вход 1/ и обнуляет счетчик /вход 2/, а в девятый разряд блока 32 поступает сигнал опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы сравнения 27, которая обеспечивает до 40 Мбайт/с, и удовлетворяет требуемой 20 Мбайт/с. С выходов кодеров 14, 15, 16 коды в параллельном виде поступают на первый и второй информационные входы формирователя 17 кодов, который /фиг.5/ первым кодом в строке выдает код ССИ, из сжатого потока кодов формирует и выдает со второго по 197-й коды сигналов R, G, В и затем три кода сигнала звука /198, 199, 200-й отсчеты строки/, фиг.2. Код КСИ является первым кодом строки только в первой строке каждого кадра, при этом коде сигнала ССИ нет. Код ССИ является в каждой строке первым, начиная со второй строки, при этом нет кода КСИ /фиг.2/. Единицы кода R и 1-4 разряды кода G представляются на выходке блока 17 положительными полусинусоидами моночастоты 70 МГц, единицы в кодах В и 5-9 разрядах кода G единицы представляются отрицательными полусинусоидами той же частоты 70 МГц.

Работа формирователя 17 кодов, фиг.5.

Временные диаграммы работы блока 17 на фиг.19. Блок 17 преобразует параллельные коды в последовательные и заменяет в них представление единиц с импульсов на положительные и отрицательные полусинусоиды. На первый информационный вход в блок 33 поступают 1-9 разряды кода R и 1-4 разряды кода G, на второй информационный вход в блок 38 поступают 5-9 разряды кода G и 1-9 разряды кода В, на третий информационный вход в блок 43 поступают 1-14 разряды сигнала звука с АЦП 10 3в1, на четвертый - в блок 46 поступают 1-14 разряды второго сигнала звука с АЦП 11 3в2. На вторые входы элементов И блоков 33, 38 поступают последовательно 14 импульсов с выходов СРИ 37, 42, сигнал пуска Uп на которые поступает с первого ключа 49. С выходов блоков 33 и 38 импульсы кодов последовательно через элементы ИЛИ 34, 35 и 39, 40 поступают на управляющие входы выходных ключей 36, 41 и открывают их на время своей длительности 14,3 нс . Выходной ключ 36 в открытом состоянии пропускает одну положительную полусинусоиду на выход, выходной ключ 41 в открытом состоянии пропускает на выход одну отрицательную полусинусоиду. Выходы ключей объединены и являются первым выходом блока 17, выходной сигнал с которого представляется полными или неполными синусоидами моночастоты 70 МГц со стабильностью 10-7. Очередность следования кодов в строке определяется счетчиком 51 импульсов и дешифратором 52. Счетчик 51 8-разрядный, ведет счет импульсов строки 5 МГц с 1-го по 200-й. При коде 00000001 импульс с первого выхода дешифратора 52 открывает ключ 49. При этом открытый ключ 49 пропускает импульсы 5 МГц, идет формирование кодов строки со второго отсчета по 197-й. С приходом на вход счетчика 51 197-го импульса сигнал со второго выхода дешифратора 52 закроет ключ 49 и открывает ключ 50, при этом формируются три кода 3в1 и три кода 3в2. Импульсы кода 3в1 с элемента ИЛИ 44 поступают на второй вход элемента ИЛИ 35 и открывают на время своей длительности ключ 36, импульсы кода 3в2 с элемента ИЛИ 47 поступают на второй вход элемента ИЛИ 40 и открывают на время своей длительности /14 нс/ выходной ключ 41. С приходом в счетчик 51 200-го импульса строки с третьего выхода дешифратора 52 импульс закрывает ключ 50 и как сигнал пуска Uп запускает СРИ 20, выдающий последовательный код из 14 единиц код ССИ на третий вход элемента ИЛИ 35, код ССИ проходит через открытый ключ 53, который закрывается импульсом 25 Гц кадра только на время 200 нс, когда идет код КСИ с СРИ 21 на третий вход элемента ИЛИ 40. По окончании периода кадра очередной кадровый импульс КСИ закрывает ключ 53 на длительность 200 нс /14,28 нс×14 разр/ и передним фронтом запускает СРИ 21, который выдает 14-и разрядный код КСИ. Сигналы КСИ представляются на выходе блока 17 14-ю отрицательными полусинусоидами, сигналы ССИ представляются 14-ю положительными полусинусоидами. Когда идет код ССИ, нет кода КСИ, и наоборот, при коде КСИ нет кода ССИ. Радиосигналы на приемной стороне принимаются блоком 55 /фиг.6/, являющимся селектором каналов с электронной настройкой. Блок 55 включает входную цепь, усилитель радиочастоты и смеситель. Радиочастотный сигнал через петлю связи поступает на смеситель, на второй вход которого с синтезатора 79 частот /вход 3/ подается частота, равная несущей частоте передатчика 22, необходимая для детектирования однополосного сигнала [7, с.146]. Сигнал со смесителя, являющийся выходным сигналом блока 55, поступает на вход усилителя 56 радиочастоты, где усиливается до необходимой величины и поступает на вход двухполярного амплитудного детектора 57, выполненного по схеме на фиг.8. Диод Д1 выделяет положительную огибающую модулирующего сигнала /фиг.19, диагр.9/. Диод Д2 из модулирующей выделяет огибающие положительных полусинусоид - символы единиц сигнала R и 1-4 разряды сигнала G. Диод Д3 из модулирующей выделяет огибающие отрицательных полусинусоид - символы единиц сигнала В и 5-9 разрядов сигнала G. С первого выхода блока 57 продетектированные положительные полусинусоиды частоты 70 МГц поступают на вход первого формиро