Устройство для формирования и хранения вычетов чисел

Иллюстрации

Показать всеРеферат

a - ° ал

4ф лмв1ттзвчав о-hei. т аущф

МЮЙива рд ф Я, О П И С А Ы И Е 236853

ИЗОБРЕ ТЕ Ы И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства М

Заявлено 30.Х,1967 (№ 1194091/18-24) Кл. 42Ш, 5,02 с присоединением заявки ¹

Приоритет

МПК Ст 061

Комитет по делам изобретений и открытий при Совете Министров

СССР

УДК 681.325.53:681..3.047

Опубликовано 03.1 I.1969. Бюллетень Л 7

Дата опубликования описания 1 VII.1969

Авторы изобретения

Б. И. Добрянский и О. В. Михайловский

Заявитель

Институт горной механики и технической кибернетики им. М. М. Федорова

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ И ХРАНЕНИЯ

ВЫЧЕТОВ ЧИСЕЛ

Предлагаемое устройство относится к области цифровой вычислительной техники и может быть использовано в контрольны: с: ем ах цифровых вычислительных машин для числового и цифрового контроля передач и ооработки информации.

Известны устройства для формирова;II:I I;l iчетов чисел по модулю вида 2 " — 1, предст",âляющие собой пирамидальную схему, состоящую из п4п — 1 сумматоров по моду.11о 2 " — 1, каждый из которых имеет 2 т входов и тл выходов.

Недостатком известных устройств является их громоздкость и невозможность оперативно изменять модуль, по которому вычисляется вычет.

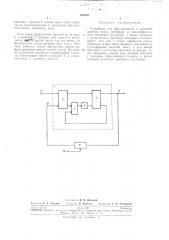

Предлагаемое устройство отличается от известных тем, что оно содержит последовательный двоичный сумматор и линию задержки с управляемым временем задержки.

На чертеже дана блок-схема предлагаемого устройства.

Оно состоит из последовательного двои шого сумматора 1, составленного из двух полусумматоров 2 и 8, линии задержки 4 на од1ш такт, схемы «ИЛИ» 5 и линии задержки 6, включенной в цепь обратной связи с выхода

7 второго полусумматора 8 на вход 8 первого полусумматора 2.

Величина задержки выбирается таким ооразом, чтобы сумматор 1 и линия задержки

6 в л мме предсгавляли задержку иа л1 тактов (такт — зремя между поступлениями

5 двуx соседни: разрядов кода) .

Работа схемы основана иа теореме о том, что для модулей вида 2" —; вычет числа по этому модулю равен вычету суммы цифр по этому же модулю, если рассматривать код как

10 шсло в 2" -ичной системе счисления.

Число, для которого определяется вычет, поступает на вхо l, 9 устройства, начиная с

М младших разрядов. Первые лт разрядов складываются с нулем, поступающим по пепи об15 ратной связи на вход 8, а каждые последующие л1 разрядоз складываются с суммой предыдмщих, подаваемых по цепи обратной связи. При этом проис.,одит суммирование по мо lx;IIo 2" — 1, та1 . 1 ак Ilpll возни1 .иовении Во

20 время очередного суммирования в коде суммы разряда 2" этот разряд, задержаиньш иа

TBI T Il1111iCii. задержки 4, гlрибав l5ieTC)l и младшему разряду суммы, т. е, происходит отбрасывание вели иш, равных 2 " — 1.

25 1ч Количество разрядов в коде должно быть кратным л1. При невыполнении этого требования знаковый разряд дублируется до заполнения последней группы из л1 разрядов.

Черсз m тактов после прохождения числа, 30 необходимых для выполнения внутренних пе236853

Предмет изобретения г-, 1

Х

10 о

Составитсль В. М. Шумский

Редактор Л. A. Утехина Тсхрсд Т. П. Курилко Корректор Г. И. Плешакова

3а),аз 1178 12 1 ира)к 480 Подписное

Ц11ИИПИ Комитета по дс:i..м изопрстсиий tt открытий при Сопстс Министров СССР

))1оскии, I ILII I 1), ttp. (ерова, д, 4

1 и!)огр аЧ) и5« Ilj). C ) tt ltot))1, 2

peHocotj, c выхода 7 Ito>«tto cttst r ttt.t teI >Iot o tticла, представленный )т1 разрядаъ1и пос,1сдоватсльного двои ного кода.

Если через .щсло,.тактов, кратное 111, иа вход

9 устройства,"в котором уже хранится вычет числа, AKFaIt другое число или его вычет, то формируется сучма вычетов двух чисел. IIptt этом работает схема аналоп)чио работе по формированшо вычета одного числа. IIB в од

10 устройства подаются управляю1цие сигналы, изменяющие время задержки 6, а следовательно, it значсн 1е модуля.

Устройство для формирования 11 хранения вычетов чисел, состоящее из последователь5 ного двоичного сумматора и лишш задержки с управляемыч временем задер)кки, от.1ача(ощееея тем, что, с целью упрощения схем1>1, снижения затрат оборудования и возз1ожности суммирования вычетов чисел, в нем выход

10 двоичного сумматора соед шен со входом линии задержки, второй вход которой соединен с датчиком управляющего сип1ала, а выход соединен со входом двоичного сумматора.