Система и способ перемежения

Иллюстрации

Показать всеИзобретение предназначено для осуществления перемежения каналов в системе беспроводной связи. Заявлены система и способ для частотного разнесения, которые используют перемежение. Поднесущие чередования перемежаются способом реверсирования битов, и чередования перемежаются способом реверсирования битов. Технический результат - повышение эффективности в условиях многолучевого распространения. 4 н. и 3 з.п ф-лы, 8 ил.

Реферат

Притязание на приоритет

Настоящая заявка на патент испрашивает приоритет предварительной патентной заявки 60/592,999 под названием "Способ перемежения каналов в системе беспроводной связи OFDM" от 29 июля 2004 г., права на которую принадлежат заявителю настоящего изобретения и которая тем самым явно включена здесь путем ссылки.

Предшествующий уровень техники

Область техники

Настоящие раскрытые варианты осуществления относятся в общем к беспроводной связи и более определенно - к перемежению каналов в системе беспроводной связи.

Предшествующий уровень техники

Мультиплексирование с ортогональным частотным разделением каналов (OFDM) представляет собой методику широковещательной передачи цифровых сигналов высокой скорости передачи. В системах OFDM отдельный поток данных высокой скорости передачи разделяется на несколько параллельных подпотоков данных низкой скорости передачи, где каждый подпоток используется для модулирования соответствующей поднесущей частоты. Следует отметить, что хотя настоящее изобретение описано в отношении квадратурной амплитудной модуляции, оно в равной степени применимо к системам модуляции посредством фазовой манипуляции.

Методика модуляции, используемая в системах OFDM, упоминается как квадратурная амплитудная модуляция (КАМ), в которой модулируются и фаза, и амплитуда несущей частоты. В модуляции КАМ комплексные символы КАМ генерируются из множества битов данных, где каждый символ включает в себя составляющую вещественного числа и составляющую мнимого числа и где каждый символ представляет множество битов данных, из которых он был сгенерирован. Множество битов КАМ передаются вместе в кодовой комбинации, которая может быть графически представлена комплексной плоскостью. Как правило, кодовая комбинация упоминается как "совокупность". Благодаря использованию модуляции КАМ система OFDM может улучшать свою эффективность.

Случается, что когда сигнал является сигналом широковещательной передачи, он может распространяться к приемнику больше чем одним путем. Например, сигнал от единственного передатчика может распространяться к приемнику по прямой линии и он также может отражаться от физических объектов, распространяясь к приемнику по другому пути. Кроме того, случается, что когда система использует так называемую методику "сотовой" широковещательной передачи, чтобы увеличить спектральную эффективность, сигнал, предназначенный для приема, может передаваться посредством широковещательной передачи больше чем одним передатчиком. Следовательно, один и тот же сигнал будет передаваться к приемнику больше чем по одному пути. Такое параллельное распространение сигналов, является ли оно искусственным (то есть вызванным широковещательной передачей одного и того же сигнала больше чем от одного передатчика) или естественным (то есть вызванным эхо-сигналом), называется "многолучевым распространением". Можно с готовностью оценить, что хотя сотовая цифровая широковещательная передача со спектральной точки зрения является эффективной, должны быть выполнены некоторые условия, чтобы эффективно обратить внимание на соображения многолучевого распространения.

К счастью, системы OFDM, которые используют модуляцию КАМ, более эффективны в присутствии условий многолучевого распространения (которые, как заявлено выше, должны возникать, когда используются методики сотовой широковещательной передачи), чем методики модуляции КАМ, в которых используется только одна несущая частота. Более конкретно, в системах КАМ с единственной несущей должен использоваться комплексный выравниватель, чтобы уравнивать каналы, которые имеют эхо-сигналы столь же сильные, как первичный путь, и такое уравнивание трудно выполнять. Напротив, в системах OFDM потребность в комплексных выравнивателях может быть совершенно устранена посредством простого введения защитного интервала соответствующей длины в начале каждого символа. Соответственно, когда ожидаются условия многолучевого распространения, предпочтительными являются системы OFDM, которые используют модуляцию КАМ.

В типичной схеме решетчатого кодирования поток данных кодируется с помощью сверхточного кодера, а затем последовательные биты объединяются в группе битов, которая становится символом КАМ. В группе находится несколько битов с количеством битов в группе, определяемым целым числом m (следовательно, каждая группа упоминается как имеющая m-ичный размер). Как правило, значение m составляет четыре, пять, шесть или семь, хотя оно может быть больше или меньше.

После группирования битов в многоразрядные символы, эти символы перемежаются. Под термином "перемежение" подразумевается, что поток символов перестраивается в последовательности, чтобы таким образом рандомизировать потенциальные ошибки, вызываемые ухудшением характеристик канала. Чтобы проиллюстрировать это, предположим, что должны быть переданы пять слов. Если во время передачи неперемежаемого сигнала в канале возникают временные помехи, может быть потеряно целое слово, прежде чем помехи в канале уменьшатся, и может быть трудно узнать, если не невозможно, какая информация была передана этим потерянным словом.

Напротив, если буквы этих пяти слов до передачи последовательно перестроены (то есть подвергнуты "перемежению") и в канале возникают помехи, несколько букв могут быть потеряны, возможно, по одной букве в слове. Однако после декодирования перестроенных букв все пять слов могут появиться, хотя с несколькими пропущенными буквами в словах. Должно быть понятно, что при этих обстоятельствах было бы относительно просто для цифрового декодера восстановить данные, по существу, полностью. После перемежения m-ичных символов символы отображаются в комплексные символы с использованием отмеченных выше принципов КАМ, мультиплексируются в их соответствующие каналы поднесущих и передаются.

Краткое описание чертежей

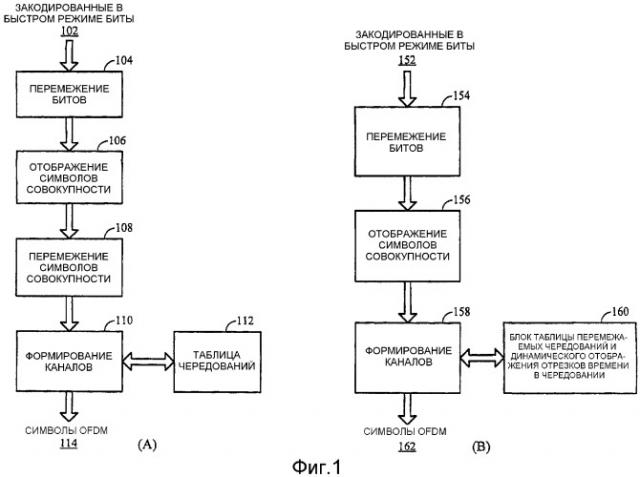

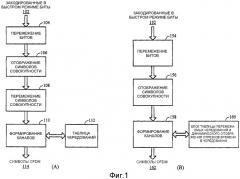

Фиг. 1А показывает устройство перемежения каналов в соответствии с вариантом осуществления;

фиг. 1В показывает устройство перемежения каналов в соответствии с другим вариантом осуществления;

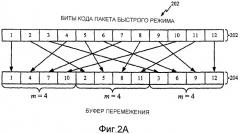

фиг. 2А показывает биты кода пакета быстрого режима, размещенного в буфере перемежения, в соответствии с вариантом осуществления;

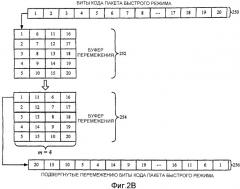

фиг. 2В показывает буфер устройства перемежения, выполненный в виде матрицы из N/m строк на m столбцов, в соответствии с вариантом осуществления;

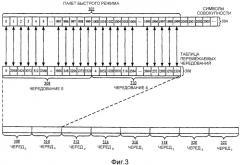

фиг. 3 иллюстрирует таблицу перемежаемых чередований в соответствии с вариантом осуществления;

фиг. 4 показывает схематическое изображение формирования каналов в соответствии с вариантом осуществления;

фиг. 5 показывает схематическое изображение формирования каналов с последовательностью смещения всех единиц, приводящей к продолжительным периодам оценок хороших и плохих каналов для конкретного отрезка времени, в соответствии с вариантом осуществления;

фиг. 6 показывает схематическое изображение формирования каналов с последовательностью смещения всех двоек, приводящей к равномерно распространенным чередованиям оценок хороших и плохих каналов;

фиг. 7 показывает беспроводное устройство, выполненное с возможностью реализации перемежения в соответствии с вариантом осуществления.

Подробное описание

В варианте осуществления устройство перемежения каналов содержит устройство перемежения битов и устройство перемежения символов. Фиг. 1 показывает два типа схем перемежения каналов. Обе схемы используют перемежение и чередование битов для достижения максимального разнесения каналов.

Фиг. 1А показывает устройство перемежения каналов в соответствии с вариантом осуществления. Фиг. 1В показывает устройство перемежения каналов в соответствии с другим вариантом осуществления. Устройство перемежения фиг. 1В использует исключительно устройство перемежения битов для достижения разнесения m-ичной модуляции и использует двумерную таблицу перемежаемых чередований и отображение чередования отрезков времени в чередование во время выполнения, чтобы достигать частотного разнесения, которое обеспечивает лучшую эффективность перемежения без необходимости в явном перемежении символов.

Фиг. 1А изображает закодированные турбокодом биты 102, вводимые в блок 104 перемежения битов. Блок 104 перемежения битов выводит подвергнутые перемежению биты, которые вводятся в блок 106 отображения символов совокупности. Блок 106 отображения символов совокупности выводит отображаемые биты символов совокупности, которые вводятся в блок 108 перемежения символов совокупности. Блок 108 перемежения символов совокупности выводит подвергнутые перемежению биты символов совокупности в блок 110 формирования каналов. Блок 110 формирования каналов чередует подвергнутые перемежению биты символов совокупности, используя таблицу 112 чередований, и выводит символы 114 OFDM.

Фиг. 1В показывает закодированные турбокодом биты 152, вводимые в блок 154 перемежения битов. Блок 154 перемежения битов выводит подвергнутые перемежению биты, которые вводятся в блок 156 отображения символов совокупности. Блок 15 отображения символов совокупности выводит отображаемые биты символов совокупности, которые вводятся в блок 158 формирования каналов. Блок 158 формирования каналов разделяет на отдельные каналы подвергнутые перемежению биты символов совокупности, используя блок 160 таблицы перемежаемых чередований и динамического отображения чередования отрезков времени, и выводит символы 162 OFDM.

Перемежение битов для разнесения модуляции

Устройство перемежения фиг. 1В использует перемежение 154 битов для достижения разнесения модуляции. Биты 152 кода из пакета быстрого режима перемежаются в такой кодовой комбинации, что смежные биты кода отображаются в символы разных совокупностей. Например, для 2m-ичной модуляции буфер устройства перемежения N битов разделен на N/m блоков. Смежные биты кода последовательно записываются в смежные блоки, а затем считываются один за другим с начала буфера до конца в последовательном порядке, как показано на фиг. 2А (сверху). Это гарантирует, что смежные биты кода будут отображаться в символы разных совокупностей. Эквивалентно этому, как иллюстрируется на фиг. 2В (снизу), буфер устройства перемежения выполнен в виде матрицы из N/m строк на m столбцов. Биты кода записываются в буфер столбец за столбцом и считываются строка за строкой. Чтобы избегать отображения смежного бита кода в такую же позицию бита символа совокупности вследствие того, что некоторые биты символа совокупности более достоверны, чем другие, для 16-КАМ (квадратурной амплитудной модуляции с 16 значащими позициями амплитуды и фазы), где в зависимости от отображения, например, первый и третий биты являются более достоверными, чем второй и четвертый биты, строки должны считываться попеременно слева направо и справа налево.

Фиг. 2А показывает биты кода пакета 202 быстрого режима, помещаемые в буфер 204 перемежения в соответствии с вариантом осуществления. Фиг. 2В представляет иллюстрацию операции перемежения битов в соответствии с вариантом осуществления. Биты кода пакета 250 быстрого режима помещаются в буфер 252 перемежения, как показано на фиг. 2В. Буфер 252 перемежения преобразуется посредством перестановки второго и третьего столбцов, таким образом создавая буфер 254 перемежения, в котором m=4, в соответствии с вариантом осуществления. Подвергнутые перемежению биты кода пакета 256 быстрого режима считываются из буфера 254 перемежения.

Для простоты, можно использовать фиксированное значение m = 4, если самый высокий уровень модуляции составляет 16 и если длина бита кода всегда делится на 4. В этом случае, чтобы улучшить разделение для QPSK (квадратурной фазовой манипуляции), средние два столбца перед считыванием перестанавливаются. Эта процедура изображена на фиг. 2В (снизу). Специалистам в данной области техники должно быть очевидно, что можно переставлять любые два столбца. Специалистам в данной области техники также должно быть очевидно, что столбцы можно помещать в любом порядке. Специалистам в данной области техники также должно быть очевидно, что строки можно помещать в любом порядке.

В другом варианте осуществления, в качестве первого этапа биты кода пакета 202 быстрого режима распределяются в группы. Следует отметить, что варианты осуществления и фиг. 2А, и фиг. 2В также распределяют биты кода в группы. Однако, биты кода внутри каждой группы скорее перетасовываются в соответствии с порядком битов группы для каждой данной группы, чем просто выполняется перестановка строк или столбцов. Таким образом, порядок четырех групп из 16 битов после распределения в группы может быть следующим {1, 5, 9, 13} {2, 6, 10, 14} {3, 7, 11, 15} {4, 8, 12, 16} при использовании простого линейного упорядочивания групп, а порядок четырех групп 16 битов кода после перетасовки может быть следующим {13, 9, 5, 1} {2, 10, 6, 14} {11, 7, 15, 3} {12, 8, 4, 16}. Следует отметить, что перестановка строк или столбцов может быть регрессивным случаем этой перетасовки внутри группы.

Перемежаемое чередование для частотного разнесения

В соответствии с вариантом осуществления, устройство перемежения каналов использует перемежаемое чередование для перемежения символов совокупности, чтобы достигать частотного разнесения. Это устраняет необходимость в явном перемежении символов совокупности. Перемежение выполняется на двух уровнях:

В пределах или внутри перемежаемого чередования: в варианте осуществления, 500 поднесущих чередований перемежаются способом реверсирования битов.

Между или среди перемежаемых чередований: в варианте осуществления, восемь чередований перемежаются способом реверсирования битов.

Специалистам в данной области техники должно быть очевидно, что количество поднесущих может отличаться от 500. Специалистам в данной области техники также должно быть очевидно, что количество чередований может отличаться от восьми.

Следует отметить, что поскольку 500 не является степенью 2, в соответствии с вариантом осуществления должна использоваться операция реверсирования битов сокращенного набора. Следующий код показывает эту операцию:

vector<int>reducedSetBitRev(int n)

{

int m=exponent(n);

vector<int>y(n);

for(int i=0,j=0;i<n;i++,j++)

{

int k;

for(;(k=bitRev(j,m))>=n;j++);

y[i]=k;

}

return y;

}

где n=500, m - самое маленькое целое число, такое, что 2m > n, которое составляет 8, а bitRev является регулярной операцией реверсирования битов.

Символы последовательности символов совокупности канала передачи данных отображаются в соответствующие поднесущие последовательным линейным способом в соответствии с назначенным индексом отрезка времени, определяемым устройством формирования каналов с использованием таблицы чередований, как изображено на фиг. 3, согласно варианту осуществления.

Фиг. 3 иллюстрирует таблицу перемежаемых чередований в соответствии с вариантом осуществления. На ней показаны пакет 302 быстрого режима, символы 304 совокупности и таблица 306 перемежаемых чередований. Также показаны чередование 3 (308), чередование 4 (310), чередование 2 (312), чередование 6 (314), чередование 1 (316), чередование 5 (318), чередование 3 (320) и чередование 7 (322).

В варианте осуществления, одно из этих восьми чередований используется для контрольного сигнала, то есть для контрольного сигнала попеременно используются чередование 2 и чередование 6. В результате, устройство формирования каналов может использовать семь чередований для планирования. Для удобства устройство формирования каналов использует Отрезок времени в качестве единицы планирования. Отрезок времени определяется, как одно чередование символа OFDМ. Таблица чередований используется для отображения отрезка времени в конкретное чередование. Поскольку используются восемь чередований, поэтому имеется восемь отрезков времени. Семь отрезков времени будут отложены для использования для формирования каналов, а один отрезок времени - для контрольного сигнала. Без потери общности, отрезок времени 0 используется для контрольного сигнала, а отрезки времени с 1 по 7 используются для формирования каналов, как показано на фиг. 4, где вертикальная ось представляет индекс 402 отрезка времени, горизонтальная ось - индекс 404 символа OFDM, а начерченный полужирно объект - индекс чередования, назначенный для соответствующего отрезка времени в момент времени символа OFDM.

Фиг. 4 показывает схематическое изображение формирования каналов в соответствии с вариантом осуществления. Фиг. 4 показывает индексы отрезков времени, зарезервированные для планировщика 406, и индексы отрезков времени, зарезервированные для контрольного сигнала 408. Начерченные полужирно объекты представляют собой номера индексов чередования. Номер с квадратом является чередованием, смежным с контрольным сигналом, и следовательно, с хорошей оценкой канала.

Номер, окруженный квадратом, является чередованием, смежным с контрольным сигналом, и следовательно, с хорошей оценкой канала. Поскольку планировщик всегда назначает участок непрерывных отрезков времени и символов OFDM для канала передачи данных, ясно, что из-за перемежения между чередованиями непрерывные отрезки времени, которые назначены для канала передачи данных, будут отображены в прерывистые чередования. Тогда может быть достигнут больший коэффициент усиления при частотном разнесении.

Однако это статическое назначение (то есть отрезок времени для таблицы 1 отображения физического чередования через какое-то время не изменяется) содержит одну проблему. То есть, если блок назначения канала передачи данных (предположим, прямоугольный) занимает множество символов OFDM, чередования, назначенные для канала передачи данных, не изменяются через какое-то время, приводя к потере частотного разнесения. Средство для устранения этого заключается в том, чтобы просто циклически сдвигать таблицу чередований планировщика (то есть, исключая чередование контрольного сигнала) от символа OFDM к символу OFDM.

Фиг. 5 изображает операцию смещения таблицы чередований планировщика по одному разу на символ OFDM. Эта схема успешно устраняет проблему статического назначения чередования, то есть конкретный отрезок времени отображается в различные чередования в разное время символов OFDM.

Фиг. 5 показывает схематическое изображение формирования каналов с последовательностью смещения всех единиц, приводящей к продолжительным периодам оценок хороших и плохих каналов для конкретного отрезка времени 502, в соответствии с вариантом осуществления. Фиг. 5 показывает индексы отрезков времени, зарезервированные для планировщика 506, и индекс отрезка времени, зарезервированный для контрольного сигнала 508. Индекс 504 символов отрезков времени показан на горизонтальной оси.

Однако следует отметить, что отрезки времени назначаются четырем непрерывным чередованиям с оценками хороших каналов, сопровождаемыми продолжительными периодами чередований с оценками плохих каналов, в отличие от предпочтительных кодовых комбинаций коротких периодов выполнения чередований оценок хороших каналов и коротких периодов выполнения чередований с оценками плохих каналов. На чертеже чередование, которое является смежным с чередованием контрольного сигнала, отмечено квадратом. Решение для продолжительных периодов оценок хороших и плохих каналов имеет проблему, которая состоит в том, чтобы использовать последовательность смещения, иную чем последовательность всех единиц. Существует много последовательностей, которые можно использовать для выполнения этой задачи. Самая простая последовательность состоит из последовательности всех двоек, то есть таблица чередований планировщика сдвигается дважды вместо одного раза на символ OFDM. Результат показан на фиг. 6, который значительно улучшает кодовую комбинацию чередования устройства формирования каналов. Следует отметить, что эта кодовая комбинация повторяется каждые 2×7=14 символов OFDM, где 2 - период расположения в шахматном порядке чередований контрольного сигнала, а 7 - период смещения чередований устройства формирования каналов.

Чтобы упростить операцию и в передатчиках, и в приемниках, можно использовать простую формулу для определения отображения из отрезка времени в чередование в данный момент времени символа OFDM.

1Таблица отрезков времени планировщика не включает в себя отрезок времени контрольного сигнала.

i= {(N-((R × t)%N)+s-1)%N},

где

N=I-1 - количество чередований, используемых для планирования данных информационного обмена, где I - общее количество чередований;

i ∈ {0,1,…,I-1}, исключая чередование контрольного сигнала, является индексом чередования, в который отрезок времени s отображается в символ t OFDM;

t=0,1,…,T-1 - индекс символа OFDM в суперкадре, где T - общее количество символов OFDM в кадре 2;

s=1,2,…,S-1, s - индекс отрезка времени, где S - общее количество отрезков времени;

R - количество сдвигов на символ OFDM;

- оператор реверсирования битов сокращенного набора. То есть чередование, используемое контрольным сигналом, должно быть исключено из операции реверсирования битов.

2Индекс символа OFDM в суперкадре вместо кадра дает дополнительное разнесение для кадров, поскольку количество символов OFDM в кадре в современной конструкции не делится на 14.

Пример. В варианте осуществления, I=8, R=2. Соответствующая формула отображения отрезков времени в чередования принимает вид

i= {(7-((2×t)%7)+s-1)%7},

где соответствует следующей таблице:

x ⇒ {х}

0⇒0

1⇒4

2⇒2 или 6

3⇒1

4⇒5

5⇒3

6⇒7

Эта таблица может генерироваться с помощью следующего кода:

int reducedSetBitRev(int x, int exclude, int n)

{

int m=exponent(n);

int у;

for(int i=0, j=0; i<=x; i++, j++)

{

for (; (y=bitRev(j, m))=exclude; j++);

}

return y;

}

где m=3, а bitRev - операция регулярного реверсирования битов.

Для символа OFDM t=11, контрольный сигнал использует чередование 6. Отображение между отрезком времени и чередованием становится следующим:

Отрезок времени 1 отображается в чередование {(7-(2×11)%7+1-1)%7}={6}=7;

Отрезок времени 2 отображается в чередование {(7-(2×11)%7+2-1)%7}={0}=0;

Отрезок времени 3 отображается в чередование {(7-(2×11)%7+3-1)%7}={1}=4;

Отрезок времени 4 отображается в чередование {(7-(2×11)%7+4-1)%7}={2}=2;

Отрезок времени 5 отображается в чередование {(7-(2×11)%7+5-1)%7}={3}=1;

Отрезок времени 6 отображается в чередование {(7-(2×11)%7+6-1)%7}={4}=5;

Отрезок времени 7 отображается в чередование {(7-(2×11)%7+7-1)%7}={5}=3.

Полученное в результате отображение согласуется с отображением на фиг. 6. Фиг. 6 показывает схематическое изображение формирования каналов с последовательностью смещения всех двоек, приводящей к равномерному распространению чередований оценок хороших и плохих каналов.

В соответствии с вариантом осуществления, устройство перемежения имеет следующие признаки:

устройство перемежения битов предназначено для получения преимуществ от разнесения m-ичной модуляции посредством перемежения битов кода в различные символы модуляции;

"перемежение символов" предназначено для достижения частотного разнесения посредством перемежения внутри чередований и перемежения между чередованиями;

дополнительный коэффициент усиления при частотном разнесении и коэффициент усиления при оценке канала достигнуты посредством изменения таблицы отображения отрезков времени в чередования от символа OFDM к символу OFDM. Для достижения этой цели предложена простая последовательность циклических сдвигов.

Фиг. 7 показывает беспроводное устройство, выполненное с возможностью реализации перемежения в соответствии с вариантом осуществления. Беспроводное устройство 702 содержит антенну 704, антенный переключатель D 706, приемник 708, передатчик 710, процессор 712 и запоминающее устройство 714. Процессор 712 способен выполнять перемежение в соответствии с вариантом осуществления. Процессор 712 использует запоминающее устройство 714 для буферов или структур данных, чтобы выполнять свои операции.

Специалистам в данной области техники должно быть понятно, что информация и сигналы могут быть представлены с использованием любого из ряда различных технических приемов и методов. Например, данные, инструкции, команды, информация, сигналы, биты, символы и кодовые элементы, которые могут упоминаться на протяжении всего приведенного выше описания, могут быть представлены напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами, или любой их комбинацией.

Специалисты в данной области техники дополнительно могут оценить, что различные иллюстративные логические блоки, модули, схемы и этапы алгоритмов, описанные в связи с раскрытыми в данном описании вариантами осуществления, могут быть реализованы в виде электронных аппаратных средств, программного обеспечения или их комбинации. Чтобы ясно проиллюстрировать эту взаимозаменяемость аппаратных средств и программного обеспечения, различные иллюстративные компоненты, блоки, модули, схемы и этапы были описаны выше в общем в терминах их функциональных возможностей. Реализованы ли такие функциональные возможности, как аппаратные средства или программное обеспечение, зависит от конкретного применения и конструктивных ограничений, накладываемых на всю систему. Специалисты в данной области техники могут реализовывать описанные функциональные возможности отличающимися способами для каждого конкретного применения, но такие решения выполнения не должны интерпретироваться, как приводящие к отклонению от объема настоящего изобретения.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми в данном описании вариантами осуществления, могут быть реализованы или выполнены с помощью универсального процессора, цифрового процессора сигналов (DSP), интегральной схемы прикладной ориентации (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства, дискретного логического элемента или транзисторного логического устройства, дискретных аппаратных компонентов или любой их комбинации, предназначенной для выполнения описанных в данном описании функций. Универсальный процессор может быть микропроцессором, но в качестве альтернативы, процессор может быть любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован в виде комбинации вычислительных устройств, например комбинации DSP и микропроцессора, множества микропроцессоров, одного или больше микропроцессоров вместе с ядром DSP, или любой другой такой конфигурации.

Этапы способа или алгоритма, описанные в связи с раскрытыми в данном описании вариантами осуществления, могут быть воплощены непосредственно в аппаратных средствах, в программном модуле, выполняемом процессором, или в их комбинации. Программный модуль может постоянно находиться в памяти ОЗУ (оперативное запоминающее устройство), флэш-памяти, памяти ПЗУ (постоянное запоминающее устройство), памяти ППЗУ (программируемое ПЗУ), памяти ЭСППЗУ (электрически стираемое ППЗУ), регистрах, жестком диске, съемном диске, CD-ROM (неперезаписываемый компакт-диск) или любой другой форме носителя данных, известной в технике. Примерный носитель данных соединен с процессором таким образом, что процессор может считывать информацию с носителя данных и записывать на него информацию. В качестве альтернативы, носитель данных может быть встроен в процессор. Процессор и носитель данных могут постоянно находиться в ASIC. ASIC может постоянно находиться в пользовательском терминале. В качестве альтернативы, процессор и носитель данных могут постоянно находиться в виде дискретных компонентов в пользовательском терминале.

Предыдущее описание раскрытых вариантов осуществления представлено для того, чтобы дать возможность любому специалисту в данной области техники выполнять или использовать настоящее изобретение. Различные модификации к этим вариантам осуществления специалистам в данной области техники будут очевидны, а универсальные принципы, определенные в данном описании, могут применяться к другим вариантам осуществления, не выходя при этом за рамки сущности и объема изобретения. Таким образом, настоящее изобретение не должно быть ограничено вариантами осуществления, показанными в данном описании, но должно соответствовать самому широкому объему, совместимому с принципами и новыми признаками, раскрытыми в данном описании.

1. Способ перемежения чередований для достижения частотного разнесения в системе беспроводной связи, содержащий:перемежение битов символов в поднесущих чередований способом реверсирования битов устройством перемежения битов, иперемежение чередований способом реверсирования битов устройством перемежения символов, причем чередования содержат поднесущие, содержащие символы, подвергнутые перемежению битов по предыдущему этапу,при этом способ реверсирования битов является операцией реверсирования битов сокращенного набора, если количество поднесущих не является степенью двух.

2. Способ по п.1, в котором количество поднесущих равно 500.

3. Способ по п.2, в котором количество чередований равно восьми.

4. Способ по п.1, в котором этап перемежения чередований способом реверсирования битов включает в себя отображение символов из последовательности символов совокупности в соответствующие поднесущие последовательным линейным способом в соответствии с назначенным индексом отрезка времени с использованием таблицы чередований.

5. Процессор для выполнения перемежения в системе беспроводной связи, выполненный с обеспечением возможностиперемежения битов символов в поднесущих чередований способом реверсирования битов, иперемежения чередований способом реверсирования битов, причем чередования содержат поднесущие, содержащие символы, подвергнутые упомянутому перемежению битов,при этом способ реверсирования битов является операцией реверсирования битов сокращенного набора, если количество поднесущих не является степенью двух.

6. Процессор для выполнения перемежения в системе беспроводной связи, содержащийустройство для перемежения битов для перемежения битов символов в поднесущих чередований способом реверсирования битов, иустройство для перемежения символов для перемежения чередований способом реверсирования битов, причем чередования содержат поднесущие, содержащие символы, подвергнутые упомянутому перемежению битов с помощью устройства для перемежения битов,при этом способ реверсирования битов является операцией реверсирования битов сокращенного набора, если количество поднесущих не является степенью двух.

7. Машиночитаемый носитель информации, содержащий сохраненные на нем инструкции, которые, при считывании процессором, побуждают процессор к воплощению способа перемежения, содержащего:перемежение битов символов в поднесущих чередований способом реверсирования битов, иперемежение чередований способом реверсирования битов,причем чередования содержат поднесущие, содержащие символы, подвергнутые перемежению битов по предыдущему этапу,при этом способ реверсирования битов является операцией реверсирования битов сокращенного набора, если количество поднесущих не является степенью двух.