Комплементарный двухтактный каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для усиления аналоговых сигналов. Технический результат - повышение коэффициента ослабления входных синфазных сигналов за счет автоматического установления статического режима без классических источников опорного тока. Устройство содержит первый (1) и второй (2) входные р-n-р транзисторы (Т) с объединенными базами, эмиттеры которых через соответствующие первый (3) и второй (4) токостабилизирующие двухполюсники (ТД) связаны с шиной (5) положительного источника питания (ИП), первый (8) и второй (9) входные n-р-n Т с объединенными базами, эмиттеры которых через соответствующие третий (10) и четвертый (11) ТД связаны с шиной (12) отрицательного ИП, первый (15) выходной р-n-р Т, эмиттер которого связан с шиной (5) ИП через пятый (16) ТД, а база подключена к коллекторам Т (2) и Т (9), второй (17) выходной n-р-n Т, эмиттер которого связан с шиной (12) ИП через шестой (18) ТД, а база соединена с базой Т (15), третий (19) выходной n-р-n Т, база которого соединена с эмиттером Т (15), четвертый (20) выходной р-n-р Т, база которого соединена с эмиттером Т (17), а эмиттер подключен к эмиттеру Т (19) и выходу (21) КДУ. В схему введены первый (23) n-р-n и второй (24) р-n-р дополнительные Т, эмиттер Т (23) соединен с коллектором Т (1), коллектор Т (23) соединен с базами Т (1) и Т (2), а база Т (23) подключена к эмиттеру Т (15), эмиттер Т (24) соединен с коллектором Т (8), коллектор Т (24) связан с объединенными базами Т (8) и Т (9), база Т (24) соединена с эмиттером Т (17), причем седьмой ТД (22) выполнен в виде резистора, который включен между эмиттерами Т (23) и Т (24). 1 з.п. ф-лы, 14 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage» или «комплементарных дифференциальных усилителей (КДУ)») [1-20]. По такой архитектуре, на модификации которой выдано около 50 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Однако в практических схемах известных КДУ коэффициент ослабления входного синфазного сигнала (Кос.сф) получается небольшим (50÷60 ДБ). Это связано с асимметрией архитектуры КДУ.

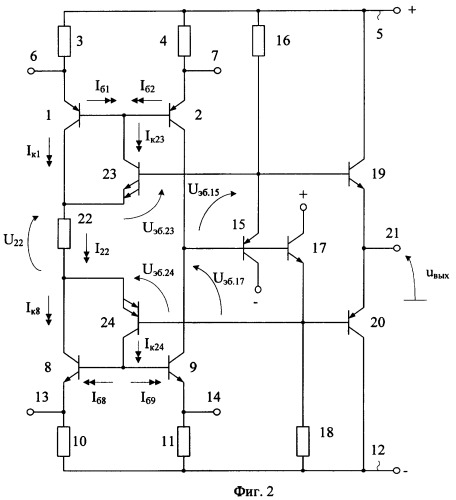

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патентной заявке США №2005/0127999, содержащий первый 1 и второй 2 входные p-n-p транзисторы с объединенными базами, эмиттеры которых через соответствующие первый 3 и второй 4 токостабилизирующие двухполюсники связаны с шиной 5 положительного источника питания и первым 6 и вторым 7 входами комплементарного двухтактного каскодного дифференциального усилителя, первый 8 и второй 9 входные p-n-p транзисторы с объединенными базами, эмиттеры которых через соответствующие третий 10 и четвертый 11 токостабилизирующие двухполюсники связаны с шиной 12 отрицательного источника питания и третьим 13, и четвертым 14 входами комплементарного каскодного дифференциального усилителя, первый 15 выходной p-n-p транзистор, эмиттер которого связан с шиной 5 положительного источника питания через пятый 16 токостабилизирующий двухполюсник, а база подключена к коллекторам второго p-n-p (2) и второго n-p-n (9) входных транзисторов, второй выходной n-p-n транзистор 17, эмиттер которого связан с шиной 12 отрицательного источника питания через шестой токостабилизирующий двухполюсник 18, а база соединена с базой первого 15 выходного p-n-p транзистора, третий выходной n-p-n транзистор 19, база которого соединена с эмиттером первого 15 выходного p-n-p транзистора, четвертый 20 выходной p-n-p транзистор, база которого соединена с эмиттером второго 17 выходного n-p-n транзистора, а эмиттер подключен к эмиттеру третьего 19 выходного n-p-n транзистора и выходу 21 комплементарного двухтактного каскодного дифференциального усилителя, седьмой 22 токостабилизирующий двухполюсник.

Существенный недостаток известного КДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов, которое определяется коэффициентом

где Ку>>1 - коэффициент усиления входного дифференциального сигнала КДУ;

Ксф.<<1 - коэффициент передачи входного синфазного сигнала КДУ.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов.

Поставленная цель достигается тем, что в дифференциальном усилителе (фиг.1), содержащем первый 1 и второй 2 входные p-n-p транзисторы с объединенными базами, эмиттеры которых через соответствующие первый 3 и второй 4 токостабилизирующие двухполюсники связаны с шиной 5 положительного источника питания и первым 6 и вторым 7 входами комплементарного двухтактного каскодного дифференциального усилителя, первый 8 и второй 9 входные n-р-n транзисторы с объединенными базами, эмиттеры которых через соответствующие третий 10 и четвертый 11 токостабилизирующие двухполюсники связаны с шиной 12 отрицательного источника питания и третьим 13, и четвертым 14 входами комплементарного каскодного дифференциального усилителя, первый 15 выходной p-n-p транзистор, эмиттер которого связан с шиной 5 положительного источника питания через пятый 16 токостабилизирующий двухполюсник, а база подключена к коллекторам второго p-n-p (2) и второго p-n-p (4) входных транзисторов, второй выходной n-p-n транзистор 17, эмиттер которого связан с шиной 12 отрицательного источника питания через шестой токостабилизирующий двухполюсник 18, а база соединена с базой первого 15 выходного p-n-p транзистора, третий выходной n-p-n транзистор 19, база которого соединена с эмиттером первого 15 выходного p-n-p транзистора, четвертый 20 выходной p-n-p транзистор, база которого соединена с эмиттером второго 17 выходного n-p-n транзистора, а эмиттер подключен к эмиттеру третьего 19 выходного n-p-n транзистора и выходу 21 комплементарного двухтактного каскодного дифференциального усилителя, седьмой 22 токостабилизирующий двухполюсник, предусмотрены новые связи - в схему введены первый 23 n-p-n и второй 24 p-n-p дополнительные транзисторы, эмиттер первого n-p-n 23 дополнительного транзистора соединен с коллектором первого 1 входного p-n-p транзистора, коллектор первого n-p-n 23 дополнительного транзистора соединен с базами первого 1 и второго 2 входных p-n-p транзисторов, а база первого 23 n-p-n дополнительного транзистора подключена к эмиттеру первого 15 n-p-n выходного транзистора, эмиттер второго 24 p-n-p дополнительного транзистора соединен с коллектором второго 8 входного p-n-p транзистора, коллектор второго 24 p-n-p дополнительного транзистора связан с объединенными базами первого 8 и второго 9 входных p-n-p транзисторов, база второго 24 p-n-p дополнительного транзистора соединена с эмиттером второго 17 n-p-n выходного транзистора, причем седьмой токостабилизирующий двухполюсник 22 выполнен в виде резистора, который включен между эмиттерами первого n-p-n 23 и второго 24 p-n-p дополнительных транзисторов.

Схема заявляемого устройства в соответствии с формулой изобретения показана на фиг.2.

На фиг.3 показана схема входного каскада на основе двух параллельно включенных дифференциальных каскадов с источниками опорного тока в эмиттерных цепях входных транзисторов.

На фиг.4 представлена схемотехническая реализация симметричного входного каскада по мостовой схеме.

На фиг.5 показана схема операционного усилителя на основе комплементарного каскодного дифференциального усилителя (фиг.2) с входным каскадом на основе двух параллельно включенных дифференциальных каскадов с источниками опорного тока в эмиттерных цепях входных транзисторов (фиг.3).

На фиг.6 представлена частотная зависимость коэффициента усиления схемы (фиг.5).

На фиг.7 показана схема операционного усилителя на основе комплементарного каскодного дифференциального усилителя (фиг.2) с входным каскадом на основе двух параллельно включенных дифференциальных каскадов с резисторами в эмиттерных цепях входных транзисторов.

На фиг.8 представлена частотная зависимость коэффициента усиления схемы (фиг.7)

На фиг.9 показана схема операционного усилителя на основе комплементарного каскодного дифференциального усилителя (фиг.2) с входным каскадом на основе двух параллельно включенных дифференциальных каскадов с источниками опорного тока в эмиттерных цепях входных транзисторов (фиг.3), выходные сопротивления которых неравны (15 кОм, 30 кОм).

На фиг.10 представлена зависимость коэффициента ослабления синфазного сигнала от частоты для схемы фиг.9.

На фиг.11 показана схема операционного усилителя на основе комплементарного каскодного дифференциального усилителя (фиг.2) с входным каскадом на основе двух параллельно включенных дифференциальных каскадов с источниками опорного тока в эмиттерных цепях входных транзисторов (фиг.3), выходные сопротивления которых равны.

На фиг.12 представлена зависимость коэффициента ослабления синфазного сигнала от частоты для схемы фиг.11.

Фиг.6, фиг.8, фиг.10, фиг.12 получены в результате компьютерного моделирования, комплементарных двухтактных каскодных дифференциальных усилителей фиг.5, фиг.7, фиг.9, фиг.11, соответственно, в среде PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные p-n-p транзисторы с объединенными базами, эмиттеры которых через соответствующие первый 3 и второй 4 токостабилизирующие двухполюсники связаны с шиной 5 положительного источника питания и первым 6 и вторым 7 входами комплементарного двухтактного каскодного дифференциального усилителя, первый 8 и второй 9 входные n-p-n транзисторы с объединенными базами, эмиттеры которых через соответствующие третий 10 и четвертый 11 токостабилизирующие двухполюсники связаны с шиной 12 отрицательного источника питания и третьим 13 и четвертым 14 входами комплементарного каскодного дифференциального усилителя, первый 15 выходной p-n-p транзистор, эмиттер которого связан с шиной 5 положительного источника питания через пятый 16 токостабилизирующий двухполюсник, а база подключена к коллекторам второго p-n-p (2) и второго n-p-n (9) входных транзисторов, второй выходной n-p-n транзистор 17, эмиттер которого связан с шиной 12 отрицательного источника питания через шестой токостабилизирующий двухполюсник 18, а база соединена с базой первого 15 выходного p-n-p транзистора, третий выходной n-p-n транзистор 19, база которого соединена с эмиттером первого 15 выходного p-n-p транзистора, четвертый 20 выходной p-n-p транзистор, база которого соединена с эмиттером второго 17 выходного n-p-n транзистора, а эмиттер подключен к эмиттеру третьего 19 выходного n-p-n транзистора и выходу 21 комплементарного двухтактного каскодного дифференциального усилителя, седьмой 22 токостабилизирующий двухполюсник. В схему введены первый 23 n-p-n и второй 24 p-n-p дополнительные транзисторы, эмиттер первого n-p-n 23 дополнительного транзистора соединен с коллектором первого 1 входного p-n-p транзистора, коллектор первого p-n-p 23 дополнительного транзистора соединен с базами первого 1 и второго 2 входных p-n-p транзисторов, а база первого 23 n-p-n дополнительного транзистора подключена к эмиттеру первого 15 p-n-p выходного транзистора, эмиттер второго 24 p-n-p дополнительного транзистора соединен с коллектором первого 8 входного n-p-n транзистора, коллектор второго 24 p-n-p дополнительного транзистора связан с объединенными базами первого 8 и второго 9 входных n-p-n транзисторов, база второго 24 p-n-p дополнительного транзистора соединена с эмиттером второго 17 n-p-n выходного транзистора, причем седьмой токостабилизирующий двухполюсник 22 выполнен в виде резистора, который включен между эмиттерами первого n-p-n 23 и второго 24 p-n-p дополнительных транзисторов.

На чертеже фиг.2, в соответствии с п.2 формулы изобретения, первый 6 и второй 7, а также третий 8 и четвертый 14 входы комплементарного двухтактного каскодного дифференциального усилителя соединены с выходами комплементарного параллельно-балансного дифференциального каскада, например, фиг.3 (фиг.4).

Рассмотрим работу схемы фиг.2.

Статический режим входных p-n-p (1, 2) и входных p-n-p (8, 9) транзисторов устанавливается двухполюсниками 16 и 18 (это могут быть резисторы) и токостабилизирующим двухполюсником 22. На основании второго закона Кирхгофа можно записать, что напряжение на сравнительно низкоомном двухполюснике (резисторе) 22:

Если вольтамперные характеристики всех транзисторов аппроксимировать традиционной экспонентой

а также учесть, что ток коллектора транзистора 23 (24) в β - раз меньше, чем ток коллектора транзисторов 1, 2, 8 и 9, то уравнение (1) можно представить в следующем виде

В последних уравнениях:

φТ=26 мВ - температурный потенциал; Iэ0 - ток обратно-смещенных эмиттерных р-n переходов транзисторов 1, 2, 8, 9; I0=I16=I17.

Численные значения сопротивления двухполюсника 22 (R22) для практических схем заявляемого КДУ лежат в диапазоне десятков-сотен Ом. Для некоторого увеличения R22 авторы рекомендуют применить в качестве элементов 23 и 24 несколько параллельно включенных транзисторов. В качестве двухполюсников 16 и 18 могут использоваться резисторы. В этом случае в уравнении (3) следует считать, что

где Е5 - напряжение на шине 5 положительного источника питания;

E12 - напряжение на шине 12 отрицательного источника питания.

Таким образом, заявляемая схема обеспечивает «самоустановление» статического режима - без классических источников опорного тока (фиг.1). При этом ввиду ее высокой симметрии существенно улучшается Кос.сф (фиг.10, фиг.12, фиг.14). Введение цепей «слежения» статического режима транзисторов (по Uкб) за уровнем выходного напряжения КДУ существенно повышает и другой параметр КДУ - коэффициент усиления по напряжению Ку (фиг.6, фиг.8).

Источники информации

1. Патент РФ №2193273, H03F 3/45.

2. Патент Японии №53-25232, H03F 3/26, 98(5) А332.

3. Патент US 2001/0052818A1, H03F, 3/45.

4. Патент Японии №JР8222972.

5. Авт. Свид. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - стр.103. Рис.6.11.

7. Патент США №6.366.170 B1H03F/45.

8. Патент США №6.268.769 H03F/45.

9. Патент США №3.974.455 H03F/45.

10. Патент США №3.968.451 H03F/45.

11. Патент США №4.837.523 H03F/45.

12. Патент США №5.291.149 H03F/45.

13. Патент США №4.636.743 H03F/45.

14. Патент США №4.783.637 H03F/45.

15. Патент США №5.515.005 H03F/45.

16. Патент США №5.291.149 H03F/45.

17. Патент США №5.140.280 H03F/45.

18. Патент США №5.455.535 H03F/45.

19. Патент США №5.523.718 H03F/45.

20. Патент США №4.600.893 H03F/45.

21. Дворников О.В. Схемотехника биполярно-полевых аналоговых микросхем. Chip News, #10 (93), 2004, стр.41.

1. Комплементарный двухтактный каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные p-n-p транзисторы с объединенными базами, эмиттеры которых через соответствующие первый (3) и второй (4) токостабилизирующие двухполюсники связаны с шиной (5) положительного источника питания и первым (6) и вторым (7) входами комплементарного двухтактного каскодного дифференциального усилителя, первый (8) и второй (9) входные n-р-n транзисторы с объединенными базами, эмиттеры которых через соответствующие третий (10) и четвертый (11) токостабилизирующие двухполюсники связаны с шиной (12) отрицательного источника питания и третьим (13) и четвертым (14) входами комплементарного каскодного дифференциального усилителя, первый (15) выходной p-n-p транзистор, эмиттер которого связан с шиной (5) положительного источника питания через пятый (16) токостабилизирующий двухполюсник, а база подключена к коллекторам второго p-n-p (2) и второго n-р-n (9) входных транзисторов, второй выходной n-р-n транзистор (17), эмиттер которого связан с шиной (12) отрицательного источника питания через шестой токостабилизирующий двухполюсник (18), а база соединена с базой первого (15) выходного p-n-p транзистора, третий выходной n-р-n транзистор (19), база которого соединена с эмиттером первого (15) выходного p-n-p транзистора, четвертый (20) выходной p-n-p транзистор, база которого соединена с эмиттером второго (17) выходного n-p-n транзистора, а эмиттер подключен к эмиттеру третьего (19) выходного n-p-n транзистора и выходу (21) комплементарного двухтактного каскодного дифференциального усилителя, седьмой (22) токостабилизирующий двухполюсник, отличающийся тем, что в схему введены первый (23) n-p-n и второй (24) p-n-p дополнительные транзисторы, эмиттер первого n-p-n (23) дополнительного транзистора соединен с коллектором первого (1) входного p-n-p транзистора, коллектор первого n-p-n (23) дополнительного транзистора соединен с базами первого (1) и второго (2) входных p-n-p транзисторов, а база первого (23) n-p-n дополнительного транзистора подключена к эмиттеру первого (15) p-n-p выходного транзистора, эмиттер второго (24) р-n-р дополнительного транзистора соединен с коллектором первого (8) входного n-p-n транзистора, коллектор второго (24) p-n-p дополнительного транзистора связан с объединенными базами первого (8) и второго (9) входных n-p-n транзисторов, база второго (24) p-n-p дополнительного транзистора соединена с эмиттером второго (17) n-p-n выходного транзистора, причем седьмой токостабилизирующий двухполюсник (22) выполнен в виде резистора, который включен между эмиттерами первого n-p-n (23) и второго (24) р-n-р дополнительных транзисторов.

2. Устройство по п.1, отличающееся тем, что первый (6) и второй (7), а также третий (13) и четвертый (14) входы комплементарного двухтактного каскодного дифференциального усилителя соединены с выходами комплементарного параллельно-балансного дифференциального каскада.