Мультидифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, инструментальных усилителях, активных фильтрах и т.п.). Технический результат - уменьшение токопотребления и повышение симметрии. Мультидифференциальный усилитель (МДУ) содержит первый (1) и второй (2) входы, согласованные с шиной (3) положительного источника питания (ИП), третий (4) и четвертый (5) входы, согласованные с шиной (6) отрицательного ИП, первый (7) и второй (8) входные транзисторы (Т) с объединенными базами, эмиттеры которых соединены с соответствующими первым (1) и вторым (2) входами, третий (9) и четвертый (10) входные Т с объединенными базами, эмиттеры которых подключены к соответствующим третьему (4) и четвертому (5) входам, причем коллектор второго (8) и четвертого (10) входных Т объединены и соединены с выходной цепью (11) МДУ. В схему введены первый (12) и второй (13) дополнительные Т, базы которых связаны с цепью установления статического потенциала (14), коллектор первого (12) дополнительного Т соединен с объединенными базами первого (7) и второго (8) входных Т, коллектор второго (13) дополнительного Т соединен с объединенными базами третьего (9) и четвертого (10) входных Т, эмиттер первого (12) дополнительного Т подключен к коллектору третьего (9) входного Т и через дополнительный резистор (15) соединен с эмиттером второго (13) дополнительного Т и коллектором первого (7) входного Т. 5 з.п. ф-лы, 17 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, инструментальных усилителях, активных фильтрах и т.п.).

Известны схемы так называемых «перегнутых» мультидифференциальных каскодных дифференциальных усилителей (КДУ) на n-р-n и р-n-р транзисторах, которые стали основой более чем 20 серийных ОУ, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 50 патентов в различных странах. Предлагаемое изобретение относится к данному подклассу устройств.

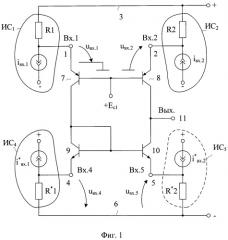

Одной из модификаций «перегнутых» каскодных дифференциальных усилителей является схема фиг.1, представленная в публикациях [1-7]. Она используется в ОУ ряда ведущих микроэлектронных фирм. Особенность таких КДУ - наличие четырех входов.

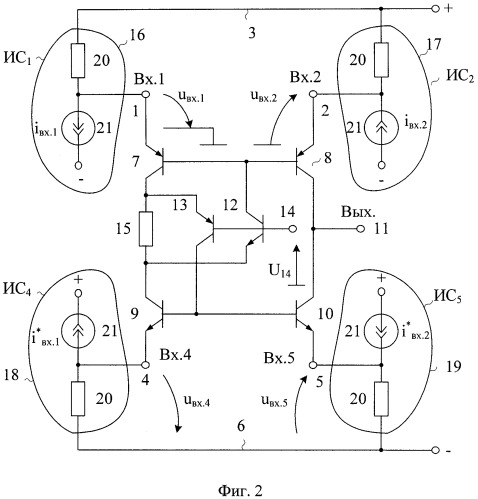

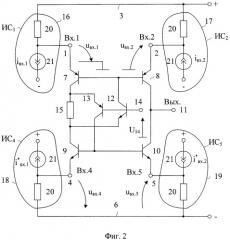

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4.532.479, содержащий первый 1 и второй 2 входы, согласованные с шиной 3 положительного источника питания, третий 4 и четвертый 5 входы, согласованные с шиной 6 отрицательного источника питания, первый 7 и второй 8 входные транзисторы с объединенными базами, эмиттеры которых соединены с соответствующими первым 1 и вторым 2 входами, согласованными с шиной 3 положительного источника питания, третий 9 и четвертый 10 входные транзисторы с объединенными базами, эмиттеры которых подключены к соответствующим третьему 4 и четвертому 5 входам, согласованным с шиной 6 отрицательного источника питания, причем коллектор второго 8 и четвертого 10 входных транзисторов объединены и соединены с выходной цепью 11 мультидифференциального усилителя (МДУ).

Существенный недостаток известного МДУ состоит в том, что его архитектура несимметрична - коэффициенты передачи по входам 1, 2 и 5 отличаются от коэффициента передачи по входу 4. Это оказывает отрицательное влияние на погрешности МДУ, связанные с напряжением смещения нуля (Ucм) и коэффициентом ослабления синфазных сигналов (Кос.сф).

Кроме этого известный МДУ имеет повышенное собственное токопотребление, что связано с наличием в схеме второстепенного источника питания (+Ecl), непосредственно не влияющего на усилительные параметры МДУ (обеспечивающие только статический режим транзисторов 7, 8).

Цель предлагаемого изобретения состоит в уменьшении собственного токопотребления МДУ, а также создании условий для улучшения гаммы параметров МДУ (напряжение смещения, коэффициент ослабления синфазных сигналов, коэффициент подавления помехи по питанию, коэффициент усиления по напряжению), зависящих от степени симметрии его структуры.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входы, согласованные с шиной 3 положительного источника питания, третий 4 и четвертый 5 входы, согласованные с шиной 6 отрицательного источника питания, первый 7 и второй 8 входные транзисторы с объединенными базами, эмиттеры которых соединены с соответствующими первым 1 и вторым 2 входами, согласованными с шиной 3 положительного источника питания, третий 9 и четвертый 10 входные транзисторы с объединенными базами, эмиттеры которых подключены к соответствующим третьему 4 и четвертому 5 входам, согласованным с шиной 6 отрицательного источника питания, причем коллектор второго 8 и четвертого 10 входных транзисторов объединены и соединены с выходной цепью 11 мультидифференциального усилителя, предусмотрены новые элементы и связи - в схему введены первый 12 и второй 13 дополнительные транзисторы, базы которых связаны с цепью установления статического потенциала 14, коллектор первого 12 дополнительного транзистора соединен с объединенными базами первого 7 и второго 8 входных транзисторов, коллектор второго 13 дополнительного транзистора соединен с объединенными базами третьего 9 и четвертого 10 входных транзисторов, эмиттер первого 12 дополнительного транзистора подключен к коллектору третьего 9 входного транзистора и через дополнительный резистор 15 соединен с эмиттером второго 13 дополнительного транзистора и коллектором первого входного транзистора 7.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

На фиг.3, в соответствии с п.2 формулы изобретения, показаны варианты выполнения входных преобразователей ток-напряжение на элементах 20.1÷20.5 и 21.1÷21.5.

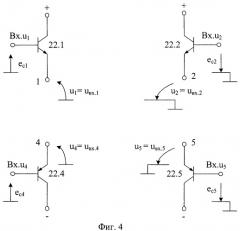

На фиг.4 представлены варианты выполнения входных эмиттерных повторителей на транзисторах 22 (22.1÷22.5) (п.3 формулы изобретения).

На фиг.5 представлена схема заявляемого устройства, соответствующая п.3 и п.4 формулы изобретения, для случая, когда объединенные базы транзисторов 12 и 13 подключены к выходной цепи 11 мультидифференциального усилителя.

На фиг.6 показана схема заявляемого МДУ, в котором в соответствии с п.5 формулы изобретения базы транзисторов 12 и 13 подключены к выходу 23 буферного усилителя 24.

Схема фиг.7 соответствует п.1 формулы изобретения для случая, когда входные преобразователи ток-напряжение реализованы на основе двухполюсников 20.1-20.5. В частном случае к коллекторам транзисторов 8 и 10 могут подключаться выходные транзисторы 25-26.

Схема фиг.8 иллюстрирует конкретное применение МОУ фиг.7 в структуре операционного усилителя на основе комплементарных входных каскадов на транзисторах 27-32 и резисторах 33 и 34, а также выходном каскаде на транзисторах 35-36.

Принципиальная схема фиг.9 поясняет пример построения каскодного усилителя с входным каскадом на транзисторах 37-39 для случая, когда входы 1 и 2 МДУ не используются, а на входы 4, 5 подается токовый сигнал от транзисторов 37, 38 с источником тока на транзисторе 39.

На схеме фиг.10 представлен дифференциальный усилитель с низкоомными входами 1 и 2 в структуре низковольтного усилителя на базе предлагаемой архитектуры МДУ для случая, когда входы 4 и 5 не используются, а входные сигналы подаются на входы МДУ 1 и 2.

Схема фиг.11 является модификацией схемы фиг.10, в которой на входы 1 и 2 подается сигнал с выходов эмиттерных повторителей на транзисторах 22.1 и 22.2.

Схема фиг.12 соответствует п.6 формулы изобретения. Здесь между базами транзисторов 12 и 13 включен согласующий р-n переход 40, входящий в структуру цепи установления статического потенциала 14.

На фиг.13 представлена схема МДУ фиг.9 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Компьютерный анализ этой схемы подтверждает работоспособность заявляемого устройства (при наличии асимметрии применяемых элементов).

На фиг.14 показана зависимость коэффициента усиления МДУ фиг.13 от частоты.

На фиг.15 в качестве примера построения представлена схема МДУ фиг.9 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» с цепью запуска статического режима (R3, R4, VT1), а на фиг.16 - зависимость коэффициента усиления МДУ фиг.15 от частоты.

На фиг.17 в качестве примера построения представлена схема МДУ фиг.8 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НИИ «Пульсар».

Мультидифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входы, согласованные с шиной 3 положительного источника питания, третий 4 и четвертый 5 входы, согласованные с шиной 6 отрицательного источника питания, первый 7 и второй 8 входные транзисторы с объединенными базами, эмиттеры которых соединены с соответствующими первым 1 и вторым 2 входами, согласованными с шиной 3 положительного источника питания, третий 9 и четвертый 10 входные транзисторы с объединенными базами, эмиттеры которых подключены к соответствующим третьему 4 и четвертому 5 входам, согласованным с шиной 6 отрицательного источника питания, причем коллектор второго 8 и четвертого 10 входных транзисторов объединены и соединены с выходной цепью 11 мультидифференциального усилителя. В схему введены первый 12 и второй 13 дополнительные транзисторы, базы которых связаны с цепью установления статического потенциала 14, коллектор первого 12 дополнительного транзистора соединен с объединенными базами первого 7 и второго 8 входных транзисторов, коллектор второго 13 дополнительного транзистора соединен с объединенными базами третьего 9 и четвертого 10 входных транзисторов, эмиттер первого 12 дополнительного транзистора подключен к коллектору третьего 9 входного транзистора и через дополнительный резистор 15 соединен с эмиттером второго 13 дополнительного транзистора и коллектором первого входного транзистора 7.

На фиг.2, в соответствии с п.2 формулы изобретения (фиг.3), в качестве первого 16, второго 17 и/или третьего 18 и четвертого 19 источников сигналов (ИС), подключенных соответственно к первому 1, второму 2 и/или третьему 4 и четвертому 5 входам мультидифференциального усилителя, используются преобразователи ток-напряжения, реализованные на основе вспомогательных двухполюсников 20 и соединенных с ними управляемых источников входных токов 21 (элементы 20.1÷20.5, 21.1÷21.5).

На фиг.4, в соответствии с п.4 формулы изобретения, в качестве первого 16, второго 17 и/или третьего 18 и четвертого 19 источников сигнала (фиг.2) используются эмиттерные повторители на основе вспомогательных транзисторов 22, причем входные потенциальные сигналы мультидифференциального усилителя подаются на базы вспомогательных транзисторов 22 (22.1÷22.5).

На фиг.5, в соответствии с п.3 п.4 формулы изобретения, в качестве цепи установления статического потенциала 14 используется выходная цепь 11 мультидифференциального усилителя.

На фиг.6, соответствующей п.5 формулы изобретения, в качестве цепи установления статического потенциала 14 используется выход 23 дополнительного буферного усилителя 24, вход которого соединен с выходной цепью 11 мультидифференциального усилителя.

Схема фиг.7 соответствует п.1 формулы изобретения для случая, когда входные преобразователи ток-напряжение реализованы на основе двухполюсников 20.1-20.5. В частном случае к коллекторам транзисторов 8 и 10 могут подключаться выходные транзисторы 25-26.

Схема фиг.8 иллюстрирует конкретное применение МОУ фиг.7 в структуре операционного усилителя на основе комплементарных входных каскадов на транзисторах 27-32 и резисторах 33 и 34, а также выходном каскаде на транзисторах 35-36.

Принципиальная схема фиг.9 иллюстрирует пример построения каскодного усилителя с входным каскадом на транзисторах 37-39 для случая, когда входы 1 и 2 МДУ не используются, а на входы 4, 5 подается токовый сигнал от транзисторов 37, 38 с источником тока на транзисторе 39.

На схеме фиг.10 представлен дифференциальный усилитель с низкоомными входами 1 и 2 в структуре низковольтного усилителя на базе предлагаемой архитектуры МДУ для случая, когда входы 4 и 5 не используются, а входные сигналы подаются на входы МДУ 1 и 2.

Схема фиг.11 является модификацией схемы фиг.10, в которой на входы 1 и 2 подается сигнал с выходов эмиттерных повторителей на транзисторах 22.1 и 22.2.

Схема фиг.12 соответствует п.6 формулы изобретения. Здесь между базами транзисторов 12 и 13 включен согласующий р-n переход 40, входящий в структуру цепи установления статического потенциала 14.

Описание фиг.13 - фиг.17 дано выше.

Рассмотрим работу заявляемого устройства (фиг.2).

Для определенности будем считать, что базы транзисторов 12 и 13 соединены с общей шиной источников питания 3 и 6. Статический режим МДУ фиг.2 устанавливается резистором 15 и не зависит от напряжения питания.

,

где Iki - коллекторный ток i-го транзистора;

Uэб≈0,6В - напряжение эмиттер-база транзисторов 13 и 12.

Следует заметить, что такое построение МДУ исключает необходимость применения источника напряжения смещения Ec1 (фиг.1), что снижает общее энергопотребление.

Токи Iэ7≈Iк7, Iэ8≈Iк8, Iэ9≈Iк9, Iэ10≈Iк10 создают на резисторах 20 небольшие падения напряжения, так как резисторы 20 выбираются достаточно низкоомными. Изменения выходных токов iвх (или напряжений uвх.1, uвх.2, uвх.4, uвх.5) преобразуются транзисторами 7, 8, 9, 10 в приращение тока в нагрузке (узел 11).

В схеме фиг.5 на входы 1, 2, 4, 5 подаются потенциальные сигналы.

Особенность схемы фиг.6 - подключение без транзисторов 12, 13 к выходу 23 буферного усилителя 24. Схемы фиг.5 и фиг.6 имеют (в сравнении с МДУ-прототипом фиг.1) на порядок более высокие значения коэффициента усиления по напряжению.

В схеме фиг.7, в которой используется токовое управление транзисторами 7, 8, 9, 10, также минимизируется общее энергопотребление МДУ.

Такими же свойствами, а также более высокой симметрией обладают МДУ фиг.8, фиг.9, фиг.10, фиг.11, фиг.12.

Следует заметить, что при высокой идентичности транзисторов в рассматриваемых схемах могут потребоваться цепи запуска статического режима. Пример построения такой цепи дан на фиг.15 (элементы VT1, R3, R4). При этом фиг.14 и фиг.16 показывают, что цепь запуска не влияет на Ку, численные значения которого в 5÷10 раз больше чем в МДУ-прототипе фиг.1.

Особенность схемы фиг.17 состоит в том, что здесь статический режим транзисторов входных дифференциальных каскадов устанавливается источниками опорного тока на транзисторах VT5, VT6, получающих смещение на базах от перегнутого каскода.

Таким образом, благодаря уменьшению энергопотребляющих цепей, а также более высокой амплитуды, положительно влияющей на динамические параметры, заявляемое устройство имеет преимущества в сравнении с известным МДУ.

Источники информации

1. Патент США №4.649.352.

2. Патентная заявка США №2005/0127999.

3. Патент США №6.420.931.

4. Патент США №4.463.319.

5. Патент США №4.649.352.

6. Патент США №5.091.701.

7. Патент США №4.532.479.

1. Мультидифференциальный усилитель, содержащий первый (1) и второй (2) входы, согласованные с шиной (3) положительного источника питания, третий (4) и четвертый (5) входы, согласованные с шиной (6) отрицательного источника питания, первый (7) и второй (8) входные транзисторы с объединенными базами, эмиттеры которых соединены с соответствующими первым (1) и вторым (2) входами, согласованными с шиной (3) положительного источника питания, третий (9) и четвертый (10) входные транзисторы с объединенными базами, эмиттеры которых подключены к соответствующим третьему (4) и четвертому (5) входам, согласованным с шиной (6) отрицательного источника питания, причем коллектор второго (8) и четвертого (10) входных транзисторов объединены и соединены с выходной цепью (11) мультидифференциального усилителя, отличающийся тем, что в схему введены первый (12) и второй (13) дополнительные транзисторы, базы которых связаны с цепью установления статического потенциала (14), коллектор первого (12) дополнительного транзистора соединен с объединенными базами первого (7) и второго (8) входных транзисторов, коллектор второго (13) дополнительного транзистора соединен с объединенными базами третьего (9) и четвертого (10) входных транзисторов, эмиттер первого (12) дополнительного транзистора подключен к коллектору третьего (9) входного транзистора и через дополнительный резистор (15) соединен с эмиттером второго (13) дополнительного транзистора и коллектором первого входного транзистора (7).

2. Устройство по п.1, отличающееся тем, что в качестве первого (16), второго (17) и/или третьего (18) и четвертого (19) источников сигналов, подключенных соответственно к первому (1), второму (2) и/или третьему (4) и четвертому (5) входам мультидифференциального усилителя, используются преобразователи ток-напряжение, реализованные на основе вспомогательных двухполюсников (20) и соединенных с ними управляемых источников входных токов (21).

3. Устройство по п.1, отличающееся тем, что в качестве первого (16), второго (17) и/или третьего (18) и четвертого (19) источников сигнала используются эмиттерные повторители на основе вспомогательных транзисторов (22), причем входные потенциальные сигналы мультидифференциального усилителя подаются на базы вспомогательных транзисторов (22).

4. Устройство по п.1, отличающееся тем, что в качестве цепи установления статического потенциала (14) используется выходная цепь (11) мультидифференциального усилителя.

5. Устройство по п.1, отличающееся тем, что в качестве цепи установления статического потенциала (14) используется выход (23) дополнительного буферного усилителя (24), вход которого соединен с выходной цепью (11) мультидифференциального усилителя.

6. Устройство по п.4, отличающееся тем, что между базами первого (12) и второго (13) дополнительных транзисторов, связанных с цепью установления статического потенциала (14), включен согласующий р-n-переход (40).