Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для использования в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных усилителях, операционных усилителях (ОУ), драйверов линий связи и т.п.). Технический результат - повышение стабильности выходных напряжений. Каскодный дифференциальный усилитель (КДУ) содержит первый (1) и второй (2) входные транзисторы (Т), базы которых подключены к источнику (3) напряжения смещения, а эмиттеры через первый (4) и второй (5) вспомогательные двухполюсники связаны с шиной (6) первого источника питания (ИП) и подключены к первому (7) и второму (8) токовым входам КДУ, первый (9) и второй (10) двухполюсники нагрузки, подключенные к первому (11) и второму (12) выходам КДУ и коллекторам первого (1) и второго (2) входных Т. В схему введены первый (13) и второй (14) дополнительные Т, базы которых соединены с источником (3) напряжения смещения, эмиттеры объединены и подключены к шине (6) первого ИП через первый (15) дополнительный двухполюсник, а коллекторы соединены с коллекторами соответствующих первого (1) и второго (2) входных Т, второй (16) и третий (17) дополнительные двухполюсники, первые выводы которых соединены друг с другом и подключены к базе третьего (18) дополнительного Т, коллектор которого связан с эмиттерами первого (13) и второго (14) дополнительных Т, а эмиттер подключен к шине дополнительного источника напряжения смещения (19), причем первый (11) выход КДУ связан со вторым выводом второго (16) дополнительного двухполюсника, а второй (12) выход КДУ связан со вторым выводом третьего (17) дополнительного двухполюсника. 4 з.п. ф-лы, 12 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления и преобразования аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных усилителях, операционных усилителях (ОУ), драйверах линий связи и т.п.).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (КДУ) [1-40], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УДЗ и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ, на их модификации выдано более 50 патентов для ведущих производителей микроэлектронных изделий. Предлагаемое изобретение относится к данному подклассу устройств.

Одна из задач, которую требуется решать с помощью КДУ, - создание на их основе усилителей с двумя низкоомными противофазными (парофазными) выходами, согласованными с общей шиной источников питания. Усилители с таким так называемым парафазным выходом, наряду с классическими ОУ, образуют основу для проектирования активных фильтров, драйверов линий связей, преобразователей одного входного напряжения в два противофазных сигнала и т.д. При этом во всех этих случаях для получения широкого динамического диапазона при малых напряжениях питания необходимо иметь нулевой (или другой заданный) статический потенциал на парафазных выходах.

Следует отметить, что для известного КДУ (фиг.1) характерны противоречивые требования к параметрам элементов схемы, при которых обеспечивается высокий коэффициент усиления по напряжению Ky и заданный уровень выходных статических напряжений U11=U12 (), которые должны быть «привязаны» к потенциалу общей шины источников питания (приблизительно равна нулю). Действительно, для повышения Ку в качестве двухполюсников 9 и 10 необходимо использовать источники опорного тока, что в то же время приводит к неопределенности статических потенциалов U11, U12 на выходах 11 и 12 (или на выходах 11*, 12* эмиттерных повторителей, которые включаются для согласования схемы с низкими сопротивлениями нагрузки).

Таким образом, на базе известного КДУ не реализуются дифференциальные каскады с повышенным коэффициентом усиления по напряжению и заданным уровнем выходных статических напряжений, «привязанных», например, к общей шине питания.

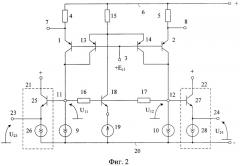

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте США №4.406.990 (фиг.2), содержащий первый 1 и второй 2 входные транзисторы, базы которых подключены к источнику 3 напряжения смещения, а эмиттеры через первый 4 и второй 5 вспомогательные двухполюсники связаны с шиной 6 первого источника питания и подключены к первому 7 и второму 8 токовым входам каскодного дифференциального усилителя, первый 9 и второй 10 двухполюсники нагрузки, подключенные к первому 11 и второму 12 выходам каскодного дифференциального усилителя и коллекторам первого 1 и второго 2 входных транзисторов.

Существенный недостаток известного ДУ состоит в том, что при высоком усилении по напряжению статический потенциал его парафазных выходов нестабилен, что создает проблемы с согласованием выходов КДУ с нагрузкой.

Основная цель предлагаемого изобретения состоит в повышении стабильности выходных напряжений КДУ и создании условий, при которых выходные статические напряжения КДУ устанавливаются на заданном, в том числе, нулевом уровне.

Поставленная цель достигается тем, что в дифференциальном усилителе (фиг.1), содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены к источнику 3 напряжения смещения, а эмиттеры через первый 4 и второй 5 вспомогательные двухполюсники связаны с шиной 6 первого источника питания и подключены к первому 7 и второму 8 токовым входам каскодного дифференциального усилителя, первый 9 и второй 10 двухполюсники нагрузки, подключенные к первому 11 и второму 12 выходам каскодного дифференциального усилителя и коллекторам первого 1 и второго 2 входных транзисторов, предусмотрены новые элементы и связи: в схему введены первый 13 и второй 14 дополнительные транзисторы, базы которых соединены с источником 3 напряжения смещения, эмиттеры объединены и подключены к шине 6 первого источника питания через первый 15 дополнительный двухполюсник, а коллекторы соединены с коллекторами соответствующих первого 1 и второго 2 входных транзисторов, второй 16 и третий 17 дополнительные двухполюсники, первые выводы которых соединены друг с другом и подключены к базе третьего 18 дополнительного транзистора, коллектор которого связан с эмиттерами первого 13 и второго 14 дополнительных транзисторов, а эмиттер подключен к шине дополнительного источника напряжения смещения 19, причем первый 11 выход каскодного дифференциального усилителя связан со вторым выводом второго 16 дополнительного двухполюсника, а второй 12 выход каскодного дифференциального усилителя связан со вторым выводом третьего 17 дополнительного двухполюсника.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

На фиг.3 представлена схема КДУ, соответствующая п.2 формулы изобретения.

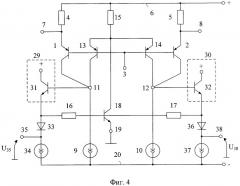

Схема фиг.4 соответствует п.4 формулы изобретения.

Схема фиг.5 совпадает со схемой фиг.2. Однако здесь транзисторы 1, 2, 13 и 14 - полевые, реализуемые (в частном случае так же, как и другие элементы), по техпроцессу SGB25VD.

На фиг.6 приведена схема по п.5 формулы изобретения.

На фиг.7 показана схема КДУ фиг.6 в среде компьютерного моделирования Pspice, а на фиг.8, фиг.9 и фиг.10 - ее амплитудно-частотные характеристики коэффициента усиления по напряжению Ku (фиг.8), входного сопротивления для синфазного сигнала (фиг.9) и входного дифференциального сопротивления (фиг.10).

Схема фиг.11 также соответствует фиг.6 в среде Cadance на моделях интегральных СВЧ-транзисторов IHP. На фиг.12 представлена амплитудно-частотная характеристика коэффициента усиления по напряжению схемы фиг.11.

Каскодный дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены к источнику 3 напряжения смещения, а эмиттеры через первый 4 и второй 5 вспомогательные двухполюсники связаны с шиной 6 первого источника питания и подключены к первому 7 и второму 8 токовым входам каскодного дифференциального усилителя, первый 9 и второй 10 двухполюсники нагрузки, подключенные к первому 11 и второму 12 выходам каскодного дифференциального усилителя и коллекторам первого 1 и второго 2 входных транзисторов. В схему введены первый 13 и второй 14 дополнительные транзисторы, базы которых соединены с источником 3 напряжения смещения, эмиттеры объединены и подключены к шине 6 первого источника питания через первый 15 дополнительный двухполюсник, а коллекторы соединены с коллекторами соответствующих первого 1 и второго 2 входных транзисторов, второй 16 и третий 17 дополнительные двухполюсники, первые выводы которых соединены друг с другом и подключены к базе третьего 18 дополнительного транзистора, коллектор которого связан с эмиттерами первого 13 и второго 14 дополнительных транзисторов, а эмиттер подключен к шине дополнительного источника напряжения смещения 19, причем первый 11 выход каскодного дифференциального усилителя связан со вторым выводом второго 16 дополнительного двухполюсника, а второй 12 выход каскодного дифференциального усилителя связан со вторым выводом третьего 17 дополнительного двухполюсника.

На фиг.2 (п.2 формулы изобретения) в качестве шины дополнительного источника напряжения смещения 19 используется общая шина первого 6 и второго 20 источников питания.

На фиг.3, в соответствии с п.3 формулы изобретения, к первому 1 выходу каскодного дифференциального усилителя подключен вход первого эмиттерного повторителя 21, а ко второму выходу 12 каскодного дифференциального усилителя подключен вход второго 22 эмиттерного повторителя, соответствующие выходы которых являются вспомогательными выходами 23 и 24 каскодного дифференциального усилителя.

На фиг.4, в соответствии с п.4 формулы изобретения, между первым 11 выходом каскодного дифференциального усилителя и вторым выводом второго 16 дополнительного двухполюсника включен первый эмиттерный повторитель 29 на основе первого 31 р-n-р входного транзистора, а между вторым 12 выходом каскодного дифференциального усилителя и вторым выводом третьего 17 дополнительного двухполюсника включен второй эмиттерный повторитель 30 на основе второго 32 n-p-n входного транзистора, причем эмиттер первого n-p-n входного транзистора связан с шиной 20 второго источника питания через последовательно соединенные первый р-n переход 33 и первый 34 источник опорного тока, общий узел которых является первым 35 дополнительным выходом каскодного дифференциального усилителя, а эмиттер второго 32 n-p-n входного транзистора связан с шиной 20 второго источника питания через последовательно соединенные второй р-n переход 36 и второй 37 источник опорного тока, общий узел которых является вторым 38 дополнительным выходом каскодного дифференциального усилителя.

На фиг.5 в качестве транзисторов 1, 2, 13, 14 используются полевые транзисторы.

На схеме фиг.6, соответствующей п.5 формулы изобретения, в качестве шины дополнительного источника напряжения смещения 19 используется общая эмиттерная цепь дополнительного входного параллельно-балансного каскада на основе вспомогательных транзисторов 39 и 40 и дополнительного двухполюсника 41 в их общей эмиттерной цепи, причем коллекторы вспомогательных транзисторов 39 и 40 подключены к первому 7 и второму 8 токовым входам каскодного дифференциального усилителя.

Рассмотрим работу заявляемого ДУ.

Статический режим по току транзисторов схемы фиг.2 устанавливается двухполюсниками 9 и 10, а также за счет соответствующего выбора источника напряжения смещения 3 и сопротивлений двухполюсников 4, 15, 5.

Уровень выходных статических напряжений КДУ U11 и U12 отличается от потенциала общей шины на +0,7В. Поэтому при введении эмиттерных повторителей 21 и 22 (фиг.2) напряжение на выходах 23 и 24 будет близко к нулю, что является необходимым условием для введения обратных связей на постоянном токе и получения максимального динамического диапазона.

В схеме фиг.4 нулевые значения выходных статических напряжений U35≈U38=0 обеспечиваются р-n переходами 33 и 36. При этом эмиттерные повторители 29 и 30 повышают коэффициент усиления КДУ по напряжению при сравнительно низкоомных сопротивлениях резисторов 16 и 17.

Особенность схемы фиг.6 состоит в том, что здесь выходные статические напряжения U12 и U11 равны входному синфазному напряжению дополнительного параллельно-балансного каскада (33, 40, 41).

Схема фиг.6 имеет повышенный коэффициент ослабления входных синфазных сигналов (более 200 дБ).

Приведенные на фиг.8, фиг.9 и фиг.10 результаты моделирования предлагаемого КДУ показывают, что в заявляемой схеме разрешаются технические противоречия, характерные для КДУ-прототипа.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6.304.143

2. Патент США №5.418.491

3. Патент США №4.463.319

4. Патент США №6.717.474

5. Патент США №6.734.720

6. Патент США №4.723.111

7. Патент США №4.293.824

8. Патент США №5.323.121

9. Патент США №5.091.701

10. Патент США №4.406.990

11. Патент США №5.422.600

12. Патент США №6.788.143

13. Патент США №4.274.061

14. Патент США №5.327.100

15. Патент США №5.786.729

16. Патент США №3.644.838

17. Патент США №4.600.893

18. Патент США №4.390.850

19. Патент США №6.628.168

20. Матавкин В.В. Быстродействующие операционные усилители. - М. Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

21. Патент США №6.218.900, фиг.1

22. Патентная заявка US 2002/0196079

23. Патент США Re 30.587

24. Патент ЕР 1.227.580

25. Патент США №6.714.076

26. Патентная заявка US 2004/0090268 A1

27. Патент США №4.959.622, фиг.1

28. Патент США №6.018.268

29. Патент США №5.952.882

30. Патент США №6.580.325

31. Патент США №6.965.266

32. Патент США №6.867.643

33. Патент США №6.236.270

34. Патент США №6.229.394

35. Патент США №5.734.296

36. Патент США №5.477.190

37. Патент США №6.084.475

38. Патент США №3.733.559

39. Патентная заявка US 2005/0001682 A1

40. Патент США №6.300.831

1. Каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены к источнику (3) напряжения смещения, а эмиттеры через первый (4) и второй (5) вспомогательные двухполюсники связаны с шиной (6) первого источника питания и подключены к первому (7) и второму (8) токовым входам каскодного дифференциального усилителя, первый (9) и второй (10) двухполюсники нагрузки, подключенные к первому (11) и второму (12) выходам каскодного дифференциального усилителя и коллекторам первого (1) и второго (2) входных транзисторов, отличающийся тем, что в схему введены первый (13) и второй (14) дополнительные транзисторы, базы которых соединены с источником (3) напряжения смещения, эмиттеры объединены и подключены к шине (6) первого источника питания через первый (15) дополнительный двухполюсник, а коллекторы соединены с коллекторами соответствующих первого (1) и второго (2) входных транзисторов, второй (16) и третий (17) дополнительные двухполюсники, первые выводы которых соединены друг с другом и подключены к базе третьего (18) дополнительного транзистора, коллектор которого связан с эмиттерами первого (13) и второго (14) дополнительных транзисторов, а эмиттер подключен к шине дополнительного источника напряжения смещения (19), причем первый (11) выход каскодного дифференциального усилителя связан со вторым выводом второго (16) дополнительного двухполюсника, а второй (12) выход каскодного дифференциального усилителя связан со вторым выводом третьего (17) дополнительного двухполюсника.

2. Устройство по п.1, отличающееся тем, что в качестве шины дополнительного источника напряжения смещения (19) используется общая шина первого (6) и второго (20) источников питания.

3. Устройство по п.2, отличающееся тем, что к первому (1) выходу каскодного дифференциального усилителя подключен вход первого эмиттерного повторителя (21), а ко второму выходу (12) каскодного дифференциального усилителя подключен вход второго (22) эмиттерного повторителя, соответствующие выходы которых являются вспомогательными выходами (23) и (24) каскодного дифференциального усилителя.

4. Устройство по п.2, отличающееся тем, что между первым (11) выходом каскодного дифференциального усилителя и вторым выводом второго (16) дополнительного двухполюсника включен первый эмиттерный повторитель (29) на основе первого (31) p-n-p-входного транзистора, а между вторым (12) выходом каскодного дифференциального усилителя и вторым выводом третьего (17) дополнительного двухполюсника включен второй эмиттерный повторитель (30) на основе второго (32) n-p-n-входного транзистора, причем эмиттер первого n-p-n-входного транзистора связан с шиной (20) второго источника питания через последовательно соединенные первый p-n-переход (33) и первый (34) источник опорного тока, общий узел которых является первым (35) дополнительным выходом каскодного дифференциального усилителя, а эмиттер второго (32) n-p-n-входного транзистора связан с шиной (20) второго источника питания через последовательно соединенные второй p-n-переход (36) и второй (37) источник опорного тока, общий узел которых является вторым (38) дополнительным выходом каскодного дифференциального усилителя.

5. Устройство по п.1, отличающееся тем, что в качестве шины дополнительного источника напряжения смещения (19) используется общая эмиттерная цепь дополнительного входного параллельно-балансного каскада на основе вспомогательных транзисторов (39) и (40) и дополнительного двухполюсника (41) в их общей эмиттерной цепи, причем коллекторы вспомогательных транзисторов (39) и (40) подключены к первому (7) и второму (8) токовым входам каскодного дифференциального усилителя.