Управляемый усилитель переменного тока

Иллюстрации

Показать всеИспользование: в области радиотехники и связи. Технический результат заключается в повышении коэффициента подавления сигнала управления в широком диапазоне частот. Усилитель содержит первый (1) и второй (3) входные транзисторы, двухполюсник (5) местной отрицательной обратной связи, симметричную цепь нагрузки (6), первый (9) блокирующий конденсатор, первый (11) и второй (12) токостабилизирующие двухполюсники, второй блокирующий конденсатор (13), первый (14) и второй (15) дополнительные транзисторы, дополнительный двухполюсник (16) отрицательной обратной связи. 8 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в качестве усилителя переменного тока, коэффициент передачи по напряжению которого (Кu) зависит от уровня сигнала управления (uу). Такие устройства применяются в структуре аналоговых микросхем различного функционального назначения, системах автоматической регулировки усиления, аналоговых псремножителях сигналов и т.п.

В современных адаптивных СФ-блоках систем связи и телекоммуникаций широко используется в качестве управляемого усилителя классический дифференциальный каскад с резистором местной отрицательной обратной связи. При этом на его основе выполняются разные модификации управляемых усилителей [1-26].

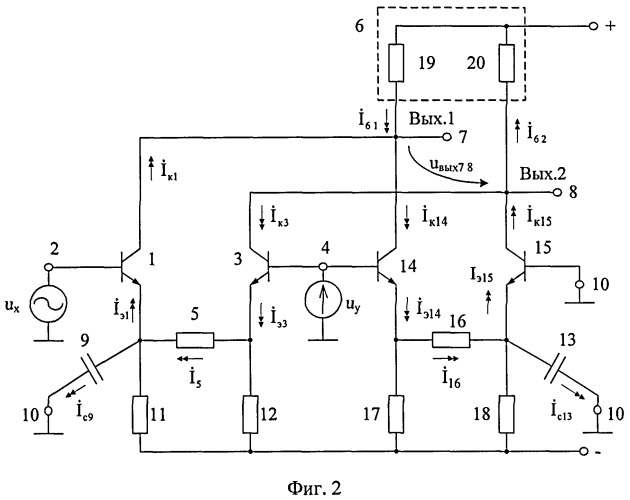

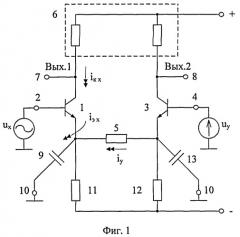

Наиболее близким по технической сущности к заявляемому устройству является управляемый дифференциальный каскад, описанный в патенте США №5.126.586, fig.1. Он содержит (фиг.1) первый 1 входной транзистор, база которого соединена с основным 2 входом управляемого усилителя, второй 3 входной транзистор, база которого соединена с управляющим входом 4 управляемого усилителя, двухполюсник 5 местной отрицательной обратной связи, включенный между эмиттерами первого 1 и второго 3 входных транзисторов, симметричную цепь нагрузки 6, связанную с коллекторами первого 1 и второго 3 входных транзисторов и дифференциальным выходом 7 и 8 управляемого усилителя, первый 9 блокирующий конденсатор, включенный по переменному току между эмиттером первого 1 входного транзистора и общей шиной 10 источников питания, первый 11 токостабилизирующий двухполюсник, связанный с эмиттером первого 1 входного транзистора, второй 12 токостабилизирующий двухполюсник, соединенный с эмиттером второго 3 входного транзистора, второй блокирующий конденсатор 13.

Существенный недостаток известного управляемого усилителя (УУ) состоит в том, что в нем не обеспечивается эффективное подавление сигнала управления ни на низких, ни на высоких частотах. Это не позволяет выполнять на его основе различные функциональные узлы современных систем связи, для которых характерно одно из важнейших требований - отсутствие гармонических составляющих сигнала управления uy на выходе.

Основная цель предлагаемого изобретения состоит в повышении на несколько порядков коэффициента подавления сигнала управления в широком диапазоне частот.

Поставленная цель достигается тем, что в управляемом усилителе переменного тока (фиг.1), содержащем первый 1 входной транзистор, база которого соединена с основным 2 входом управляемого усилителя, второй 3 входной транзистор, база которого соединена с управляющим входом 4 управляемого усилителя, двухполюсник 5 местной отрицательной обратной связи, включенный между эмиттерами первого 1 и второго 3 входных транзисторов, симметричную цепь нагрузки 6, связанную с коллекторами первого 1 и второго 3 входных транзисторов и дифференциальным выходом 7 и 8 управляемого усилителя, первый 9 блокирующий конденсатор, включенный по переменному току между эмиттером первого 1 входного транзистора и общей шиной 10 источников питания, первый 11 токостабилизирующий двухполюсник, связанный с эмиттером первого 1 входного транзистора, второй 12 токостабилизирующий двухполюсник, соединенный с эмиттером второго 3 входного транзистора, второй блокирующий конденсатор 13, предусмотрены новые элементы и связи - в схему введены первый 14 и второй 15 дополнительные транзисторы, эмиттеры которых соединены друг с другом через дополнительный двухполюсник 16 отрицательной обратной связи и подключены к соответствующим первому 17 и второму 18 дополнительным токостабилизирующим двухполюсникам, база первого 14 дополнительного транзистора соединена с управляющим входом 4 управляемого усилителя, база второго 15 дополнительного транзистора связана по переменному току с общей шиной 10 источников питания, причем коллектор первого дополнительного транзистора 14 соединен с коллектором первого 1 входного транзистора, коллектор второго 15 дополнительного транзистора соединен с коллектором второго 3 входного транзистора, а второй блокирующий конденсатор 13 включен по переменному току между эмиттером второго 15 дополнительного транзистора и общей шиной 10 источников питания.

На фиг.1 показана схема УУ-прототипа, а на фиг.2 - схема заявляемого УУ в соответствии с формулой изобретения.

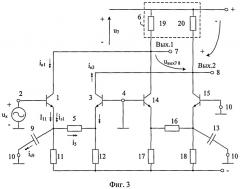

На фиг.3 показаны токи и напряжения УУ фиг.2 для случая, когда сигнал управления равен нулю (uу=0). Это позволяет проследить пути прохождения переменных токов в схеме, обусловленных сигналом на входе 2.

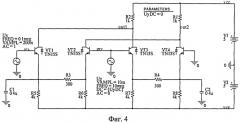

На фиг.4 приведена схема УУ фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Результаты ее моделирования показаны на фиг.5 - 7:

- зависимость коэффициента усиления по напряжению Кu от напряжения управления Uу в диапазоне средних частот (фиг.5);

- зависимость коэффициента усиления Кu от частоты при разных напряжениях управления (фиг.6);

- зависимость коэффициента подавления напряжения управления (Кп=uвых/uу) от частоты для заявляемого УУ фиг.4 (фиг.7).

На чертеже фиг.8 показана зависимость коэффициента подавления напряжения управления (Кп=uвых/uу) от частоты для УУ-прототипа фиг.1.

Управляемый усилитель переменного тока фиг.2 содержит первый 1 входной транзистор, база которого соединена с основным 2 входом управляемого усилителя, второй 3 входной транзистор, база которого соединена с управляющим входом 4 управляемого усилителя, двухполюсник 5 местной отрицательной обратной связи, включенный между эмиттерами первого 1 и второго 3 входных транзисторов, симметричную цепь нагрузки 6, связанную с коллекторами первого 1 и второго 3 входных транзисторов и дифференциальным выходом 7 и 8 управляемого усилителя, первый 9 блокирующий конденсатор, включенный по переменному току между эмиттером первого 1 входного транзистора и общей шиной 10 источников питания, первый 11 токостабилизирующий двухполюсник, связанный с эмиттером первого 1 входного транзистора, второй 12 токостабилизирующий двухполюсник, соединенный с эмиттером второго 3 входного транзистора, второй блокирующий конденсатор 13. В схему введены первый 14 и второй 15 дополнительные транзисторы, эмиттеры которых соединены друг с другом через дополнительный двухполюсник 16 отрицательной обратной связи и подключены к соответствующим первому 17 и второму 18 дополнительным токостабилизирующим двухполюсникам, база первого 14 дополнительного транзистора соединена с управляющим входом 4 управляемого усилителя, база второго 15 дополнительного транзистора связана по переменному току с общей шиной 10 источников питания, причем коллектор первого дополнительного транзистора 14 соединен с коллектором первого 1 входного транзистора, коллектор второго 15 дополнительного транзистора соединен с коллектором второго 3 входного транзистора, а второй блокирующий конденсатор 13 включен по переменному току между эмиттером второго 15 дополнительного транзистора и общей шиной 10 источников питания.

В качестве симметричной цепи нагрузки 6 могут применяться резисторы 19, 20 или источники опорного тока, а также другие подсхемы.

В схеме фиг.3 сигнал управления равен нулю. Представленные здесь токи и напряжения характеризуют работу схемы при усилении сигнала ux по входу 2.

Рассмотрим работу управляемого усилителя фиг.2.

В диапазоне средних частот при достаточно высокоомном резисторе 5 усиление сигнала ux по основному входу 2 при uу=0 обеспечивается транзистором 1, включенным по традиционной схеме с общим эмиттером:

где Rн.экв - эквивалентное сопротивление цепи нагрузки 6 по выходу 7;

R19 - сопротивление двухполюсника 19 цепи нагрузки 6;

φт≈25 мВ - температурный потенциал;

I11 - статический ток эмиттера транзистора 1;

rэ1=φт/I11 - сопротивление эмиттерного перехода транзистора 1.

В этой схеме первый 9 блокирующий конденсатор обеспечивает «подключение» по переменному току эмиттера транзистора 1 к общей шине 10 источников питания.

Если на вход 4 подается постоянное напряжение Uу≠0, то это приводит к уменьшению тока эмиттера транзистора 1, изменению его сопротивления эмиттерного перехода rэ1 и, как следствие, к изменению Кu (1).

За счет введения новых элементов схемы и связей между ними в схеме фиг.2 обеспечивается высокое подавление на дифференциальном выходе 7-8 сигнала управления. Действительно, при достаточно высокоомных двухполюсниках 11, 12, 17 и 18 комплекс тока через двухполюсник 5

где - комплекс напряжения управления

uу;

- комплекс эмиттерного тока транзистора 3;

- комплекс коллекторного тока транзистора 3.

С другой стороны, комплексы эмиттерного и коллекторного токов транзистора 1:

где - коэффициент деления тока между эмиттером транзистора 1 и емкостью

Сд, причем

Поэтому коллекторный ток транзистора 1

С другой стороны сигнал управления uу создает коллекторный ток транзистора 14

В свою очередь ток делится между эмиттером транзистора 15 и вторым блокирующим конденсатором 13

где .

В результате анализа схемы можно найти результирующие токи в двухполюсниках нагрузки 19 и 20 и соответствующие выходные дифференциальные напряжения УУ:

Если R19=R20=Rн, то

Полагая, что в схеме фиг.2 выполняются равенства rэ1=rэ15, R5=R16, rэ14=rэ3, Сд=С13, с учетом уравнений (5), (6), (8) можно сделать вывод о том, что в широком диапазоне частот в формуле (12) обеспечивается попарная взаимная компенсация слагаемых и , и . Это означает, что выходное дифференциальное напряжение Uвыx УУ фиг.2 не зависит от напряжения управления, а коэффициент подавления Kп=uвых/uу≈0.

Таким образом, в схеме фиг.2 компенсируется частотная зависимость коэффициента подавления сигнала управления Кп, который остается достаточно малым в более широком диапазоне частот, чем в схеме фиг.1.

Данный теоретический вывод подтверждается результатами компьютерного моделирования схемы фиг.2, показанными на чертеже фиг.7 - здесь подавление сигнала управления (при полной идентичности элементов схемы) достигает 300 дБ при f=0÷1 ГГц, что значительно лучше, чем в схеме УУ-прототипе (фиг.8).

Замечательная особенность заявляемого УУ состоит также в том, что он может иметь напряжения питания ±1,5 В, что позволяет использовать для его реализации перспективные SiGe техпроцессы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка США №2004/0183599

2. Патентная заявка США №2004/0178850

3. Патентная заявка США №2006/0044064

4. Патентная заявка США №2008/0088374

5. Патент США №4.575.687

6. Патентная заявка США №2005/0179493

7. Патент США №6.456.142

8. Патент США №5.184.088

9. Патент США №6.703.899

10. Патентная заявка США №2008/0191803

11. Патент США №6.525.606, фиг.6

12. Патент США №6.980.054, fig.4

13. Патент США №6.980.053

14. Патентная заявка США №2005/0258900

15. Патентная заявка США №2003/0011429

16. Патент США №6.972.625

17. Патентная заявка США №2006/0022748

18. Патент США №5.157.360

19. Патентная заявка США №2005/0038615

20. Патент GB 2.318.470

21. Патент США №5.126.586

22. Патент США 4.511.852

23. Патент США 4.881.043

24. Патент США №6.891.436, fig.1

25. Патент США №6.933.783, фиг.20, 21

26. Патент США №4.267.518

Управляемый усилитель переменного тока, содержащий первый (1) входной транзистор, база которого соединена с основным (2) входом управляемого усилителя, второй (3) входной транзистор, база которого соединена с управляющим входом (4) управляемого усилителя, двухполюсник (5) местной отрицательной обратной связи, включенный между эмиттерами первого (1) и второго (3) входных транзисторов, симметричную цепь нагрузки (6), связанную с коллекторами первого (1) и второго (3) входных транзисторов и дифференциальным выходом (7) и (8) управляемого усилителя, первый (9) блокирующий конденсатор, включенный по переменному току между эмиттером первого (1) входного транзистора и общей шиной (10) источников питания, первый (11) токостабилизирующий двухполюсник, связанный с эмиттером первого (1) входного транзистора, второй (12) токостабилизирующий двухполюсник, соединенный с эмиттером второго (3) входного транзистора, второй блокирующий конденсатор (13), отличающийся тем, что в схему введены первый (14) и второй (15) дополнительные транзисторы, эмиттеры которых соединены друг с другом через дополнительный двухполюсник (16) отрицательной обратной связи и подключены к соответствующим первому (17) и второму (18) дополнительным токостабилизирующим двухполюсникам, база первого (14) дополнительного транзистора соединена с управляющим входом (4) управляемого усилителя, база второго (15) дополнительного транзистора связана по переменному току с общей шиной (10) источников питания, причем коллектор первого дополнительного транзистора (14) соединен с коллектором первого (1) входного транзистора, коллектор второго (15) дополнительного транзистора соединен с коллектором второго (3) входного транзистора, а второй блокирующий конденсатор (13) включен по переменному току между эмиттером второго (15) дополнительного транзистора и общей шиной (10) источников питания.