Регистратор параметров аварийных ситуаций в электрических сетях повышенной точности (варианты)

Иллюстрации

Показать всеИзобретение относится к области информационно-измерительной и вычислительной техники и может быть использовано в электроэнергетике для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях. Техническим результатом является расширение функциональных возможностей устройства за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации. Технический результат достигается благодаря тому, что: 1) первый вариант реализации регистратора содержит группу аналоговых датчиков, группу цифровых датчиков, многоканальные первый аналоговый (МАК) и второй цифровой (МЦК) коммутаторы, формирователь модуля, нуль-орган (НО), источник опорных напряжений (ИОН), дешифратор, первое, второе и третье оперативные запоминающие устройства (ОЗУ), постоянное запоминающее устройство (ПЗУ), микроконтроллер, таймер, первый - четвертый одноканальные аналоговые коммутаторы, аналого-цифровой преобразователь (АЦП), первый и второй аналоговые компараторы (АК), регистр, первый - пятый счетчики, первый - третий триггеры, элемент И-НЕ, первый - пятый элементы И, первый - четвертый элементы ИЛИ, первый - шестнадцатый одновибраторы, числовой компаратор, генератор тактовых импульсов (ГТИ); 2) второй вариант реализации регистратора содержит группу аналоговых датчиков, группу цифровых датчиков, первый МАК и второй МЦК, формирователь модуля, НО, ИОН, дешифратор, первое, второе и третье ОЗУ, ПЗУ, микроконтроллер, таймер, первый - третий одноканальные аналоговые коммутаторы, ГТИ, АЦП, регистр, первый - пятый счетчики, первый - пятый элементы ИЛИ, первый - четырнадцатый одновибраторы, первый - третий триггеры, элемент И-НЕ, первый - шестой элементы И, первый и второй числовые компараторы, блок задания кода границы. 2 н. и 2 з.п. ф-лы, 3 ил.

Реферат

Предлагаемое изобретение относится к области информационно-измерительной и вычислительной техники и может быть использовано в электроэнергетике для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях.

Известно устройство для сбора, преобразования и передачи результатов измерения параметров физической среды (Патент 2081452 РФ, МПК G06F 17/40. Устройство для сбора, преобразования и передачи результатов измерения параметров физической среды / Т.Г.Самхарадзе (РФ). - 1997, Бюл. №16), содержащее аналоговые измерительные датчики, блок управления с адресно-информационной и командной магистралью, генератор тактовых импульсов, коммутатор, блок управления коммутатором, канал управления опросом датчиков, аналого-цифровой преобразователь, буферное запоминающее устройство, блок регистров результата, формирователь передаваемой информации, узел передачи данных и канал ввода-вывода.

Недостатком указанного аналога являются его узкие функциональные возможности - аналог предназначен для наблюдения за процессом изменения параметров контролируемых величин, но не может быть использован для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

Наиболее близким техническим решением к предлагаемому является устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды (Патент 2079881 РФ, МПК G06F 17/40. Устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды / Т.Г.Самхарадзе (РФ). - 1997, Бюл. №14), содержащее первую и вторую группы аналоговых измерительных датчиков, первую и вторую группы аналого-цифровых преобразователей, блоки обработки данных первой группы и блоки обработки данных второй группы, первый и второй коммутаторы, первый и второй блоки управления коммутаторами, четыре оперативных запоминающих устройства, два буферных запоминающих устройства, два формирователя передаваемой информации, два узла передачи данных, канал ввода-вывода и управляющий вычислительный комплекс с адресно-информационной и командной магистралью.

Недостатком прототипа также являются узкие функциональные возможности - прототип предназначен для наблюдения за процессом изменения параметров контролируемых величин, но не может быть использован для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

Технические задачи, решаемые изобретением - расширение функциональных возможностей устройства за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

Указанные технические задачи (в первом варианте реализации предлагаемого технического решения) решаются тем, что в устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды, содержащее микроконтроллер, первое, второе и третье оперативные запоминающие устройства, первый счетчик, первый и второй многоканальные коммутаторы, аналого-цифровой преобразователь, группу аналоговых датчиков, генератор тактовых импульсов, выходы которого соединены: третий - с тактовым входом первого счетчика, первый - с тактовым входом микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго и третьего оперативных запоминающих устройств, входы управления записью которых подключены к шине управления микроконтроллера, к которой также подключен вход управления состоянием выходов выходных регистров третьего оперативного запоминающего устройства, информационный выход первого счетчика соединен с управляющим входом первого многоканального коммутатора, информационные входы которого подключены к выходам группы аналоговых датчиков, дополнительно введены постоянное запоминающее устройство, числовой компаратор, таймер, регистр, второй - пятый счетчики, первый - третий триггеры, формирователь модуля, нуль-орган, источник опорных напряжений, дешифратор, первый - четвертый одноканальные аналоговые коммутаторы, первый и второй аналоговые компараторы, элемент И-НЕ, первый - пятый элементы И, первый - четвертый элементы ИЛИ, первый - шестнадцатый одновибраторы, группа цифровых датчиков, выходы которых соединены с информационными входами второго многоканального коммутатора, управляющий вход которого объединен с первым входом числового компаратора, информационным входом регистра и группой старших разрядов адресного входа первого оперативного запоминающего устройства и подключен к информационному выходу первого счетчика, третий выход генератора тактовых импульсов соединен с объединенными первым входом четвертого элемента ИЛИ и инверсным входом первого одновибратора, выход которого соединен с объединенными управляющим входом четвертого одноканального аналогового коммутатора и инверсным входом двенадцатого одновибратора, выход которого соединен со входом запуска аналого-цифрового преобразователя, информационный вход которого подключен к выходу формирователя модуля, тактовый вход подключен ко второму выходу генератора тактовых импульсов, а информационный выход соединен с группой младших разрядов информационного входа первого оперативного запоминающего устройства, вход управления записью которого объединен с входом установки нуля пятого счетчика и входом второго одновибратора и подключен к выходу окончания цикла преобразования аналого-цифрового преобразователя, выход второго одновибратора соединен с объединенными третьим входом первого элемента И и инверсным входом третьего одновибратора, выходы которого соединены: прямой - с первым входом первого элемента ИЛИ, а инверсный - через четвертый одновибратор с первым входом элемента И-НЕ, второй вход которого подключен к выходу второго многоканального коммутатора, соединенному через пятый одновибратор со входом управления записью регистра, вход управления состоянием выхода которого подключен к шине управления микроконтроллера, выход регистра соединен с шиной данных микроконтроллера и вторым входом числового компаратора, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах числового компаратора) соединен с объединенными первыми входами первого, второго и третьего элементов И, выход элемента И-НЕ соединен со входом установки единицы первого триггера, прямой выход которого соединен с объединенными вторыми входами первого и четвертого элементов И и входом шестого одновибратора, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера и через седьмой одновибратор - со входом установки единицы второго триггера, прямой выход которого через пятый элемент И соединен с тактовым входом третьего триггера, выходы которого соединены соответственно через восьмой и девятый одновибраторы со вторыми входами второго и третьего элементов И, выход которого соединен с тактовым входом второго счетчика и вторыми входами второго и первого элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика и через четвертый элемент И с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом четвертого счетчика, информационный выход которого соединен с адресной шиной микроконтроллера, вход управления состоянием информационного выхода подключен к шине управления микроконтроллера, а выход переноса соединен со входом десятого одновибратора, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера и входом установки нуля четвертого счетчика, инверсный - со входом установки нуля первого триггера, выход переноса второго счетчика соединен со входом одиннадцатого одновибратора, выходы которого соединены: прямой - со входом установки нуля второго счетчика, инверсный - со входами установки нуля второго и третьего триггеров, информационный выход третьего счетчика соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, соединенной с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, выход первого элемента И через третий элемент ИЛИ соединен со входом управления записью второго оперативного запоминающего устройства, тактовый вход таймера объединен с вторым входом пятого элемента И и подключен к первому выходу генератора тактовых импульсов, вход захвата и вход управления состоянием выходов выходных регистров таймера подключены к шине управления микроконтроллера, а информационный выход таймера соединен с шиной данных микроконтроллера, выход первого многоканального коммутатора соединен с объединенными информационными входами нуль-органа и формирователя модуля, выход которого через четвертый одноканальный аналоговый коммутатор соединен с объединенными вторыми входами первого и второго аналоговых компараторов, первые входы которых подключены соответственно ко второму и первому выходам источника опорных напряжений, первый - третий выходы которого соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов подключены соответственно к первому - третьему выходам дешифратора, выходы первого и второго аналоговых компараторов через последовательно соединенные попарно тринадцатый и четырнадцатый, а также пятнадцатый и шестнадцатый одновибраторы связаны соответственно со вторым и третьим входами четвертого элемента ИЛИ, выход которого соединен с тактовым входом пятого счетчика, выход которого соединен с объединенными входом дешифратора и группой средних разрядов информационного входа первого оперативного запоминающего устройства, старший разряд которого объединен с первым управляющим входом формирователя модуля и подключен к прямому выходу нуль-органа, инверсный выход которого соединен со вторым управляющим входом формирователя модуля.

Указанные технические задачи (во втором варианте реализации предлагаемого технического решения) решаются тем, что в устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды, содержащее микроконтроллер, первое, второе и третье оперативные запоминающие устройства, первый счетчик, первый и второй многоканальные коммутаторы, аналого-цифровой преобразователь, группу аналоговых датчиков, генератор тактовых импульсов, выходы которого соединены: третий - с тактовым входом первого счетчика, первый - с тактовым входом микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго и третьего оперативных запоминающих устройств, входы управления записью которых подключены к шине управления микроконтроллера, к которой также подключен вход управления состоянием выходов выходных регистров третьего оперативного запоминающего устройства, информационный выход первого счетчика соединен с управляющим входом первого многоканального коммутатора, информационные входы которого подключены к выходам группы аналоговых датчиков, дополнительно введены постоянное запоминающее устройство, источник опорных напряжений, первый - третий одноканальные аналоговые коммутаторы, первый и второй числовые компараторы, второй - пятый счетчики, первый - третий триггеры, формирователь модуля, нуль-орган, таймер, регистр, дешифратор, элемент И-НЕ, первый - шестой элементы И, первый - пятый элементы ИЛИ, первый - двенадцатый одновибраторы, блок задания кода границы, группа цифровых датчиков, выходы которых соединены с информационными входами второго многоканального коммутатора, управляющий вход которого объединен с первым входом первого числового компаратора, информационным входом регистра и группой старших разрядов адресного входа первого оперативного запоминающего устройства и подключен к информационному выходу первого счетчика, третий выход генератора тактовых импульсов соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с тактовым входом пятого счетчика и через первый одновибратор - с входом запуска аналого-цифрового преобразователя, информационный вход которого подключен к выходу формирователя модуля, тактовый вход подключен ко второму выходу генератора тактовых импульсов, а информационный выход соединен с объединенными вторым входом второго числового компаратора и группой младших разрядов информационного входа первого оперативного запоминающего устройства, вход управления записью которого объединен с входом установки нуля пятого счетчика и входом второго одновибратора и через шестой элемент И подключен к выходу окончания цикла преобразования аналого-цифрового преобразователя, выход второго одновибратора соединен с объединенными третьим входом первого элемента И и инверсным входом третьего одновибратора, выходы которого соединены: прямой - с объединенными входом установки нуля аналого-цифрового преобразователя и первым входом первого элемента ИЛИ, а инверсный - через четвертый одновибратор с первым входом элемента И-НЕ, второй вход которого подключен к выходу второго многоканального коммутатора, соединенному через пятый одновибратор со входом управления записью регистра, вход управления состоянием выхода которого подключен к шине управления микроконтроллера, выход регистра соединен с шиной данных микроконтроллера и вторым входом первого числового компаратора, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах первого и второго числовых компараторов) соединен с объединенными первыми входами первого, второго и третьего элементов И, выход элемента И-НЕ соединен со входом установки единицы первого триггера, прямой выход которого соединен с объединенными вторыми входами первого и четвертого элементов И и входом шестого одновибратора, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера и через седьмой одновибратор - со входом установки единицы второго триггера, прямой выход которого через пятый элемент И соединен с тактовым входом третьего триггера, выходы которого соединены соответственно через восьмой и девятый одновибраторы со вторыми входами второго и третьего элементов И, выход которого соединен с тактовым входом второго счетчика и вторыми входами второго и первого элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика и через четвертый элемент И с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом четвертого счетчика, информационный выход которого соединен с адресной шиной микроконтроллера, вход управления состоянием информационного выхода подключен к шине управления микроконтроллера, а выход переноса соединен со входом десятого одновибратора, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера и входом установки нуля четвертого счетчика, инверсный - со входом установки нуля первого триггера, выход переноса второго счетчика соединен со входом одиннадцатого одновибратора, выходы которого соединены: прямой - со входом установки нуля второго счетчика, инверсный - со входами установки нуля второго и третьего триггеров, информационный выход третьего счетчика соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, соединенной с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, выход первого элемента И через третий элемент ИЛИ соединен со входом управления записью второго оперативного запоминающего устройства, тактовый вход таймера объединен с вторым входом пятого элемента И и подключен к первому выходу генератора тактовых импульсов, вход захвата и вход управления состоянием выходов выходных регистров таймера подключены к шине управления микроконтроллера, а информационный выход таймера соединен с шиной данных микроконтроллера, выход пятого счетчика соединен с объединенными входом дешифратора и группой средних разрядов информационного входа первого оперативного запоминающего устройства, старший разряд которого объединен с первым управляющим входом формирователя модуля и подключен к прямому выходу нуль-органа, инверсный выход которого соединен со вторым управляющим входом формирователя модуля, информационный вход которого объединен с входом нуль-органа и подключен к выходу первого многоканального коммутатора, первый - третий выходы источника опорных напряжений соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов подключены соответственно к первому - третьему выходам дешифратора, выход блока задания кода границы соединен с первым входом второго числового компаратора, выходы которого соединены: «А<В» - через двенадцатый одновибратор со вторым входом четвертого элемента ИЛИ, «А=В» и «А>В» - со вторым и третьим входами пятого элемента ИЛИ, первый вход которого подключен к первому выходу дешифратора, а выход пятого элемента ИЛИ соединен со вторым входом шестого элемента И.

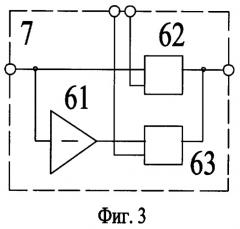

Формирователь модуля содержит инвертор, четвертый и пятый одноканальные аналоговые коммутаторы, выходы которых объединены и соединены с выходом формирователя модуля, информационный вход которого соединен с объединенными входами четвертого одноканального аналогового коммутатора и инвертора, выход которого соединен со входом пятого одноканального аналогового коммутатора, первый и второй управляющие входы формирователя модуля соединены соответственно с управляющими входами четвертого и пятого одноканальных аналоговых коммутаторов.

Существенным отличием предлагаемого технического решения в различных вариантах его реализации является введение дополнительных элементов:

1) постоянного запоминающего устройства, формирователя модуля, нуль-органа, источника опорных напряжений, дешифратора, цифровых датчиков, первого - третьего одноканальных аналоговых коммутаторов, первого и второго аналоговых компараторов, таймера, регистра, числового компаратора, второго - пятого счетчиков, первого - третьего триггеров, элемента И-НЕ, первого - пятого элементов И, первого - четвертого элементов ИЛИ, первого - шестнадцатого одновибраторов;

2) постоянного запоминающего устройства, формирователя модуля, нуль-органа, источника опорных напряжений, дешифратора, цифровых датчиков, первого - третьего одноканальных аналоговых коммутаторов, таймера, регистра, первого и второго числовых компараторов, второго - пятого счетчиков, первого - третьего триггеров, элемента И-НЕ, первого - шестого элементов И, первого - пятого элементов ИЛИ, блока задания кода границы, первого - одиннадцатого одновибраторов.

К существенным отличиям предлагаемого технического решения также относятся организация его новой структуры и введение новых связей между элементами. Совокупность элементов и связей между ними обеспечивает достижение положительного эффекта - расширения функциональных возможностей за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

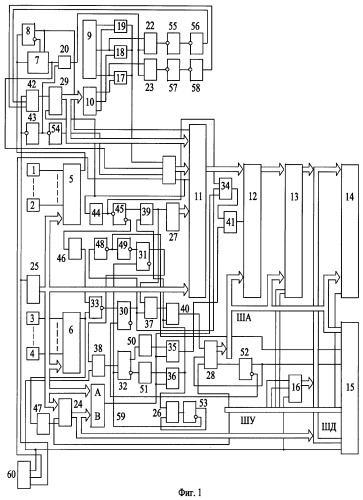

Схемы вариантов реализации регистратора параметров аварийных ситуаций в электрических сетях повышенной точности представлены: на фиг.1 - первого варианта, на фиг.2 - второго варианта; на фиг.3 приведен один из вариантов реализации формирователя модуля 7.

Схема первого варианта реализации регистратора (фиг.1) содержит группу аналоговых датчиков (АД) 1-2, группу цифровых датчиков (ЦД) 3-4, многоканальные первый аналоговый 5 (МАК) и второй цифровой 6 (МЦК) коммутаторы, формирователь 7 модуля (ФМ), нуль-орган (НО) 8, источник 9 опорных напряжений (ИОН), дешифратор 10, первое 11, второе 12 и третье 13 оперативные запоминающие устройства (ОЗУ), постоянное запоминающее устройство (ПЗУ) 14, микроконтроллер (МК) 15, таймер 16, первый - четвертый одноканальные аналоговые коммутаторы (OAK) 17-20, аналого-цифровой преобразователь (АЦП) 21, первый 22 и второй 23 аналоговые компараторы (АК), регистр 24, первый - пятый счетчики 25-29, первый -третий триггеры 30-32, элемент И-НЕ 33, первый - пятый элементы И 34-38, первый - четвертый элементы ИЛИ 39-42, первый - шестнадцатый одновибраторы

43-58, числовой компаратор (ЧК) 59, генератор 60 тактовых импульсов (ГТИ).

Выходы группы аналоговых датчиков 1-2 соединены с информационными входами первого многоканального коммутатора 5, выход которого соединен с объединенными информационными входами нуль-органа 8 и формирователя 7 модуля, выход которого через аналого-цифровой преобразователь 21 соединен с группой младших разрядов информационного входа первого оперативного запоминающего устройства 11, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства 12, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства 13, информационный выход которого соединен с шиной данных микроконтроллера 15, соединенной с информационным входом постоянного запоминающего устройства 14, вход управления записью которого подключен к шине управления микроконтроллера 15, соединенной также со входами управления состоянием выходов регистра 24, таймера 16, четвертого счетчика 28 и выходных регистров третьего оперативного запоминающего устройства 13, входами управления записью третьего оперативного запоминающего устройств 13 и постоянного запоминающего устройства 14, а также со входом захвата таймера 16, информационный выход которого соединен с шиной данных микроконтроллера 15, а тактовый вход объединен с тактовым входом микроконтроллера 15 и вторым входом пятого элемента И 38 и подключен к первому выходу генератора 60 тактовых импульсов, второй выход которого соединен с тактовым входом аналого-цифрового преобразователя 21, а третий выход соединен с объединенными первым входом четвертого элемента ИЛИ 42, инверсным входом первого одновибратора 43 и тактовым входом первого счетчика 25, информационный выход которого соединен с управляющими входами первого 5 и второго 6 многоканальных коммутаторов, с группой старших разрядов адресного входа первого оперативного запоминающего устройства 11, первым входом числового компаратора 59 и информационным входом регистра 24, выход которого соединен с шиной данных микроконтроллера 15 и вторым входом числового компаратора 59, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах числового компаратора 59) соединен с объединенными первыми входами первого 34, второго 35 и третьего 36 элементов И, выходы группы цифровых датчиков 3-4 соединены с информационными входами второго многоканального коммутатора 6, выход которого соединен со вторым входом элемента И-НЕ 33 и через пятый одновибратор 47 со входом управления записью регистра 24, выход элемента И-НЕ 33 соединен со входом установки единицы первого триггера 30, прямой выход которого соединен с объединенными вторыми входами первого 34 и четвертого 37 элементов И и входом шестого одновибратора 48, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера 15 и через седьмой одновибратор 49 - со входом установки единицы второго триггера 31, прямой выход которого через пятый элемент И 38 соединен с тактовым входом третьего триггера 32, выходы которого соединены соответственно через восьмой 50 и девятый 51 одновибраторы со вторыми входами второго 35 и третьего 36 элементов И, выход которого соединен с тактовым входом второго счетчика 26 и вторыми входами второго 40 и первого 39 элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика 27 и через четвертый элемент И 37 с первым входом второго элемента ИЛИ 40, выход которого соединен с тактовым входом четвертого счетчика 28, информационный выход которого соединен с адресной шиной микроконтроллера 15, а выход переноса соединен со входом десятого одновибратора 52, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера 15 и входом установки нуля четвертого счетчика 28, инверсный - со входом установки нуля первого триггера 30, выход переноса второго счетчика 26 соединен со входом одиннадцатого одновибратора 53, выходы которого соединены: прямой - со входом установки нуля второго счетчика 26, инверсный - со входами установки нуля второго 31 и третьего 32 триггеров, информационный выход третьего счетчика 27 соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства 11, выход первого одновибратора 43 соединен с объединенными управляющим входом четвертого одноканального аналогового коммутатора 20 и инверсным входом двенадцатого одновибратора 54, выход которого соединен со входом запуска аналого-цифрового преобразователя 21, выход окончания цикла преобразования которого соединен с объединенными входом управления записью первого оперативного запоминающего устройства 11, входом установки нуля пятого счетчика 29 и входом второго одновибратор 44, выход которого соединен с объединенными третьим входом первого элемента И 34 и инверсным входом третьего одновибратора 45, выходы которого соединены: прямой - с первым входом первого элемента ИЛИ 39, а инверсный - через четвертый одновибратор 46 с первым входом элемента И-НЕ 33, выход четвертого элемента ИЛИ 42 соединен с тактовым входом пятого счетчика 29, выход которого соединен с объединенными входом дешифратора 10 и группой средних разрядов информационного входа первого оперативного запоминающего устройства 11, старший разряд которого объединен с первым управляющим входом формирователя 7 модуля и подключен к прямому выходу нуль-органа 8, инверсный выход которого соединен со вторым управляющим входом формирователя 7 модуля, выход которого через четвертый одноканальный аналоговый коммутатор 20 соединен с объединенными вторыми входами первого 22 и второго 23 аналоговых компараторов, первые входы которых подключены соответственно ко второму и первому выходам источника 9 опорных напряжений, первый - третий выходы которого соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов 17-19, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя 21, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов 17 - 19 подключены соответственно к первому - третьему выходам дешифратора 10, выходы первого 22 и второго 23 аналоговых компараторов через последовательно соединенные попарно тринадцатый 55 и четырнадцатый 56, а также пятнадцатый 57 и шестнадцатый 58 одновибраторы связаны соответственно со вторым и третьим входами четвертого элемента ИЛИ 42, выход первого элемента И 34 через третий элемент ИЛИ 41 соединен со входом управления записью второго оперативного запоминающего устройства 12, адресная шина микроконтроллера 15 соединена с объединенными адресными входами второго 12 и третьего 13 оперативных запоминающих устройств и постоянного запоминающего устройства 14.

Схема второго варианта реализации регистратора (фиг.2) содержит группу аналоговых датчиков (АД) 1-2, группу цифровых датчиков (ЦД) 3-4, многоканальные первый аналоговый 5 (МАК) и второй цифровой 6 (МЦК) коммутаторы, формирователь 7 модуля (ФМ), нуль-орган (НО) 8, источник 9 опорных напряжений (ИОН), дешифратор 10, первое 11, второе 12 и третье 13 оперативные запоминающие устройства (ОЗУ), постоянное запоминающее устройство (ПЗУ) 14, микроконтроллер (МК) 15, таймер 16, первый - третий одноканальные аналоговые коммутаторы (OAK) 17-19, генератор 20 тактовых импульсов (ГТИ), аналого-цифровой преобразователь (АЦП) 21, регистр 22, первый - пятый счетчики 23 - 27, первый - пятый элементы ИЛИ 28-32, первый - четырнадцатый одновибраторы 33-46, первый - третий триггеры 47-49, элемент И-НЕ 50, первый - шестой элементы И 51-56, первый 57 и второй 58 числовые компараторы (ЧК), блок 59 задания кода границы (БЗКГ).

Выходы группы аналоговых датчиков 1-2 соединены с информационными входами первого многоканального коммутатора 5, выход которого соединен с объединенными информационными входами нуль-органа 8 и формирователя 7 модуля, выход которого через аналого-цифровой преобразователь 21 соединен с объединенными вторым входом второго числового компаратора 58 и группой младших разрядов информационного входа первого оперативного запоминающего устройства 11, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства 12, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства 13, информационный выход которого соединен с шиной данных микроконтроллера 15, соединенной с информационным входом постоянного запоминающего устройства 14, вход управления записью которого подключен к шине управления микроконтроллера 15, соединенной также со входами управления состоянием выходов регистра 22, таймера 16, четвертого счетчика 26 и выходных регистров третьего оперативного запоминающего устройства 13, входами управления записью третьего оперативного запоминающего устройств 13 и постоянного запоминающего устройства 14, а также со входом захвата таймера 16, информационный выход которого соединен с шиной данных микроконтроллера 15, а тактовый вход объединен с тактовым входом микроконтроллера 15 и вторым входом пятого элемента И 55 и подключен к первому выходу генератора 20 тактовых импульсов, второй выход которого соединен с тактовым входом аналого-цифрового преобразователя 21, а третий выход соединен с объединенными первым входом четвертого элемента ИЛИ 31 и тактовым входом первого счетчика 23, информационный выход которого соединен с управляющими входами первого 5 и второго 6 многоканальных коммутаторов, с группой старших разрядов адресного входа первого оперативного запоминающего устройства 11, первым входом первого числового компаратора 57 и информационным входом регистра 22, выход которого соединен с шиной данных микроконтроллера 15 и вторым входом первого числового компаратора 57, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах первого и второго числовых компараторов 57 и 58) соединен с объединенными первыми входами первого 51, второго 52 и третьего 53 элементов И, выходы группы цифровых датчиков 3-4 соединены с информационными входами второго многоканального коммутатора 6, выход которого соединен со вторым входом элемента И-НЕ 50 и через пятый одновибратор 37 со входом управления записью регистра 22, выход элемента И-НЕ 50 соединен со входом установки единицы первого триггера 44, прямой выход которого соединен с объединенными вторыми входами первого 51 и четвертого 54 элементов И и входом шестого одновибратора 38, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера 15 и через седьмой одновибратор 39 - со входом установки единицы второго триггера 48, прямой выход которого через пятый элемент И 55 соединен с тактовым входом третьего триггера 49, выходы которого соединены соответственно через восьмой 40 и девятый 41 одновибраторы со вторыми входами второго 52 и третьего 53 элементов И, выход которого соединен с тактовым входом второго счетчика 24 и вторыми входами второго 29 и первого 28 элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика 25 и через четвертый элемент И 54 с первым входом второго элемента ИЛИ 29, выход которого соединен с тактовым входом четвертого счетчика 26, информационный выход которого соединен с адресной шиной микроконтроллера 15, а выход переноса соединен со входом десятого одновибратора 42, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера 15 и входом установки нуля четвертого счетчика 26, инверсный - со входом установки нуля первого триггера 47, выход переноса второго счетчика 24 соединен со входом одиннадцатого одновибратора 43, выходы которого соединены: прямой - со входом установки нуля второго счетчика 24, инверсный - со входами установки нуля второго 48 и третьего 49 триггеров, информационный выход третьего счетчика 25 соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства 11, выход четвертого элемента ИЛИ 31 соединен с объединенными тактовым входом пятого счетчика 27 и инверсным входом первого одновибратора 33, выход которого соединен со входом запуска аналого-цифрового преобразователя 21, выход окончания цикла преобразования которого соединен с первым входом шестого элемента И 56, выход которого соединен с объединенными входом управления записью первого оперативного запоминающего устройства 11, входом установки нуля пятого счетчика 27 и входом второго одновибратор 34, выход которого соединен с объединенными третьим входом первого элемента И 51 и инверсным входом третьего одновибратора 35, выходы которого соединены: прямой - с объединенными первым входом первого элемента ИЛИ 28 и входом установки нуля аналого-цифрового преобразователя 21, а инверсный - через четвертый одновибратор 36 с первым входом элемента И-НЕ 50, выход четвертого элемента ИЛИ 31 соединен с тактовым входом пятого счетчика 27, выход которого соединен с объединенными входом дешифратора 10 и группой средних разрядов информационного входа первого оперативного запоминающего устройства 11, старший разряд которого объединен с первым управляющим входом формирователя 7 модуля и подключен к прямому выходу нуль-органа 8, инверсный выход которого соединен со вторым управляющим входом формирователя 7 модуля, первый - третий выходы источника 9 опорных напряжений соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов 17-19, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя 21, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов 17-19 подключены соответственно к первому - третьему выходам дешифратора 10, выход блока 59 задания кода границы соединен с первым входом второго числового компаратора 58, выходы которого соединены: «А<В» - через двенадцатый одновибратор 44 со вторым входом четвертого элемента ИЛИ 31, «А=В» и «А>В» - со вторым и третьим входами пятого элемента ИЛИ 32, первый вход которого через последовательно соединенные тринадцатый 45 и четырнадцатый 46 одновибраторы подключен к третьему выходу дешифратора 10, а выход пятого элемента ИЛИ 32 соединен со вторым входом шестого элемента И 56, выход первого элемента И 34 через третий элемент ИЛИ 30 соединен со входом управления записью второго оперативного запоминающего устройства 12, адресная шина микроконтроллера 15 соединена с объединенными адресными входами второго 12 и третьего 13 оперативных запоминающих устройств и постоянного запоминающего устройства 14.

Схема формировател