Устройство поиска широкополосных сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может найти применение при построении систем радиосвязи, радионавигации, управления, использующих широкополосные сигналы. Технический результат - повышение стабильности помехоустойчивого поиска широкополосных сигналов (ШПС) по задержке, исключающее вероятность синхронизации устройств поиска на структурные помехи. Для этого в устройство поиска широкополосных сигналов, содержащее линейную часть (1), согласованный фильтр (2), предварительный фильтр (3), линия задержки (4), аттенюаторы (51-5n), фазовращатели (61-6n), сумматор (7), детектор (8), блок сравнения с порогом (9), генератор тактовых импульсов (10), блок управления переключением каналов (11), логический элемент «И» (12), компаратор (13) введен компаратор (13), первый вход которого является входом установки порогового напряжения VK, a n остальных его входов соединены с n входами сумматора (7), при этом выход компаратора (13) соединен со вторым входом логического элемента «И» (12). 3 ил.

Реферат

Предлагаемое устройство относится к области радиотехники и может найти применение при построении систем радиосвязи, радионавигации, управления, использующих широкополосные сигналы.

Известны устройства поиска широкополосных сигналов по а.с. №1003372, Н04L 7/02, 1981 г.; №809619 Н04L 7/02, 1979 г., которым присущ общий недостаток, заключающийся в низкой помехоустойчивости поиска широкополосных сигналов (ШПС) по задержке, а именно в большой вероятности синхронизации устройств поиска на структурные помехи.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в патенте РФ №2223606, Н04В 1/10, H04L 7/02, принятое за прототип.

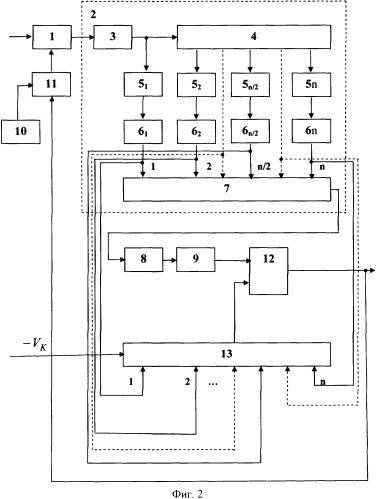

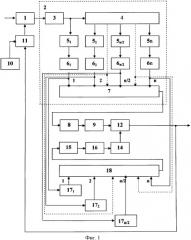

На фиг.1 изображена блок-схема устройства-прототипа, где обозначено:

1 - линейная часть;

2 - согласованный фильтр;

3 - предварительный фильтр;

4 - линия задержки;

51-5n - с первого по n-й аттенюаторы;

61-6n - с первого по n-й фазовращатели;

7, 18 - первый и второй сумматоры;

8, 15 -первый и второй детекторы;

9, 16 -первый и второй блоки сравнения с порогом;

10 -генератор тактовых импульсов;

11 - блок управления переключением каналов;

12 - элемент «И»;

14 -элемент «НЕ»;

171-17n/2 - с первого по n/2-й инверторы.

Устройство-прототип содержит последовательно соединенные линейную часть 1 и согласованный фильтр 2, состоящий из последовательно соединенных предварительного фильтра 3 и линии задержки 4, (n-1) выходов которой соединены с входами соответственно со второго по n-й аттенюаторов 52-5n, выходы которых соединены с входами соответственно со второго по n-й фазовращателей 62-6n, выходы которых соединены с входами соответственно со второго по n-й сумматора 7. При этом выход предварительного фильтра 3 соединен с входом первого аттенюатора 51, выход которого через первый фазовращатель 61 соединен с первым входом сумматора 7, выход которого является выходом согласованного фильтра 2 и соединен с входом первого детектора 8, выход которого через первый блок сравнения с порогом 9 соединен с первым входом элемента «И» 12, выход которого является выходом устройства и соединен с управляющим входом блока управления переключением каналов 11, выход которого соединен со вторым входом линейной части 1, первый вход которой является входом устройства. Причем выход генератора тактовых импульсов 10 соединен с синхронизирующим входом блока управления переключением каналов 11. Кроме того, выходы с первого по n/2-й инверторов 171-17n/2 соединены соответственно с первой группой n/2 входов второго сумматора 18, входы с первого по n/2-й инверторов 171-17n/2 соединены с n/2 входами первой группы первого сумматора 7, а n/2 входов второй группы второго сумматора 18 соединены соответственно с n/2 входами второй группы первого сумматора 7. Выход второго сумматора 18 через последовательно соединенные второй детектор 15, второй блок сравнения с порогом 16 и элемент «НЕ» 14 соединен со вторым входом элемента «И» 12. При этом вход предварительного фильтра 3 является входом согласованного фильтра 2.

Устройство-прототип работает следующим образом. На первый вход линейной части 1 поступает сигнал, структурная помеха или их смесь. С выхода линейной части 1 сигнал поступает на вход согласованного фильтра 2, где через предварительный фильтр 3 поступает на вход линии задержки 4. С выхода предварительного фильтра 3 и с n выходов линии задержки 4 через соответствующие с первого по n-й аттенюаторы 51-5n сигнал поступает на входы соответствующих с первого по n-й фазовращатели 61-6n и далее на соответствующие входы первого сумматора 7. Параметры линии задержки 4, аттенюаторов 51-5n и фазовращателей 61-6n выбираются таким образом, чтобы на выходе первого сумматора 7, являющимся также и выходом согласованного фильтра 2, и на входе первого детектора 8 элементы сигнала складывались в фазе и давали значение функции автокорреляции полезного сигнала, а на выходе первого детектора 8 при этом будет значение огибающей функции автокорреляции полезного сигнала. Превышение порога в первом блоке сравнения с порогом 9 приводит к тому, что на второй вход элемента «И» 12 поступит логическая единица.

Одновременно с n входов первого сумматора 7 сигнал поступает на соответствующие n входов второго сумматора 18, причем n/2 входов первой группы первого сумматора 7 через n/2 инверторов 171-17n/2 соединены с первой группой n/2 соответствующих входов второго сумматора 18. Это приводит к тому, что в момент времени, когда на выходе первого сумматора 7 все n элементов сигнала сложатся синфазно, то и на выходе второго сумматора 18 n/2 элементов сложатся синфазно, а n/2 остальных элементов сигнала сложатся с противоположной фазой, т.е. значение автокорреляционной функции сигнала на выходе второго сумматора 18 будет близко к нулю. Соответственно, не будет превышен порог в блоке 16 и с выхода элемента «НЕ» 14 на первый вход элемента «И» 12 поступит логическая единица. Следовательно, с выхода элемента «И» 12 выйдет логическая единица и поступит на управляющий вход блока управления переключением каналов 11, что приведет к фиксации данного канала, так как выход логической единицы с выхода элемента «И» 12 означает, что сигнал найден и поиск закончен.

Если на второй вход линейной части 1 поступит смесь полезного сигнала и мощной структурной помехи, то, как и в случае только с полезным сигналом, превышение порога суммой огибающих функций автокорреляции сигнала и функции взаимной корреляции помехи в блоке 9 приведет к поступлению на второй вход элемента «И» 12 логической единицы. Вероятность того, что в этот же момент значение функции взаимной корреляции не превысит порог в блоке 16, достаточно мала. То есть с выхода блока 14 на первый вход элемента «И» 12 поступит логический нуль. Следовательно, с выхода элемента «И» 12 на управляющий вход блока управления переключением каналов 11 поступит логический нуль, означающий, что сигнал не найден, переключение каналов может быть продолжено, поиск полезного сигнала будет продолжен.

Если на второй вход линейной части 1 поступит мощная структурная помеха, то вероятность того, что в момент отсчета будет превышен порог как в блоке 9, так и в блоке 16, достаточно велика. Это значит, что на первый вход элемента «И» 12 поступит логический нуль, а на второй вход элемента «И» 12 поступит логическая единица. С выхода элемента «И» 12 на управляющий вход блока управления переключением каналов 11 поступит логический нуль и поиск сигнала будет продолжен на других каналах.

Недостатком устройства-прототипа является нестабильность помехоустойчивого поиска широкополосных сигналов (ШПС) по задержке, а именно, заранее подключенные выводы линии задержки часто не соответствуют тем выходам, где требуется произвести инвертирование принятого сигнала, что создает вероятность синхронизации устройств поиска на структурные помехи.

Для устранения указанного недостатка в устройство поиска широкополосных сигналов, содержащее последовательно соединенные линейную часть и согласованный фильтр, состоящий из последовательно соединенных предварительного фильтра и линии задержки, выходы со 2-го по n-й которой соединены с входами соответствующих со 2-го по n-й аттенюаторов, выходы которых соединены с входами соответствующих со 2-го по n-й фазовращателей, при этом выход предварительного фильтра через 1-й аттенюатор соединен с входом 1-го фазовращателя, выходы всех фазовращателей соединены с соответствующими входами сумматора, выход которого является выходом согласованного фильтра и через последовательно соединенные детектор и блок сравнения с порогом соединен с первым входом логического элемента «И», выход которого является выходом устройства и соединен с управляющим входом блока управления переключением каналов, синхронизирующий вход которого соединен с выходом генератора тактовых импульсов, причем выход блока управления переключением каналов подсоединен ко второму входу линейной части, первый вход которой является входом устройства, согласно изобретению введен компаратор, первый вход которого является входом установки порогового напряжения VK, а n остальных его входов соединены с n входами сумматора 7, при этом выход компаратора соединен со вторым входом логического элемента «И».

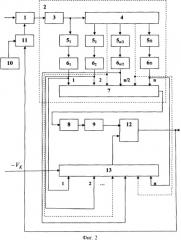

На фиг.2 изображена блок-схема предлагаемого устройства поиска широкополосного сигнала, где использованы следующие обозначения:

1 - линейная часть;

2 - согласованный фильтр;

3 - предварительный фильтр;

4 - линия задержки;

51-5n - с 1-го по n-й аттенюаторы;

61-6n - с 1-го по n-й фазовращатели;

7 - сумматор;

8 - детектор;

9 - блок сравнения с порогом;

10 - генератор тактовых импульсов;

11 - блок управления переключением каналов;

12 - логический элемент «И»;

13 - компаратор.

Предлагаемое устройство содержит последовательно соединенные линейную часть 1 и согласованный фильтр 2, состоящий из последовательно соединенных предварительного фильтра 3 и линии задержки 4, выходы которой со 2-го по n-й соединены с входами соответствующих аттенюаторов 52-5n, выходы которых соединены с входами соответствующих фазовращателей 62-6n, при этом выход предварительного фильтра 3 через первый аттенюатор 51 соединен с входом первого фазовращателя 61. Выходы n фазовращателей 61-6n подсоединены к соответствующим входам сумматора 7, выход которого является выходом согласованного фильтра 2 и через последовательно соединенные детектор 8 и блок сравнения с порогом 9 соединен с первым входом логического элемента «И» 12, выход которого является выходом устройства и соединен с управляющим входом блока управления переключением каналов 11, синхронизирующий вход которого соединен с выходом генератора тактовых импульсов 10, причем выход блока управления переключением каналов 11 подсоединен ко второму входу линейной части 1, первый вход которой является входом устройства. Второй вход элемента «И» 12 соединен с выходом компаратора 13, первый вход которого является входом установки порогового напряжения VK, а n остальных его входов соединены с n входами сумматора 7.

Предлагаемое устройство работает следующим образом.

На первый вход линейной части 1, являющийся входом устройства, поступает сигнал, структурная помеха или их смесь. Поступление положительного потенциала от блока управления переключением каналов 11 на второй вход линейной части 1 означает начало работы устройства. С выхода линейной части 1 сигнал поступает на вход согласованного фильтра 2, где через предварительный фильтр 3 поступает на вход линии задержки 4. С выхода предварительного фильтра 3 и с n выходов линии задержки 4 через соответствующие с первого по n-й аттенюаторы 51-5n сигнал поступает на входы соответствующих с первого по n-й фазовращатели 61-6n и далее на соответствующие входы первого сумматора 7.

Параметры линии задержки 4, n аттенюаторов 5 и n фазовращателей 6 выбираются таким образом, чтобы на выходе сумматора 7, являющемся также и выходом блока 2, соединенным с входом детектора 8, элементы сигнала складываются в фазе и дают значение функции автокорреляции полезного сигнала, а на выходе детектора 8 будет выделяться напряжение огибающей функции автокорреляции полезного сигнала. Превышение порога в блоке сравнения с порогом 9 приводит к тому, что на первый вход элемента «И» 12 поступает логическая единица.

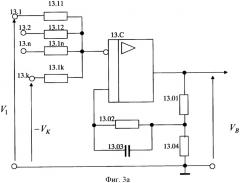

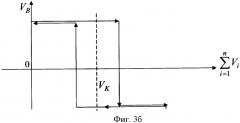

Одновременно с выходов n фазовращателей 61-6n сигнал поступает на соответствующие n входов компаратора 13, схема которого приведена на фиг.3а, где обозначено:

входы 1, 2, …, n компаратора 13 (фиг.2) являются соответственно входами 13.1, 13.2, …, 13.n;

вход 13.k является входом установки порога;

13.С - операционный усилитель;

13.01, 13.04 - резисторы делителя;

13.03 - конденсатор;

13.02, 13.1k, 13.11, 13.2, …, 13.n - резисторы.

Компаратор 13 содержит операционный усилитель 13.С, к инвертирующему входу которого через соответствующие резисторы 13.11, 13.12, 13.1n, 13.1k подсоединены входы компаратора 13.1, 13.2, 13.n, 13.k. Между выходом операционного усилителя 13.С и общей шиной включен делитель на резисторах 13.01 13.04, средняя точка которого через параллельно соединенные резистор 13.02 и конденсатор 13.03 подключена к неинвертирующему входу операционного усилителя 13.С.

Работает компаратор 13 следующим образом.

Устанавливаемое пороговое напряжение VK поступает на вход 13.k. С делителя на резисторах 13.01 13.04 напряжение через параллельно соединенные резистор 13.02 и конденсатор 13.03 подается на неинвертирующий вход операционного усилителя 13.С.

Сигналы, подаваемые на входы 13.11, 13.2, …, 13.n, складываются в соответствии с формулой:

.

Пороговое напряжение VK вычитается, как показано на фиг.3б. В результате половина сигналов Vi, будет складываться с одним знаком, а половина - с противоположным. Причем знак суммируемых напряжений определяется формой, расширяющей спектр последовательности, а не устанавливается заранее, как в прототипе. При превышении значения порога VK суммарным напряжением . на выходе компаратора 13 устанавливается низкий потенциал (логический «нуль»), как показано на фиг.3б, указывая, что сигнал не найден.

Если установленный порог VK не превышен, то это означает, что сигнал найден. При этом на выходе компаратора 13 устанавливается высокий потенциал (логическая «единица»). Для обеспечения надежности работы компаратора 13 элементы рассчитываются таким образом, чтобы подавлять пульсации сигнала, что отражено характеристикой, приведенной на фиг.3б.

Если установленный порог VK не превышен, то это означает, что сигнал найден. При этом на выходе компаратора 13 устанавливается высокий потенциал (логическая «единица»). Также высокий потенциал появляется на выходе схемы «И» 12, выход которой подключен к управляющему входу блока управления переключением каналов 11. В результате на выходе блока управления переключением каналов 11 устанавливается низкий потенциал, означающий окончание поиска сигнала. В случае низкого потенциала на выходе компаратора 13 и соответственно на выходе схемы «И» 12 и управляющем входе блока управления переключением каналов 11 устанавливается высокий потенциал, означающий продолжение поиска сигнала на новых радиоданных. При поступлении положительного перепада импульса от тактового генератора 10 на синхронизирующий вход блока управления переключением каналов 11 возобновляется поиск сигнала на новых радиоданных. Для обеспечения надежности работы компаратора 13 элементы рассчитываются таким образом, чтобы подавлять пульсации сигнала, что отражено характеристикой, приведенной на фиг.3б.

Сигнал с выхода компаратора 13 поступает на второй вход элемента «И» 12. В случае поступления высокого потенциала на управляющий вход блока управления переключением каналов 11 поиск заканчивается, означая, что сигнал найден. Если потенциал на управляющем входе блока управления переключением каналов 11 будет низким, то это означает, что сигнал не найден и подается сигнал на переключение каналов на второй вход линейной части 1. На синхронизирующий вход блока управления переключением каналов 11 подается сигнал от генератора тактовых импульсов 10, обеспечивающий тактирование работы устройства поиска широкополосных сигналов.

Блок 10 может быть выполнен на основе различных типов генераторов, например на основе кварцевого генератора, приведенного в патенте RU 2311727, Н03В 5/36.

Устройство поиска широкополосных сигналов, содержащее последовательно соединенные линейную часть и согласованный фильтр, состоящий из последовательно соединенных предварительного фильтра и линии задержки, выходы со 2-го по n-й которой соединены с входами соответствующих со 2-го по n-й аттенюаторов, выходы которых соединены с входами соответствующих со 2-го по n-й фазовращателей, при этом выход предварительного фильтра через 1-й аттенюатор соединен с входом 1-го фазовращателя, выходы всех фазовращателей соединены с соответствующими входами сумматора, выход которого является выходом согласованного фильтра и через последовательно соединенные детектор и блок сравнения с порогом соединен с первым входом логического элемента «И», выход которого является выходом устройства и соединен с управляющим входом блока управления переключением каналов, синхронизирующий вход которого соединен с выходом генератора тактовых импульсов, причем выход блока управления переключением каналов подсоединен ко второму входу линейной части, первый вход которой является входом устройства, отличающееся тем, что введен компаратор, первый вход которого является входом установки порогового напряжения VK, a n остальных его входов соединены с n входами сумматора, при этом выход компаратора соединен со вторым входом логического элемента «И».