Резервированный счетчик для формирования меток времени

Иллюстрации

Показать всеИспользование: в области вычислительной и импульсной техники при построении высоконадежных резервированных систем для счета и обработки цифровой информации. Технический результат заключается в упрощении схемной реализации устройства. Устройство состоит из m каналов, каждый из которых содержит блок управления, n-разрядный счетчик, блок из n мажоритарных элементов, мажоритарный элемент, одновибратор, мультиплексор, цифровой компаратор, первый, второй и m-й регистр сдвига, управляемый счетчик, программируемое запоминающее устройство, первый и второй дешифраторы. Возникающий в процессе функционирования случайный сбой в любом из каналов резервированного счетчика будет парирован в течение времени Т (периода следования входных импульсов) путем восстановления в каждом из n-разрядных счетчиков (5) правильной информации. За счет сокращения числа элементов, обеспечивающих межканальные связи, и объема преобразуемой информации происходит значительное упрощение устройства. 1 з.п. ф-лы, 2 ил.

Реферат

Предлагаемое изобретение относится к вычислительной и импульсной технике и может быть использовано в системах, использующих программно-временные устройства.

Известен резервированный счетчик для формирования меток времени, описание которого приведено в [1]. Устройство содержит 3 пары входных шин и 3 канала, каждый из которых содержит разряды, включающие триггер, два элемента И и мажоритарный элемент.

Это устройство позволяет выдавать истинную информацию (формировать метки времени в заданное время) при наличии сбоев меньше, чем мажоритарное число М, [М=(m+1):2] в каждом резервированном разряде счетчика. Но с накоплением сбоев их число в одном разряде может превысить число М, вследствие чего информация в счетчике станет ложной, что недопустимо. Сам счетчик не проводит восстановление информации в разряде, потерпевшем сбой. Вероятность сбоя резервированного счетчика (а, следовательно, и неправильного формирования меток времени) значительно возрастает, если время работы этого счетчика достаточно велико.

Наиболее близким техническим решением к предлагаемому является резервированный счетчик для формирования меток времени [2], содержащий m каналов, а в каждом канале n-разрядный счетчик, блок из n мажоритарных элементов и последовательно соединенные мажоритарный элемент и одновибратор, выход которого соединен с входом С n-разрядного счетчика, вход D параллельной записи которого подключен к выходной шине блока из n мажоритарных элементов.

Это устройство может самостоятельно восстанавливать информацию, потерянную при наличии сбоев, количество которых меньше, чем мажоритарное число М [М=(m+1):2] в каждом разряде счетчика. Это позволяет формировать метки времени в заданное время несмотря на отдельные сбои счетчиков.

Недостаток этого устройства состоит в том, что оно имеет большое число межканальных связей, и, как следствие, каждая такая связь требует установки дополнительного согласующего устройства (например, оптрона), так как каждый канал запитывается источником питания, гальванически несвязанным во многих случаях с источником питания других каналов. Кроме того, современные цифровые схемы реализуются на базе программируемых логических интегральных схем (ПЛИС) с высокой степенью интеграции, позволяющей в одной ПЛИС реализовывать логически сложные схемы. Большое число межканальных связей требует большого числа выводов ПЛИС, что приводит к необходимости использования двух и более ПЛИС или более дорогостоящей ПЛИС с большим количеством выводов. Кроме того, недостаток этого устройства состоит в том, что формирование меток времени производится путем преобразования кодовой информации всех разрядов счетчика, что требует большого количества элементов, участвующих в преобразовании, а это усложняет устройство.

Задача изобретения - упрощение устройства за счет уменьшения числа межканальных связей и снижения объема преобразуемой информации.

Эта задача достигается тем, что в резервированный счетчик для формирования меток времени, содержащий m каналов, а в каждом канале n-разрядный счетчик, блок из n мажоритарных элементов и последовательно соединенные мажоритарный элемент и одновибратор, выход которого соединен с входом С n-разрядного счетчика, вход D параллельной записи которого подключен к выходной шине блока из n мажоритарных элементов, в каждый канал введены мультиплексор, блок управления, первый, второй и m - й регистры сдвига, цифровой компаратор, управляемый счетчик, программируемое запоминающее устройство, первый и второй дешифраторы, при этом в каждом канале выход одновибратора соединен с первым входом управляемого счетчика и входом блока управления, первый и второй выходы которого соединены с входами РЕ разрешения параллельной записи n-разрядного счетчика и первого регистра сдвига соответственно, третий выход блока управления соединен с входом С первого регистра сдвига и входами С соответствующих регистров сдвига других каналов, входы D которых соединены с выходом первого регистра сдвига, входы D параллельной записи которого соединены с выходной шиной n-разрядного счетчика, входной шиной В цифрового компаратора и первой входной шиной блока из n мажоритарных элементов, вторая и m-я входные шины которого подключены к выходным шинам соответственно второго и m-го регистров сдвига, входная шина А цифрового компаратора соединена с шиной данных программируемого запоминающего устройства, шина адреса которого соединена с выходной шиной управляемого счетчика и входной шиной первого и второго дешифраторов, вход управления которых соединен с выходом А=В цифрового компаратора и вторым входом управляемого счетчика, выходная шина первого дешифратора соединена с выходной шиной устройства, выходная шина второго дешифратора соединена с входной шиной мультиплексора, входы которого подключены к соответствующим входам устройства, выход мультиплексора каждого канала соединен с соответствующими входами мажоритарного элемента всех каналов.

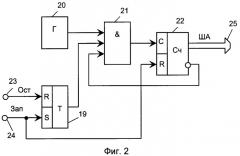

Управляемый счетчик содержит триггер, генератор, элемент И, счетчик, первый и второй входы управления, при этом выход генератора соединен с первым входом элемента И, второй вход которого соединен с выходом триггера, вход S которого соединен с первым входом управления и входом R счетчика, третий вход элемента И соединен с инверсным выходом последнего разряда счетчика, вход С которого соединен с выходом элемента И, вход R триггера соединен с вторым входом управления, выходы каждого разряда счетчика соединены с выходной шиной управляемого счетчика.

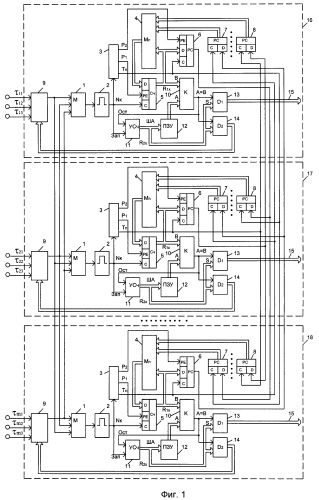

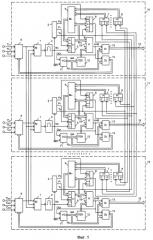

На фиг.1 приведена блок-схема резервированного счетчика для формирования меток времени, где 1 - мажоритарный элемент, 2 - одновибратор, 3 - блок управления, 4 - блок из n мажоритарных элементов, 5 - n-разрядный счетчик, 6, 7 и 8 - первый, второй и m - и регистры сдвига, 9 - мультиплексор, 10 - цифровой компаратор, 11 - управляемый счетчик, 12 - программируемое запоминающее устройство, 13 - первый дешифратор, 14 - второй дешифратор, 15 - выходная шина, 16 - первый канал, 17 - второй канал, 18 - m-й канал.

На фиг.2 приведена блок - схема управляемого счетчика, где 19 - триггер, 20 - генератор, 21 - элемент И, 22 - счетчик, 23 - первый вход управления, 24 - второй вход управления, 25 - выходная шина управляемого счетчика.

Резервированный счетчик для формирования меток времени содержит m каналов, каждый из которых включает мажоритарный элемент 1, одновибратор 2, блок управления 3, n-разрядный счетчик 5, блок из n мажоритарных элементов 4, первый 6, второй 7 и m-й 8 регистры сдвига, мультиплексор 9, цифровой компаратор 10, управляемый счетчик 11, программируемое запоминающее устройство 12, первый дешифратор 13, второй дешифратор 14, выходную шина 15. В каждом канале соединены последовательно мажоритарный элемент 1 и одновибратор 2, выход которого соединен с входом блока управления 3, первым входом управляемого счетчика 11 и входом С n-разрядного счетчика 5, вход D параллельной записи которого подключен к выходной шине блока из n мажоритарных элементов 4. Выход мультиплексора 9 каждого канала соединен с соответствующими входами мажоритарного элемента всех каналов. Первый и второй выходы блока управления 3 соединены с входами РЕ разрешения параллельной записи n-разрядного счетчика 5 и первого регистра сдвига 6 соответственно, третий выход блока управления 3 соединен с входом С первого регистра сдвига 6 и входами С соответствующих регистров сдвига других каналов, входы D которых соединены с выходом первого регистра сдвига 6, входы D параллельной записи которого соединены с выходной шиной n-разрядного счетчика 5, входной шиной В цифрового компаратора 10 и первой входной шиной блока из n мажоритарных элементов 4, вторая и m-я входные шины которого подключены к выходным шинам соответственно второго 7 и m-го 8 регистров сдвига. Входная шина А цифрового компаратора 10 соединена с шиной данных программируемого запоминающего устройства 12, шина адреса которого соединена с выходной шиной управляемого счетчика 11 и входной шиной первого 13 и второго 14 дешифраторов, вход управления которых соединен с выходом А=В цифрового компаратора 10 и вторым входом управляемого счетчика 11. Выходная шина первого дешифратора 13 соединена с выходной шиной устройства 15, выходная шина второго дешифратора 14 соединена с входной шиной мультиплексора 9, входы которого подключены к соответствующим входам устройства.

Управляемый счетчик фиг.2 содержит триггер 19, генератор 20, элемент И 21, счетчик 22, первый вход управления 23, второй вход управления 24 и выходную шину управляемого счетчика 25. Выход генератора 20 соединен с первым входом элемента И 21, второй вход которого соединен с выходом триггера 19, вход S которого соединен с первым входом управления 23 и входом R счетчика 22. Третий вход элемента И 21 соединен с инверсным выходом последнего разряда счетчика 22, вход С которого соединен с выходом элемента И 21. Вход R триггера 19 соединен со вторым входом управления 24, выходы каждого разряда счетчика 22 соединены с выходной шиной управляемого счетчика 25.

Резервированный счетчик работает следующим образом (для простоты примем m=3 и что все n - разрядные счетчики 6 находятся в нулевом состоянии). Пусть на входы мультиплексора 9 канала q (q=1, 2, ...m) поступают входные последовательности импульсов τqi(i=1, 2, 3) с интервалами τq1, τq2 и τq3. Будем предполагать, что τq1=τ1=1 час, τq2=τ2=1 мин, τq3=τ3=1 с, а импульсы τqi поступают синхронно. Предполагаем также, что при поступлении импульса с выхода одновибратора 2 на вход блока управления 3 на его выходах формируются следующие сигналы: на первом выходе формируется импульс Р1, разрешающий параллельную запись в n-разрядный счетчик 5 кодовой информации выходной шины блока из n мажоритарных элементов 4, на втором выходе формируется импульс P2, разрешающий параллельную запись в первый регистр сдвига 6 кодовой информации выходной шины n-разрядного счетчика 5, на третьем выходе формируется последовательность из n импульсов Tn частотой следования Т0. Будем считать, что первым по времени формируется импульс P2, далее формируется последовательность импульсов Tn и затем формируется импульс P1. Будем также предполагать, что период следования входных импульсов Т>n Т0, а за время Т формируются все сигналы с выходов блока управления 3: импульсы P1, P2 и последовательность Tn.

Пусть требуется формировать I=5 меток времени Mj, при этом временные интервалы Tj(j=1, 2, ...5) между соседними метками соответственно равны:

где коэффициенты pji изменяются в пределах от нуля до 59 (в рассматриваем случае отношение τi/τ(i+1)=К=60). Пусть для простоты р11=p21=р31=p41=p51=2, p12=p22=p32=p42=p52=8, p13=p23=р33=p43=p53=12.

Пусть на входы каждого канала резервированного счетчика для формирования меток времени поступают импульсы τqi, синхронизированные по времени. В этом случае при появлении очередных входных импульсов на выходе мажоритарного элемента 1 каждого канала формируется сигнал, поступающий на вход одновибратора 2, который формирует импульс на входе С n-разрядного счетчика 5, на первом входе управляемого счетчика 11 и входе блока управления 3. Этот импульс суммируется с содержимым n-разрядного счетчика 5, разрешает суммирование импульсов с генератора 20 счетчиком 22 (фиг.2) и осуществляет запуск программы формирования сигналов P1, Р2 и Tn блоком управления 3. Рассмотрим вначале прохождение выходных сигналов блока управления 3. Вырабатываемый первым по времени сигнал Р2 осуществляет параллельную запись в первый регистр сдвига 6 кодовой информации выходной шины n-разрядного счетчика 5. Формируемая далее последовательность Tn из n импульсов поступает на вход С первого регистра сдвига 6 и входы С соответствующих регистров сдвига других каналов и осуществляет передачу кодовой информации с выхода первого регистра сдвига 6 на входы D соответствующих регистров сдвига других каналов. Таким образом, после прохождения n-го импульса последовательности Tn в каждом канале кодовое состояние второго 7 и m-го 8 регистров сдвига будет соответствовать кодовому состоянию n-разрядного счетчика 5 других каналов. В результате на соответствующих входах блока из n мажоритарных элементов 4 каждого канала образуется кодовая информация n-разрядных счетчиков 5 всех каналов (считаем, что блок из n мажоритарных элементов 4 содержит n мажоритарных элементов и входы d-го мажоритарного элемента каждой входной шины, d=1, 2 (n соединены соответственно с выходами d-го разряда n-разрядного счетчика 5 и соответствующих регистров сдвига этого канала).

На каждом выходе d выходной шины блока из n мажоритарных элементов 4 будет сформировано состояние, соответствующее состоянию большинства d-x разрядов n-разрядных счетчиков 5 всех каналов. Кодовое состояние выходной шины блока из n мажоритарных элементов 4 каждого канала будет соответствовать истинному значению, если по каким-либо причинам число сбоев в любых d-x разрядах не превышает число M [M=(m+1):2]. Формируемый далее блоком управления 3 на втором выходе импульс P1 осуществит запись в n-разрядный счетчик 5 всех каналов кодового состояния блока из n мажоритарных элементов 4. Таким образом, если по каким-либо причинам информация в n-разрядном счетчике 5 какого-либо канала оказалась недостоверной, она будет восстановлена выходным импульсом P1 в момент записи в n-разрядный счетчик 5 всех каналов кодового состояния блока из n мажоритарных элементов 4.

Выходной импульс NK одновибратора 2 поступает на первый вход 24 управляемого счетчика 11 (фиг.2), устанавливает триггер 19 в единичное состояние, а счетчик 22 в нулевое состояние. В этом случае на втором и третьем входах элемента И 21 будут высокие уровни и выходные сигналы генератора 20 будут проходить с выхода элемента И 21 на вход С счетчика 22. Счетчик 22 будет считать импульсы генератора 20 до момента установки последнего разряда счетчика 22 в единичное состояние. В этом случае с инверсного выхода последнего разряда счетчика 22 на третий вход элемента И 21 будет поступать низкий уровень и элемент И 21 блокирует прохождение импульсов генератора 20. В таком состоянии управляемый счетчик будет находиться до очередного поступления выходного импульса NK одновибратора 2. Остановка счета импульсов генератора 20 происходит также в случае поступления на второй вход 23 управляемого счетчика 11 сигнала с выхода А=В цифрового компаратора 10. Этот сигнал устанавливает триггер 19 в нулевое состояние и на его выходе формируется низкий уровень. Будем считать, что генератор 20 формирует импульсы частотой ТГ, причем, I ТГ<τ3 (τ3 - минимальный период следования входных импульсов).

Пусть исходное состояние n-разрядного счетчика 5 R10 и управляемого счетчика 11 R20, причем R10=R20=0. В дальнейшем число, записанное в n-разрядный счетчик 5, будем обозначать R1X, а число, записанное в управляемый счетчик 11, будем обозначать R2X. Цифровой сигнал R1X формируется путем последовательного суммирования pji импульсов тех последовательностей, которые определяют время Tj, причем в интервале времени Tj последовательно будем суммировать вначале pj1 импульсов с максимальным периодом следования τ1, затем pj2 импульсов с меньшим периодом следования τ2 и в конце pjn импульсов с наименьшими периодом следования τn, при этом метки времени Mj будем формировать в моменты времени tr(r=1, 2, ...m), когда цифровой сигнал С равен значению

Пусть при R2X=1 программируемое запоминающее устройство (ПЗУ) 12 подключает к своему выходу ячейку с адресом R2X=1, содержимое которой А=p11=2, а второй дешифратор 14 при R2X=0 формирует на своем выходе D такой код, который устанавливает мультиплексор 9 в состояние, при котором на его выход подключается последовательность импульсов τq1. Считаем, что первый 13 и второй 14 дешифраторы осуществляют преобразование той информации на входной шине, которая имела место на момент поступления на вход управления сигнала с выхода А=В цифрового компаратора 10, и не изменяют свой выходной сигнал до очередного поступления сигнала А=В. После поступления первого импульса с выхода одновибратора 2 управляемый счетчик 11 будет изменять свой выходной сигнал R2X от нулевого значения до максимального, при котором состояние последнего разряда счетчика 22 не станет единичным. В этом случае на шине А компаратора будут появляться все числовые значения, формируемые ПЗУ, но ни одно из этих значений не будет равно текущему значению цифровой информации n-разрядного счетчика 5 R1X и до момента изменения информации на выходе n-разрядного счетчика 5 не может быть выработан сигнал А=В. Таким образом, до момента появления информации R1X=p11=2 на выходе n-разрядного счетчика 5 будет производиться счет импульсов с выхода одновибратора 2 n-разрядным счетчиком 5, а выходная информация первого 13 и второго 14 остается неизменной. В то же время при каждом поступлении импульса с выхода одновибратора 2 происходит восстановление правильной информации в каждом n-разрядном счетчике 5, если по каким-либо причинам в каком-либо разряде произошел сбой.

При поступлении очередного импульса NK с выхода одновибратора 2 состояние n-разрядного счетчика 5 R1X=В=р11=2, а при состоянии управляемого счетчика 11 R2X=1 на выходной шине ПЗУ 12 формируется сигнал А=2. В этом случае на выходе А=В цифрового компаратора 10 вырабатывается сигнал S=1, который останавливает счет импульсов с генератора 20 счетчиком 22 и разрешает формирование выходной информации первым 13 и вторым 14 дешифраторами при кодовом состоянии на входной шине R2X=1. Пусть при R2X=1 второй дешифратор 14 формирует на своем выходе D такой код, который устанавливает мультиплексор 9 в состояние, при котором на его выход подключается последовательность импульсов τq2, а ПЗУ при

R2X=2 подключает к выходу ячейку с адресом 2, содержимое которой А=p11+p12=2+8=10. При выходном сигнале n-разрядного счетчика 5 R1X=p11+p12=10 на шине А цифрового компаратора 10 формируется сигнал А=10, при R2X=2 и на выходе А=В цифрового компаратора 10 вырабатывается сигнал S=1, который останавливает счет импульсов с генератора 20 счетчиком 22 и разрешает формирование выходной информации первым 13 и вторым 14 дешифраторами при кодовом состоянии на входной шине R2X=2.

Пусть при R2X=2 второй дешифратор 14 формирует на своем выходе D такой код, который устанавливает мультиплексор 9 в состояние, при котором на его выход подключается последовательность импульсов τq3, а ПЗУ при R2X=3 подключает к выходу ячейку с адресом 3, содержимое которой А=р11+p12+p13=2+8+12=22. При выходном сигнале n-разрядного счетчика 5 R1X=p11+p12+p13=22 на шине А цифрового компаратора 10 формируется сигнал А=22, при R2X=3 и на выходе А=В цифрового компаратора 10 вырабатывается сигнал S=1, который останавливает счет импульсов с генератора 20 счетчиком 22 и разрешает формирование выходной информации первым 13 и вторым 14 дешифраторами при кодовом состоянии на входной шине R2X=3.

Так как цифровой сигнал С=С1=р11+p12+p13, то в этом случае согласно (6) на выходе первого дешифратора 13 формируется метка времени M1, при этом текущее время t=t1=T1. Далее ПЗУ подключает к выходу ячейку с адресом R2X=4, содержимое которой А=р11+р12+р13+p21=22+2=24, a второй дешифратор 14 формирует на своем выходе D при R2X=3 такой код, который устанавливает мультиплексор 9 в состояние, при котором на его выход подключается последовательность импульсов τq1. Далее процесс формирования меток времени М2, М3, М4 и M5 аналогичен описанному выше процессу. При С=С2=C1+p21+р22+p23 согласно (6) формируется метка времени М2, при этом текущее время t=t2=Т1+Т2.

Закон переключения мультиплексора 9 при известных заранее коэффициентах pji весьма прост. Если, например, n=3, то шина управления D мультиплексором 9 должна содержать 2 разряда, при этом код 01 может соответствовать подключению на выход мультиплексора 2 импульсов τq1, код 02 может соответствовать подключению на выход мультиплексора 2 импульсов τq2, код 03 может соответствовать подключению на выход мультиплексора 2 импульсов τq3. Если pji≠0, то все числа R2X=3d(d=1, 2, …) соответствуют коду 01, все числа R2X=3d+1 соответствуют коду 02, все числа R2X=3d+2 соответствуют коду 03.

Эффект от использования предлагаемого изобретения состоит в упрощении реализации за счет уменьшения числа межканальных связей и снижения объема преобразуемой информации. Покажем это. Предположим, что число n=30. В этом случае для реализации резервированного счетчика по известной схеме [2] потребуется 120 межканальных связей (каждый разряд требует 4-х межканальных связей). Кроме того, для реализации этих связей потребуется установка в каждый канал 60 оптронов. В случае реализации резервированного счетчика на ПЛИС с 64 выводами потребуется установка трех таких ПЛИС вместо одной.

Для реализации резервированного счетчика по предлагаемой схеме в каждом канале требуется 6 межканальных связей и установка 4-х оптронов

Реализация резервированного счетчика по предлагаемой схеме может быть выполнена на одной ПЛИС в каждом канале. Иначе, предлагаемая схема резервированного счетчика значительно проще известного решения [2] за счет сокращения числа межканальных связей.

В известном решении [2] формирование временной метки происходит при совпадении текущего времени, фиксируемого в n-разрядном счетчике, с заданным. Для рассмотренного случая максимальное время TM, которое подлежит сравнению с заданным, будет равно TM=T1+Т2+Т3+Т4+T5=38460 с. Для представления таких чисел требуется 16 двоичных разрядов. В устройстве, реализующем предлагаемый способ формирования меток времени, преобразованию подлежит цифровой сигнал С, максимальное значение которого равно

Для рассматриваемого случая это число С=110. Для представления этого числа требуется 7 двоичных разрядов.

Предлагаемая совокупность признаков, в рассмотренных автором решениях, не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве мажоритарных элементов, счетчиков, регистров сдвига, цифровых компараторов, мультиплексоров, программируемого запоминающего устройства и др. для реализации устройства можно использовать логические элементы цифровых микросхем любых серий, например 564 и т.д.

Литература

1. Авторское свидетельство СССР N 982197, кл. Н03К 21/40, 1982. Резервированный счетчик импульсов.

2. Патент Российской Федерации N 2103815, кл. 7 Н03К 21/40, 21/10, 23/50 от 27.01.98. Резервированный счетчик.

1. Резервированный счетчик для формирования меток времени, содержащий m каналов, а в каждом канале n-разрядный счетчик, блок из n мажоритарных элементов и последовательно соединенные мажоритарный элемент и одновибратор, выход которого соединен с входом С n-разрядного счетчика, вход D параллельной записи которого подключен к выходной шине блока из n мажоритарных элементов, отличающийся тем, что в каждый канал введены мультиплексор, блок управления, первый, второй и m-й регистры сдвига, цифровой компаратор, управляемый счетчик, программируемое запоминающее устройство, первый и второй дешифраторы, при этом в каждом канале выход одновибратора соединен с первым входом управляемого счетчика и входом блока управления, первый и второй выходы которого соединены с входами РЕ разрешения параллельной записи n-разрядного счетчика и первого регистра сдвига соответственно, третий выход блока управления соединен с входом С первого регистра сдвига и входами С соответствующих регистров сдвига других каналов, входы D которых соединены с выходом первого регистра сдвига, входы D параллельной записи которого соединены с выходной шиной n-разрядного счетчика, входной шиной В цифрового компаратора и первой входной шиной блока из n мажоритарных элементов, вторая и m-я входные шины которого подключены к выходным шинам соответственно второго и m-го регистров сдвига, входная шина А цифрового компаратора соединена с шиной данных программируемого запоминающего устройства, шина адреса которого соединена с выходной шиной управляемого счетчика и входной шиной первого и второго дешифраторов, вход управления которых соединен с выходом А=В цифрового компаратора и вторым входом управляемого счетчика, выходная шина первого дешифратора соединена с выходной шиной устройства, выходная шина второго дешифратора соединена с входной шиной мультиплексора, входы которого подключены к соответствующим входам устройства, выход мультиплексора каждого канала соединен с соответствующими входами мажоритарного элемента всех каналов.

2. Резервированный счетчик для формирования меток времени по п.1, отличающийся тем, что управляемый счетчик содержит триггер, генератор, элемент И, счетчик, первый и второй входы управления, при этом выход генератора соединен с первым входом элемента И, второй вход которого соединен с выходом триггера, вход S которого соединен с первым входом управления и входом R счетчика, третий вход элемента И соединен с инверсным выходом последнего разряда счетчика, вход С которого соединен с выходом элемента И, вход R триггера соединен с вторым входом управления, выходы каждого разряда счетчика соединены с выходной шиной управляемого счетчика.