Цифровой синтезатор частот

Иллюстрации

Показать всеИзобретение относится к радиотехнике и может использоваться в качестве быстро переключаемого по частоте гетеродина приемника и в других устройствах, где требуется быстрая перестройка по частоте при чистом спектре выходного сигнала. Достигаемый технический результат - получение высокого быстродействия и стабильности работы при сохранении высокой спектральной чистоты выходного сигнала. Цифровой синтезатор частот содержит управляемый генератор, два делителя с переменным коэффициентом деления, два фильтра нижних частот, два делителя с фиксированным коэффициентом деления, опорный генератор, два частотно-фазовых детектора, инвертирующий сумматор, буферный усилитель, микроконтроллер, инвертор. 3 ил.

Реферат

Предлагаемое изобретение относится к радиотехнике и может использоваться в качестве быстро переключаемого по частоте гетеродина приемника и в других устройствах, где требуется быстрая перестройка по частоте при чистом спектре выходного сигнала.

Известен цифровой синтезатор частот (ЦСЧ), построенный по однокольцевой схеме импульсно-фазовой автоподстройки частоты (ИФАПЧ) с делителем частоты с переменным коэффициентом деления (ДПКД) в цепи обратной связи, в котором для получения высокого быстродействия при переключении выходных частот синтезатора применяется дробный ДПКД (ДДПКД) вместо обычного целочисленного ДПКД. Это позволяет использовать частоту сравнения FCP на опорном входе частотно-фазового детектора (ЧФД) во много раз больше заданного шага FШ сетки частот синтезатора (см. книгу Шапиро Д.Н., Паин А.А. Основы теории синтеза частот. - М.: Радио и связь, 1981, стр.166, рис.7.4, а также а.с. СССР №470901, Н03В 21/02, 1975 г.). Из-за высокой частоты сравнения FСР происходит автоподстройка управляемого генератора гораздо чаще, чем в ЦСЧ с целочисленным ДПКД. В результате повышается быстродействие при переключении с одной частоты на другую.

Недостаток известного ЦСЧ в том, что в синтезаторе с ДДПКД имеется так называемая значительная «помеха дробности» с низкой частотой (примерно равной заданному шагу сетки частот FШ) даже при современных микросхемах ЦСЧ с ΣΔ компенсацией этих помех (см. В.Майская "FRACTIONAL N СИНТЕЗАТОРЫ", журнал ЭЛЕКТРОНИКА: Наука, Технология, Бизнес №5, 2002 г., стр.10-16). Для подавления этих «помех дробности» до требуемых значений нужен почти такой же узкополосный петлевой фильтр нижних частот (ФНЧ), как и при использовании обычного целочисленного ДПКД. Это, в свою очередь, значительно уменьшает ширину полосы пропускания кольца ИФАПЧ и быстродействие при переключении частот.

Наиболее близким по технической сущности к предлагаемому устройству является цифровой синтезатор частот (см. авторское свидетельство СССР №1510080 от 23.09.1989 г.), который принят за прототип.

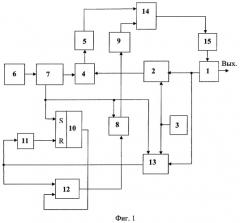

Блок-схема устройства-прототипа представлена на фиг.1, где введены следующие обозначения:

1 - управляемый генератор (УГ);

2 и 13 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

3 - блок установки выходной частоты;

4 - частотно-фазовый детектор (ЧФД);

5 и 9 - первый и второй фильтры нижних частот (ФНЧ);

6 - опорный генератор (ОГ);

7 - делитель частоты с фиксированным коэффициентом деления (ДФКД);

8 - фазовый детектор (ФД);

10 - RS-триггер;

11 - элемент задержки;

12 - элемент «И»;

14 - инвертирующий сумматор (СУМ);

15 - инвертор.

Устройство-прототип содержит последовательно соединенные управляемый генератор (УГ) 1, первый делитель частоты с переменным коэффициентом деления (ДПКД) 2, частотно-фазовый детектор (ЧФД) 4, первый фильтр нижних частот (ФНЧ) 5, выход которого соединен с первым входом инвертирующего сумматора СУМ 14, выход которого через инвертор 15 соединен с управляющим входом управляемого генератора УГ 1, второй выход которого является выходом устройства; последовательно соединенные опорный генератор (ОГ) 6 и делитель частоты с фиксированным коэффициентом деления (ДФКД) 7, второй (основной) выход которого соединен со вторым входом ЧФД 4; последовательно соединенные фазовый детектор (ФД) 8 и второй фильтр нижних частот (ФНЧ) 9, выход которого соединен со вторым входом СУМ 14, а также RS-триггер 10, первый вход (S-вход) которого соединен с первым (промежуточным) выходом ДФКД 7, второй вход (R-вход) RS-триггера 10 соединен с выходом элемента задержки 11, а выход RS-триггера 10 соединен со вторым входом элемента «И» 12, выход которого соединен с первым входом фазового детектора 8, при этом блок установки выходной частоты 3, выход которого соединен со вторыми (управляющими) входами первого ДПКД 2 и второго ДПКД 13, а первый (промежуточный) выход ДФКД 7, кроме того, соединен со вторым входом ФД 8 и с первым входом второго ДПКД 13, третий вход которого соединен с первым выходом УГ 1, а выход второго ДПКД 13 соединен с первыми входами элемента задержки 11 и элемента «И» 12.

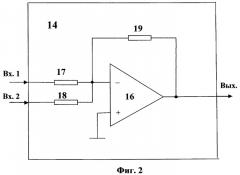

Инвертирующий сумматор 14 (см. фиг.2) содержит операционный усилитель 16 и первый 17, второй 18 и третий 19 резисторы.

Устройство-прототип работает следующим образом.

В этом ЦСЧ параллельно основному (узкополосному) кольцу автоподстройки, состоящему из УГ 1, первого ДПКД 2, ЧФД 4, первого ФНЧ 5, инвертирующего сумматора 14 и инвертора 15, выход которого соединен с управляющим входом УГ 1, включено дополнительное (широкополосное) кольцо автоподстройки из того же УГ 1, второго ДПКД 13, элемента И 12, ФД 8, второго ФНЧ 9, выход которого подключен ко второму входу инвертирующего сумматора 14. Дополнительное кольцо работает на частоте сравнения FСР в n раз больше заданного шага сетки частот FШ, а в основном кольце частота сравнения FСР не более заданного шага сетки частот FШ. Повышение быстродействия достигается за счет того, что подстройка управляющего напряжения УГ 1 осуществляется в n раз чаще, чем если бы работало только одно основное кольцо.

В режиме синхронизма импульсы с выхода первого ДПКД 2 практически почти совпадают с опорными импульсами, поступающими на второй вход ЧФД 4, т.е. основное кольцо автоподстройки представляет собой систему ИФАПЧ с астатизмом второго порядка. В дополнительном кольце опорные импульсы поступают на вход ФД 8 типа «выборка-запоминание» и запускают его генератор пилообразного напряжения. Одновременно эти же импульсы поступают на вход сброса второго ДПКД 13 и на S-вход RS-триггера 10, устанавливая его в состояние лог.1 по выходу. С выхода RS-триггера 10 уровень лог. 1 поступает на второй вход элемента И 12 и разрешает прохождение сигналов по первому его входу с выхода второго ДПКД 13. После сброса импульсом с выхода ДФКД 7 второй ДПКД 13 начинает новый счет, т.е. оба делителя начинают счет одновременно. Импульс с выхода второго ДПКД 13 через элемент И 12 поступает на другой вход ФД 8, а через элемент 11 задержки - на R-вход RS-триггера 10, переводя его в состояние «Лог. 0». Этот сигнал с выхода RS-триггера 10 поступает на второй вход элемента И 12 и закрывает его. После этого второй ДПКД 13 начинает новый счет импульсов, но не успевает его завершить, так как импульс с выхода ДФКД 7 сбросит его и оба делителя начнут счет сначала. А RS-триггер 10 этим же импульсом установится в исходное состояние, и процесс повторится. Если до прихода следующего импульса с выхода ДФКД 7 (до окончания развертки пилообразного напряжения в ФД 8) появится второй импульс с выхода второго ДПКД 13, то он не пройдет через элемент И 12, так как на втором входе элемента И 12 присутствует запрещающий сигнал «Лог. 0» с выхода RS-триггера 10.

Таким образом, в режиме синхронизма импульс выборки должен приходить всегда в одну и ту же точку пилообразного напряжения, т.е. на выходе ФД 8 или входе второго ФНЧ 9 формируется определенная величина управляющего напряжения V2, которое поступает на второй вход инвертирующего сумматора 14. А на выходе ЧФД 4 в результате сравнения двух потоков импульсов формируется основное управляющее напряжение V1 которое через первый ФНЧ 5 поступает на первый вход инвертирующего сумматора 14. При этом суммарное управляющее напряжение на управляющем входе УГ 1 равно взвешенной сумме управляющих напряжений с выходов первого ФНЧ 5 и второго ФНЧ 9

VΣ=V1+V2/n

Весовой коэффициент n выбирается из следующих соображений. Коэффициент усиления многовходового усилителя-сумматора (построенного на основе операционного усилителя 16 с заземленным неинвертирующим входом, фиг.2) определяется по каждому j входу как

Kj=Roc/Rj,

где Roc - сопротивление обратной связи операционного усилителя,

Rj - сопротивление соответствующего резистора.

С помощью резисторов, включенных во входную цепь усилителя-сумматора, можно реализовать весовые коэффициенты для каждого из слагаемых, если принять, что первый резистор 17 равен третьему резистору 19 (в обратной связи), а второй резистор 18 равен R2=nR1,

где R2 - сопротивление второго резистора 18,

R1 - сопротивление первого резистора 17.

Каждому значению управляющего напряжения VΣ на управляющем входе УГ 1 соответствует определенная частота на его выходе. Для изменения частоты выходного сигнала ЦСЧ на заданную величину Δf (шаг) нужно на соответствующую величину изменить управляющее напряжение ΔV1 по первому входу сумматора. Если выбрать частоту опорных импульсов в дополнительном кольце в n раз больше, чем в основном, определяемом заданным шагом сетки частот, то при одновременном переключении коэффициентов деления на единицу первого ДПКД 2 и второго ДПКД 13 от блока 3 установки выходной частоты напряжение на выходе ЧФД 4 до прихода импульса с выхода первого ДПКД 2 еще не изменится, а в дополнительном кольце автоподстройки пройдет n периодов регулирования.

Причем после первого же периода регулирования в основном кольце управляющее напряжение на выходе ФД 8 изменится на величину ΔV2=nΔV1, где ΔV1 - изменение управляющего напряжения, которое было бы на выходе ЧФД 4, если бы работало только одно основное кольцо. Тогда после первого же периода регулирования в дополнительном кольце суммарное управляющее напряжение УГ 1 станет равно

VΣ=V1+V2/n+ΔV2/n=V1+V2/n+nΔV1/n=V1+V2/n+ΔV1, т.е. изменится на величину ΔV1, как и требовалось для заданного приращения частоты Δf (шаг сетки частот).

Таким образом, в ЦСЧ-прототипе должен быть выигрыш по быстродействию из-за того, что подстройка управляющего напряжения осуществляется в n раз чаще, чем если бы работало только одно основное кольцо автоподстройки.

Недостаток устройства-прототипа состоит в следующем. В этом ЦСЧ работают одновременно основное (медленное) кольцо с цифровым ЧФД и дополнительное (быстродействующее), в котором FСР=nFШ. Первое (основное) кольцо в режиме синхронизма работает так, что на входах ЧФД 4 потоки сравниваемых импульсов с ДФКД 7 и ДПКД 2 равны не только по частоте, но и практически по фазе (синфазная система). Второе кольцо на основе ФД 8 типа «выборка-запоминание» работает только на основе разности фаз импульсов с выходов ДФКД 7 и ДПКД 13. Причем эта разность фаз на разных частотах разная, т.е. в переходном режиме на выходе ФД 8 получается разный набег фаз, и это может выбивать первое кольцо с ЧФД 4 из синхронизма. В дополнительном кольце подстройка частоты происходит гораздо быстрее, чем в основном. При этом основное кольцо будет мешать подстройке частоты в переходном режиме, т.к. от этих двух колец подстройка УГ 1 происходит в разные моменты времени и возможна в противоположных направлениях - вхождение в синхронизм может затягиваться.

Второй недостаток состоит в том, что в ЦСЧ-прототипе быстродействие ограничивается первым кольцом, которое работает на низкой частоте сравнения FСР=FШ. В переходном режиме первое кольцо может задерживать вхождение ЦСЧ в синхронизм.

Третий недостаток в том, что использование одного ДФКД с основным и промежуточным выходом ограничивает возможность оптимального выбора частот сравнения в кольцах и управления быстродействием, когда нужно в переходном режиме устраивать синхронный сброс счетчиков. Кроме того, в выпускаемых в настоящее время микросхемах ЦСЧ выделить в ДФКД промежуточный выход не представляется возможным.

Таким образом, быстродействие и стабильность работы в этом ЦСЧ-прототипе недостаточные.

Для устранения указанных недостатков в цифровой синтезатор частот, содержащий последовательно соединенные управляемый генератор, первый делитель частоты с переменным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, выход которого соединен с первым входом инвертирующего сумматора, выход которого через инвертор соединен с управляющим входом управляемого генератора, второй выход которого является выходом устройства, а также второй делитель частоты с переменным коэффициентом деления, вход которого соединен с первым выходом управляемого генератора, последовательно соединенные опорный генератор и первый делитель частоты с фиксированным коэффициентом деления, выход которого соединен со вторым входом первого частотно-фазового детектора; второй фильтр нижних частот, выход которого соединен со вторым входом инвертирующего сумматора, в него введены последовательно соединенные второй делитель частоты с фиксированным коэффициентом деления и второй частотно-фазовый детектор, выход которого соединен со входом второго фильтра нижних частот, последовательно соединенные буферный усилитель и микроконтроллер, выходная шина которого соединена с управляющими входами первого делителя частоты с фиксированным коэффициентом деления и второго делителя частоты с фиксированным коэффициентом деления, первого частотно-фазового детектора и второго частотно-фазового детектора, первого делителя частоты с переменным коэффициентом деления и второго делителя частоты с переменным коэффициентом деления, выход которого соединен со вторым входом второго частотно-фазового детектора, причем вход буферного усилителя соединен с выходом первого фильтра нижних частот, а вход второго делителя частоты с фиксированным коэффициентом деления соединен с выходом опорного генератора.

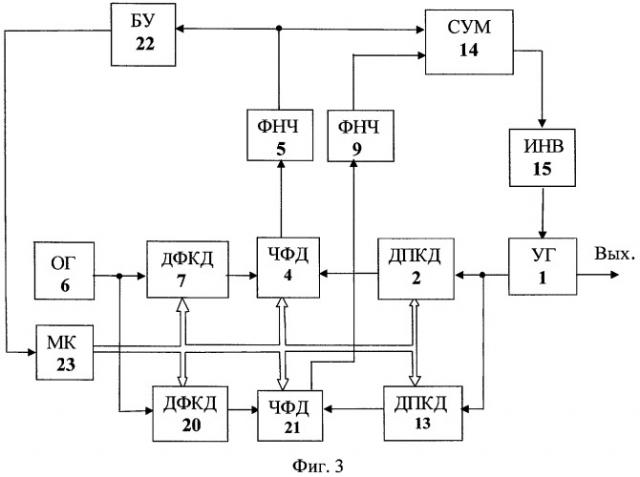

Функциональная схема предлагаемого устройства представлена на фиг.3, где введены следующие обозначения:

1 - управляемый генератор (УГ);

2 и 13 - первый и второй делители частоты с переменным коэффициентом деления (ДПКД);

4 и 21 - первый и второй частотно-фазовые детекторы (ЧФД);

5 и 9 - первый и второй фильтры нижних частот (ФНЧ);

6 - опорный генератор (ОГ);

7 и 20 - первый и второй делители частоты с фиксированным коэффициентом деления (ДФКД);

14 - инвертирующий сумматор (СУМ);

15 - инвертор (ИНВ);

22 - буферный усилитель (БУ);

23 - микроконтроллер (МК).

Предлагаемое устройство содержит последовательно соединенные управляемый генератор УГ 1, первый делитель частоты с переменным коэффициентом деления ДПКД 2, первый частотно-фазовый детектор ЧФД 4 и первый фильтр нижних частот ФНЧ 5, выход которого соединен с первым входом инвертирующего сумматора СУМ 14, выход которого через инвертор 15 соединен с управляющим входом управляемого генератора УГ 1, а также второй ДПКД 13, вход которого соединен с первым выходом УГ 1, второй выход которого является выходом устройства; последовательно соединенные опорный генератор ОГ 6 и первый ДФКД 7, выход которого соединен со вторым входом первого ЧФД 4; второй ФНЧ 9, выход которого соединен со вторым входом инвертирующего сумматора СУМ 14; последовательно соединенные второй ДФКД 20 и второй ЧФД 21, выход которого соединен со входом второго ФНЧ 9; последовательно соединенные буферный усилитель БУ 22 и микроконтроллер 23, выходная шина которого соединена с управляющими входами первого ДФКД 7 и второго ДФКД 20, первого ЧФД 4 и второго ЧФД 21, первого ДПКД 2 и второго ДПКД 13, выход которого соединен со вторым входом второго ЧФД 21. При этом вход БУ 22 соединен также с выходом первого ФНЧ 5 и выход ОГ 6 соединен со входом второго ДФКД 20.

Предлагаемое устройство работает следующим образом.

В этом ЦСЧ работают неодновременно два быстродействующих кольца ИФАПЧ с общим УГ 1. Первое кольцо состоит из УГ 1, первого ДПКД 2, первого ЧФД 4, первого ФНЧ 5, выход которого соединен с первым входом инвертирующего СУМ 14, а выход СУМ 14 через ИНВ 15 соединен с управляющим входом УГ 1. Второе кольцо состоит из того же УГ 1, второго ДПКД 13, второго ЧФД 21, второго ФНЧ 9, выход которого через второй вход СУМ 14 и ИНВ 15 соединен также с управляющим входом УГ 1. В обоих кольцах цифровые ЧФД работают на опорных частотах сравнения FСР, во много раз превышающих заданный шаг Fш сетки частот. В первом кольце частота сравнения FСР1 формируется от первого ДФКД 7, на вход которого поступает опорный сигнал с ОГ 6. Во втором кольце частота сравнения FСР2 формируется от второго ДФКД 20, вход которого также соединен с выходом ОГ 6. Выключение каждого кольца происходит по сигналу от микроконтроллера МК 23 путем перевода соответствующего ЧФД в третье состояние (т.е. кольцо разрывается), а включение каждого кольца происходит также по сигналу от МК 23 путем перевода соответствующего ЧФД из третьего состояния в рабочий режим. Третье состояние ЧФД характеризуется тем, что его выход внутри микросхемы отключается от всех цепей и имеет очень высокое выходное сопротивление (см., например, описание микросхем синтезаторов ADF4252, ADF4001, ADF4153 фирмы Analog Devices, LMX2364, LMX2470 фирмы National Semiconductor). Поэтому ФНЧ (обычно активный ФНЧ на операционном усилителе), соединенный с таким выходом ЧФД, сохраняет то управляющее напряжение, которое было перед отключением ЧФД.

В начале переходного режима после достижения синхронизма в первом кольце по сигналу управления от МК 23 первый ЧФД 4 переключается в третье состояние и на выходе первого ФНЧ 5 сохраняется постоянное управляющее напряжение Vупр1 ("подставка"), которое поступает на первый вход СУМ 14. Одновременно по сигналу от МК 23 включается второе кольцо и управляющее напряжение Vупр2 с выхода второго ФНЧ 9 поступает на второй вход СУМ 14. В результате на выходе СУМ 14 формируется суммарное управляющее напряжение VупрΣ, равное взвешенной сумме управляющих напряжений с первого ФНЧ 5 и второго ФНЧ 9

VупрΣ=Vупр1+Vупр2/n,

где весовой коэффициент n=FСР2/FШ.

Весовой коэффициент n СУМ 14 выбирается с помощью входных резисторов операционного усилителя-сумматора (см. фиг.2) так, как описано выше.

Известно, что при увеличении частоты сравнения в n раз, шаг перестройки в ЦСЧ также увеличивается в n раз из-за того, что дискретное приращение управляющего напряжения при изменении коэффициента деления ДПКД на единицу будет тоже в n раз больше. В предложенном ЦСЧ инвертирующий сумматор СУМ 14 осуществляет взвешенное суммирование входных управляющих напряжений так, что на выходе его уровень управляющего сигнала от первого кольца проходит без изменения, а от второго кольца - уменьшается в n раз. В результате после СУМ 14 приращение управляющего напряжения на входе УГ 1 получается соответствующим заданному шагу, т.е. подстройка происходит с заданным дискретом. А выигрыш состоит в том, что эта подстройка происходит в n раз чаще, что и приводит к повышению быстродействия.

От второго кольца частота УГ 1 переключается с заданным шагом в пределах некоторого поддиапазона, в котором сохраняется постоянное управляющее напряжение Vупр1 с первого кольца ("подставка").

В результате весь диапазон управляющего напряжения для УГ 1 разбивается на несколько поддиапазонов, внутри которых с помощью второго кольца происходит перестройка частоты УГ 1 с заданным шагом.

Величина каждого поддиапазона должна быть такой, чтобы при перестройке второго кольца управляющее напряжение на выходе второго ФНЧ 9 не превышало максимальное напряжение Vупр2мах (например, Vупр2мах≤10-12 В). Выбранные значения поддиапазонов записывают в память МК 23. А с выхода первого ФНЧ 5 через БУ 22 на вход МК 23 непрерывно поступает значение Vупр1 и сравнивается с записанным в памяти микроконтроллера МК 23. Если при каких-то неблагоприятных условиях Vупр1 сместится от установленных значений, то по сигналу обратной связи с выхода первого ФНЧ 5 через БУ 22 на вход МК 23 поступит новое значение Vупр1 и произойдет его сравнение с записанным в памяти МК 23. В результате включится первое кольцо и снова подстроится.

В каждом кольце ЦСЧ при переключении частот по сигналам от МК 23 происходит синхронный сброс и пуск обоих счетчиков кольца (ДФКД и ДПКД), когда оба счетчика начинают счет одновременно. Это позволяет значительно увеличить быстродействие по сравнению с тем, если бы оба счетчика срабатывали случайно в разное время, при этом получалось бы затягивание времени вхождения в синхронизм.

Управляющая шина от МК 23 представляет собой стандартный трехпроводный интерфейс, где по трем проводам поступают в последовательном коде импульсные сигналы: 1) тактовые импульсы; 2) информационный сигнал; 3) импульс разрешения записи передаваемой информации в один из блоков: ДПКД 2, ДПКД 13, ЧФД 4, ЧФД 21, ДФКД 7, ДФКД 20.

Таким образом, в предложенном ЦСЧ за счет введения новых блоков и соответствующих связей между всеми блоками синтезатора, а также за счет применения высоких частот сравнения в обоих кольцах ЦСЧ без использования дробных ДПКД при заданном шаге сетки частот значительно повышается быстродействие и стабильность работы при высокой чистоте спектра выходного сигнала.

Доказательством возможности осуществления предлагаемого ЦСЧ является то, что вводимые блоки типовые и могут быть выполнены на широко известных микросхемах. Причем в одной микросхеме могут быть один или два независимых ЦСЧ (т.е. одно- или двухканальный) с целочисленным ДПКД (Integer-N) или с дробным (Fractional-N). Например, микросхема ADF 4252 фирмы Analog Devices представляет собой двойной синтезатор с двумя раздельными контурами регулирования: один с дробным ДПКД, другой - с целочисленным. В предложенном ЦСЧ может использоваться в первом кольце любой ДПКД - и дробный, и целочисленный. А во втором кольце - только целочисленный, чтобы получить высокую спектральную чистоту выходного сигнала.

В качестве буферного усилителя используется операционный усилитель с высоким входным сопротивлением и коэффициентом передачи, близким к единице, на микросхеме AD822AR фирмы Analog Devices.

В качестве микроконтроллера МК 23 может использоваться микросхема C8051F220 фирмы Silicon Laboratories (CYGNAL).

Таким образом, в предложенном ЦСЧ имеется возможность получить высокое быстродействие и стабильность работы при высокой частоте сравнения и заданном шаге сетки частот без применения дробного ДПКД с соответствующими "помехами дробности".

Цифровой синтезатор частот, содержащий последовательно соединенные управляемый генератор, первый делитель частоты с переменным коэффициентом деления, первый частотно-фазовый детектор, первый фильтр нижних частот, выход которого соединен с первым входом инвертирующего сумматора, выход которого через инвертор соединен с управляющим входом управляемого генератора, второй выход которого является выходом устройства, а также второй делитель частоты с переменным коэффициентом деления, вход которого соединен с первым выходом управляемого генератора, последовательно соединенные опорный генератор и первый делитель частоты с фиксированным коэффициентом деления, выход которого соединен со вторым входом первого частотно-фазового детектора; второй фильтр нижних частот, выход которого соединен со вторым входом инвертирующего сумматора, отличающийся тем, что в него введены последовательно соединенные второй делитель частоты с фиксированным коэффициентом деления и второй частотно-фазовый детектор, выход которого соединен со входом второго фильтра нижних частот, последовательно соединенные буферный усилитель и микроконтроллер, выходная шина которого соединена с управляющими входами первого делителя частоты с фиксированным коэффициентом деления и второго делителя частоты с фиксированным коэффициентом деления, первого частотно-фазового детектора и второго частотно-фазового детектора, первого делителя частоты с переменным коэффициентом деления и второго делителя частоты с переменным коэффициентом деления, выход которого соединен со вторым входом второго частотно-фазового детектора, причем вход буферного усилителя соединен с выходом первого фильтра нижних частот, а вход второго делителя частоты с фиксированным коэффициентом деления соединен с выходом опорного генератора.