Устройство обработки битовых потоков в системах сжатия/восстановления аудио- и видеоданных

Иллюстрации

Показать всеПредлагаемое устройство относится к цифровой обработке сигналов и может быть использовано в устройствах обработки изображения и звука, а именно обработки битовых данных на выходе устройства. Техническим результатом изобретения является увеличение быстродействия склейки и сдвига данных при сокращении аппаратных средств. Этот результат достигается за счет введения в устройство регистра первого операнда, регистра второго операнда, регистра выхода результата, блока для выполнения операции склейки, блока для выполнения операции разворота - перестановки байтов, блока для выполнения операции сдвига, блока извлечения битов, в котором формируется полное слово данных с предварительным выравниванием, сдвоенного мультиплексора, осуществляющего исходную загрузку слова данных из памяти данных. 2 ил.

Реферат

Устройство обработки битовых потоков в системах сжатия/восстановления аудио-и видеоданных

Настоящее изобретение относится к цифровой обработке сигналов и может быть использовано в устройствах обработки изображения и звука, а именно обработки битовых данных на входе устройства.

Предлагаемое устройство предназначено для использования в системах обработки данных совместно с микропроцессором с целью ускорения обработки битовых потоков в устройствах декодирования сжатых аудио-и видеоданных.

Известно «устройство склейки/маскирования, поворота/сдвига и Булевых операций для двух систем команд, выполняемых на векторном мультиплексоре в двойном АЛУ» [1], включающее:

- регистр первого операнда,

- регистр второго операнда,

- растяжитель байта для копирования байтового операнда в АЛУ,

- регистр выхода результата,

- сумматор для выполнения операций сложения и вычитания первого и второго операнда,

- блоки для выполнения операций: склейки, разворота - перестановки байтов, сдвига и Булевых операций.

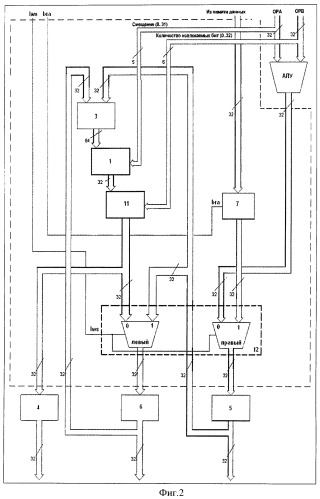

На Фиг.1 приведена блок-схема устройства [1], где

1 - блок выполнения операции сдвига,

2 - регистр для хранения результата промежуточных данных,

3 - блок выполнения операции склейки,

4 - регистр выхода результат,

5 - регистр первого операнда,

6 - регистр второго операнда,

7 - блок выполнения операции разворота - перестановки байтов на Фиг.1 не показан,

(7) - растяжитель байта для копирования байтового операнда в АЛУ на Фиг.1 не показан,

(9) - сумматор для выполнения операций сложения и вычитания первого и второго операнда на Фиг.1 не показан,

(10) - блок выполнения операции Булевых операций на Фиг.1 не показан.

Как следует из анализа описания прототипа [1], несовершенство устройства [1] заключается в том, что результаты функций склейки и сдвига доступны только на третьем шаге (на третьем синхроимпульсе) с потерей быстродействия системы, что показано на Фиг.1 - шаг 1, шаг 2, шаг 3.

Известно устройство «микропроцессор для обработки битовых потоков в системах компрессии/ восстановления сжатых изображений» [21.

Однако в указанном устройстве имеются существенные ограничения: не решаются функции склейки и сдвига данных двух 32-х разрядных слов в системе с 32-х разрядным представлением данных.

Задача, на решение которой направлено заявляемое изобретение, заключается в создании устройства, позволяющего выполнить функции склейки и сдвига данных с большим быстродействием при меньшей стоимости аппаратуры за счет ее сокращения.

Для достижения указанного результата в «устройство склейки/маскирования, поворота/сдвига и Булевых операций для двух систем команд, выполняемых на векторном мультиплексоре в двойном АЛУ» [1], включающее:

- регистр первого операнда,

- регистр второго операнда,

- регистр выхода результата,

- блок для выполнения операции склейки,

- блок для выполнения операции разворота - перестановки байтов,

- блок для выполнения операции сдвига,

добавляют блок извлечения битов, в котором формируется полное слово данных с предварительным выравниванием, и сдвоенный мультиплексор, осуществляющий исходную загрузку слова данных из памяти данных, при этом блок операции склейки, имеющий два входа данных и один выход данных, первым входом подключают к выходу регистра второго операнда, вторым входом подключают к выходу регистра первого операнда, а выход блока операции склейки подключают ко входу данных блока операции сдвига, имеющего двойную ширину данных на входе, на управляющий вход блока операции сдвига подают значение смещения от АЛУ, внешнего к устройству, выход блока операции сдвига, имеющего одиночную ширину шины данных, подключают ко входу данных блока извлечения бит, на управляющий вход блока извлечения бит подают значение выбора количества извлекаемых бит от АЛУ, выход блока извлечения бит подключают к регистру выхода результата и к «0» входу левой части сдвоенного мультиплексора, выход левой части мультиплексора подключают ко входу регистра второго операнда, выход регистра первого операнда подключают к «1» входу левой части сдвоенного мультиплексора и к правому входу данных блока операции склейки, к «0» входу правой части сдвоенного мультиплексора подают слово данных от АЛУ для загрузки регистра первого операнда, к «1» входу правой части сдвоенного мультиплексора через блок для выполнения операции разворота - перестановки байтов подают слово данных из памяти данных, внешней к устройству.

Проведенные патентные исследования показали, что совокупность отличительных признаков нашего изобретения является новой, что доказывает новизну заявляемого устройства.

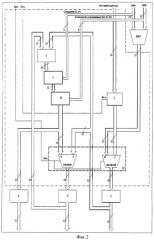

Предлагаемое устройство приведено на Фиг.2, где

1 - блок выполнения операции сдвига,

3 - блок выполнения операции склейки,

4 - регистр выхода результата,

5 - регистр первого операнда,

6 - регистр второго операнда,

7 - блок выполнения операции разворота перестановки байтов,

11 - блок извлечения битов, в котором формируется полное слово данных с предварительным выравниванием,

12 - сдвоенный мультиплексор, осуществляющий исходную загрузку слова данных из памяти данных.

Блок извлечения бит выполняется по схеме наложения разрешающей маски на каждый из совокупности единичных сигналов, объединенных в шину данных [3]. Входной сигнал свернутой разрешающей маски разворачивается с помощью дешифратора [4] с накоплением младших разрядов.

Сдвоенный мультиплексор представляет из себя два стандартных мультиплексора, имеющих один общий сигнал переключения. Описание устройства мультиплексора представлено в [5].

Устройство состоит из блока операции склейки 3, имеющего два входа данных и один выход данных, первый (левый) вход которого подключен к выходу регистра второго операнда 6, а второй (правый) вход которого подключен к выходу регистра первого операнда 5. Выход блока операции склейки подключен ко входу данных блока операции сдвига 1, имеющему двойную ширину данных на входе, на управляющий вход блока операции сдвига подается значение смещения от АЛУ, внешнего к устройству. Выход блока операции сдвига 1 имеет одиночную ширину шины данных и подключен ко входу данных блока извлечения бит 11, на управляющий вход блока извлечения бит 11 подается значение выбора количества бит от АЛУ. Выход блока извлечения бит 11 подключен к регистру выхода результата 4 для хранения данных результата и к «0» входу левой части сдвоенного мультиплексора 12. Выход левой части мультиплексора 12 подключен ко входу регистра второго операнда 6. Выход регистра первого операнда 5 подключен ко «1» входу левой части сдвоенного мультиплексора 12 и к второму (правому) входу данных блока операции склейки 3. К «0» входу правой части сдвоенного мультиплексора 12 поступает выходное слово от АЛУ для загрузки регистра первого операнда 5. К «1» входу правой части сдвоенного мультиплексора 12 подается слово данных из памяти данных, внешней к устройству, через блок для выполнения операции разворота-перестановки байтов 7. Переключение сдвоенного мультиплексора 12 производится входным управляющим сигналом lws (Load Word and Save - загрузка слова и сохранение). Отключение блока для выполнения операции разворота - перестановки байтов 7 производится входным управляющим сигналом bra (Byte Reallocate - перестановка байт). Выбор количества позиций единичных сдвигов влево от 0 до 31 в блоке операции сдвига 1 задается пятью младшими разрядами ОРА (Операнд А) из АЛУ, внешними по отношению к устройству. Выбор количества извлекаемых бит от 0 до 32 в блоке извлечения бит 11 задается шестью младшими разрядами ОРВ (Операнд В) из АЛУ, внешними по отношению к устройству, при извлечении менее чем 32 бит все остальные неиспользуемые старшие битовые позиции заполняются нулями.

Устройство работает следующим образом.

В систему команд процессора, совместно с которым работает устройство, вводятся новые команды:

1. LWS - (Load Word and Save) - команда загрузки двойного слова, то есть загрузки «старшего» регистра первого операнда 5 с одновременной перезаписью его уже имеющегося значения в «младший» регистр второго операнда 6.

2. BRA - (Byte Reallocate) - команда перестановки байтов при записи слова в регистр первого 5.

При выполнении процессором команды LWS в АЛУ процессора должен быть сформирован (активизирован) однобитовый сигнал lws, являющийся необходимым входным сигналом для работы устройства. При выполнении процессором любой другой команды однобитовый сигнал Iws должен быть неактивен.

При выполнении процессором команды BRA в АЛУ процессора должен быть сформирован (активизирован) однобитовый сигнал bra, являющийся необходимым входным сигналом для работы устройства. При выполнении процессором других команд однобитовый сигнал bra должен быть неактивен. Однобитовый сигнал bra может быть активен вместе с сигналом lws в случае, если при выполнении команды LWS требуется осуществить перестановку байт в загружаемом слове данных из памяти данных.

Для реализации команды загрузки LWS в АЛУ процессора выделяются два регистра общего назначения 5 и 6. Эти регистры являются регистрами первого и второго операндов соответственно, работают совместно с устройством, но являются по отношению к нему внешними. В момент исполнения команды LWS внешним процессором активизируется сигнал lws, который и переключает сдвоенный мультиплексор 12 в устройстве. Регистры первого и второго операндов 5 и 6 конфигурируются сдвоенным мультиплексором 12 для одновременной записи в них информации в «старший» регистр первого операнда 5 - из памяти данных, а в «младший» регистр второго операнда 6 - предыдущего значения из «старшего» регистра первого операнда 5. Таким образом, происходит сдвиг «старшего» слова данных информации в позицию «младшего» слова данных.

Выбранная и дополненная нулями до полной длины слова данных на блоке извлечения бит 11 группа бит из двойного слова данных, предварительно сдвинутая на блоке операции сдвига 1 на заданное количество битовых позиций, является результатом работы устройства и сохраняется в регистре результата 4, являющимся частью АЛУ процессора, но внешним, по отношению к устройству.

Во всех остальных командах АЛУ процессора эти регистры 5, 6 и 4 ведут себя как обычные регистры общего назначения процессора. Если данные в памяти представлены в виде 32-х разрядных слов, где младший байт находится слева, то необходимо на входе данных в правую часть сдвоенного мультиплексора 12 задействовать блок операции разворота-перестановки байтов 7 - установив (активизировав) бит bra.

Результаты сравнения предлагаемого устройства и прототипа [1] показывают, что предлагаемое устройство (Фиг.2) содержит меньший объем аппаратуры, чем устройство прототипа (Фиг.1), что позволяет существенно снизить затраты на изготовление устройства.

В предлагаемом устройстве количество функциональных блоков уменьшается примерно на 20% от общего объема аппаратуры.

Анализ работы устройства прототипа [1] показывает, что функции склейки и сдвига выполняются за 3 такта, в то время как при работе нашего устройства функции склейки и сдвига выполняются за 2 такта, что сокращает время работы устройства на треть (33%), увеличивая быстродействие.

Литература:

[1] - патент США 5.781.457

[2] - патент США 6.144.321

[3] - Е.Угрюмов. Цифровая схемотехника. Стр. 330-332. Санкт-Петербург, изд. «бхв-Санкт-Петербург», 2000 г. ISBN 5-8206-0100-9

[4] - Е.Угрюмов. Цифровая схемотехника. Стр. 46-50. Санкт-Петербург, изд. «бхв-Санкт-Петербург», 2000 г. ISBN 5-8206-0100-9

[5] - Е.Угрюмов. Цифровая схемотехника. Стр. 54-55. Санкт-Петербург, изд. «бхв-Санкт-Петербург», 2000 г. ISBN 5-8206-0100-9

Устройство обработки битовых потоков в системах сжатия/восстановления аудио- и видеоданных, включающее регистр первого операнда, регистр второго операнда, регистр выхода результата, блок для выполнения операции склейки, блок для выполнения операции разворота-перестановки байтов, блок для выполнения операции сдвига, отличающееся тем, что добавляют блок извлечения битов, в котором формируется полное слово данных с предварительным выравниванием, и сдвоенный мультиплексор, осуществляющий исходную загрузку слова данных из памяти данных, при этом блок операции склейки, имеющий два входа данных и один выход данных, первым входом подключают к выходу регистра второго операнда, вторым входом подключают к выходу регистра первого операнда, а выход блока операции склейки подключают ко входу данных блока операции сдвига, имеющего двойную ширину данных на входе, на управляющий вход блока операции сдвига подают значение смещения от АЛУ, внешнего к устройству, выход блока операции сдвига, имеющего одиночную ширину шины данных, подключают ко входу данных блока извлечения бит, на управляющий вход блока извлечения бит подают значение выбора количества извлекаемых бит от АЛУ, выход блока извлечения бит подключают к регистру выхода результата и к «0»-входу левой части сдвоенного мультиплексора, выход левой части мультиплексора подключают ко входу регистра второго операнда, выход регистра первого операнда подключают к «1»-входу левой части сдвоенного мультиплексора и к правому входу данных блока операции склейки, к «0»-входу правой части сдвоенного мультиплексора подают слово данных от АЛУ для загрузки регистра первого операнда, к «1»-входу правой части сдвоенного мультиплексора через блок для выполнения операции разворота-перестановки байтов подают слово данных из памяти данных, внешней к устройству.