Нейросетевой преобразователь кода в частоту

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано для линейного и нелинейного цифроаналогового преобразования знакопеременного кода в частоту с возможностью цифровой коррекции, а также в вычислительных устройствах для умножения частоты следования импульсных сигналов на параллельный двоичный код. Техническим результатом является расширение функциональных возможностей устройства. Устройство содержит два двоичных умножителя, каждый из которых состоит из двоичного счетчика и мультиплексора, две искусственные нейронные сети, два блока памяти весовых коэффициентов, два инвертора, устройство мультиплексирования выходных двоичных сигналов, состоящее из двоичного счетчика, трех компараторов, инвертора, элемента И и двухканального мультиплексора. 3 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для линейного и нелинейного цифроаналогового преобразования знакопеременного кода в частоту с возможностью цифровой коррекции, а также в вычислительных устройствах для умножения частоты следования импульсных сигналов на параллельный двоичный код.

Наиболее близким по совокупности признаков и по технической сущности к заявляемому устройству является преобразователь кода в частоту (патент РФ № 2285946, МПК G06F 7/68, 2006), который обеспечивает формирование выходной частоты, пропорциональной входному знакопеременному коду; содержащий первый двоичный умножитель, состоящий из первого двоичного счетчика и первого мультиплексора (n - число разрядов первого счетчика и число каналов первого мультиплексора), выходы разрядов первого двоичного счетчика соединены с соответствующими адресными входами первого мультиплексора, вход опорной частоты F0 преобразователя соединен со входом тактирования первого двоичного умножителя, вход тактирования первого двоичного умножителя одновременно является входом тактирования первого двоичного счетчика и нулевым информационным входом первого мультиплексора, разряды цифрового входа первого двоичного умножителя одновременно являются соответствующими информационными входами первого мультиплексора, информационные входы входного преобразуемого кода Nпр со второго по n-й соединены со входами соответствующих разрядов цифрового входа первого двоичного умножителя, выход первого двоичного умножителя одновременно является выходом первого мультиплексора, второй двоичный умножитель, аналогичный первому двоичному умножителю, первый и второй инверторы для инверсии старших разрядов входного преобразуемого кода Nпр и входного корректирующего кода Nкорр и устройство мультиплексирования выходных сигналов двоичных умножителей, включающее в себя третий инвертор, третий мультиплексор, третий двоичный счетчик, первый, второй и третий компараторы, элемент И, старший разряд a1 входного преобразуемого кода Nпр соединен со входом первого инвертора, выход первого инвертора соединен со входом старшего разряда цифрового входа первого двоичного умножителя, разряды цифрового входа второго двоичного умножителя одновременно являются соответствующими информационными входами второго мультиплексора, разряды b2…bk входного корректирующего кода Nкорр соединены со входами соответствующих разрядов цифрового входа второго двоичного умножителя, а старший разряд b1 входного корректирующего кода Nкорр соединен со входом второго инвертора, выход второго инвертора соединен со входом старшего разряда цифрового входа второго двоичного умножителя, выходы разрядов второго двоичного счетчика соединены с соответствующими адресными входами второго мультиплексора, вход опорной частоты F0 преобразователя соединен со входом тактирования второго двоичного умножителя и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей, вход тактирования второго двоичного умножителя одновременно является входом тактирования второго двоичного счетчика и нулевым информационным входом второго мультиплексора, вход тактирования устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является третьим входом тактирования третьего двоичного счетчика, выход первого двоичного умножителя соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, выход второго двоичного умножителя одновременно является выходом второго мультиплексора, первый частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно первым входом третьего мультиплексора, второй частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно вторым входом третьего мультиплексора, выход второго двоичного умножителя соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, нулевой информационный вход третьего мультиплексора соединен с выходом элемента "И", выход третьего мультиплексора одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей и выходом преобразователя, счетный выход третьего двоичного счетчика соединен с первой входной шиной первого, второго и третьего компараторов, выход первого компаратора соединен с первым входом разрешения счета третьего двоичного счетчика и со входом третьего инвертора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной первого компаратора, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной второго компаратора, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной третьего компаратора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой С, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой E, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой G, выход второго компаратора соединен с первым входом элемента "И", выход третьего компаратора соединен со вторым входом элемента "И", выход третьего инвертора соединен со вторым входом сброса третьего двоичного счетчика.

Недостатками прототипа являются его ограниченные функциональные возможности, а именно схемно-конструктивно не предусмотрена возможность нелинейного преобразования знакопеременных кодов в частоту, так как он предназначен только для линейного преобразования кода в частотно-импульсную последовательность.

Технический результат предлагаемого изобретения направлен на расширение функциональных возможностей, а именно на реализацию нелинейного (функционального) преобразования знакопеременного кода в частоту, достигаемый за счет использования двух искусственных нейронных сетей, обеспечивающих реализацию нелинейной зависимости для входных преобразуемого и корректируемого кодов. Использование блоков памяти весовых коэффициентов для нейронных сетей позволяет использовать один и тот же преобразователь для реализации различных функциональных зависимостей выходной частоты от входного кода.

Технический результат достигается тем, что в преобразователь кода в частоту, содержащий первый двоичный умножитель, состоящий из первого двоичного счетчика и первого мультиплексора (n - число разрядов первого счетчика и число каналов первого мультиплексора), выходы разрядов первого двоичного счетчика соединены с соответствующими адресными входами первого мультиплексора, вход опорной частоты F0 преобразователя соединен со входом тактирования первого двоичного умножителя, вход тактирования первого двоичного умножителя одновременно является входом тактирования первого двоичного счетчика и нулевым информационным входом первого мультиплексора, разряды цифрового входа первого двоичного умножителя одновременно являются соответствующими информационными входами первого мультиплексора, информационные входы входного преобразуемого кода Nпр соединены с информационными входами первой искусственной нейронной сети, входы весовых коэффициентов d - количество весовых коэффициентов первой искусственной нейронной сети) первой искусственной нейронной сети соединены с выходами первого блока памяти весовых коэффициентов, адресные входы первого блока памяти весовых коэффициентов соединены с первой шиной адреса S1A весовых коэффициентов, предназначенных для загрузки в первую искусственную нейронную сеть, информационные входы первого блока памяти весовых коэффициентов соединены с первой шиной данных S1D весовых коэффициентов, предназначенных для загрузки в первую искусственную нейронную сеть, вход разрешения записи we1, первого блока памяти весовых коэффициентов соединен с первым входом разрешения записи we и информационные выходы Ny1 первой искусственной нейронной сети со второго по n-й соединены со входами соответствующих разрядов цифрового входа первого двоичного умножителя, выход первого двоичного умножителя одновременно является выходом первого мультиплексора, второй двоичный умножитель, аналогичный первому двоичному умножителю, первый и второй инверторы для инверсии старших разрядов выходного значения Ny1 первой искусственной нейронной сети и выходного значения Ny2 второй искусственной нейронной сети и устройство мультиплексирования выходных сигналов двоичных умножителей, включающее в себя третий инвертор, третий мультиплексор, третий двоичный счетчик, первый, второй и третий компараторы, элемент И, старший разряд a1 выходного значения Ny1 первой искусственной нейронной сети соединен со входом первого инвертора, выход первого инвертора соединен со входом старшего разряда цифрового входа первого двоичного умножителя, информационные входы входного корректирующего кода Nкорр соединены с информационными входами второй искусственной нейронной сети, входы весовых коэффициентов d - количество весовых коэффициентов второй искусственной нейронной сети) соединены с выходами второго блока памяти весовых коэффициентов, адресные входы второго блока памяти весовых коэффициентов соединены со второй шиной адреса S2A весовых коэффициентов, предназначенных для загрузки во вторую искусственную нейронную сеть, информационные входы второго блока памяти весовых коэффициентов соединены со второй шиной данных S2D весовых коэффициентов, предназначенных для загрузки во вторую искусственную нейронную сеть, вход разрешения записи we второго блока памяти весовых коэффициентов соединен со вторым сигналом разрешения записи we2, разряды цифрового входа второго двоичного умножителя одновременно являются соответствующими информационными входами второго мультиплексора, разряды b2…bk выходного значения Ny2 второй искусственной нейронной сети соединены со входами соответствующих разрядов цифрового входа второго двоичного умножителя, а старший разряд b1 выходного значения Ny2 второй искусственной нейронной сети соединен со входом второго инвертора, выход второго инвертора соединен со входом старшего разряда цифрового входа второго двоичного умножителя, выходы разрядов второго двоичного счетчика соединены с соответствующими адресными входами второго мультиплексора, вход опорной частоты F0 преобразователя соединен со входом тактирования второго двоичного умножителя и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей, вход тактирования второго двоичного умножителя одновременно является входом тактирования второго двоичного счетчика и нулевым информационным входом второго мультиплексора, вход тактирования устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является третьим входом тактирования третьего двоичного счетчика, выход первого двоичного умножителя соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, выход второго двоичного умножителя одновременно является выходом второго мультиплексора, первый частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно первым входом третьего мультиплексора, второй частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно вторым входом третьего мультиплексора, выход второго двоичного умножителя соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, нулевой информационный вход третьего мультиплексора соединен с выходом элемента "И", выход третьего мультиплексора одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей и выходом преобразователя, счетный выход третьего двоичного счетчика соединен с первой входной шиной первого, второго и третьего компараторов, выход первого компаратора соединен с первым входом разрешения счета третьего двоичного счетчика и со входом третьего инвертора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной первого компаратора, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной второго компаратора, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной третьего компаратора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой С, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой Е, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой G, выход второго компаратора соединен с первым входом элемента "И", выход третьего компаратора соединен со вторым входом элемента "И", выход третьего инвертора соединен со вторым входом сброса третьего двоичного счетчика, вводится первая искусственная нейронная сеть, вторая искусственная нейронная сеть, первый блок памяти весовых коэффициентов, второй блок памяти весовых коэффициентов, первая шина адреса S1A, первая шина данных S1D, вторая шина адреса S2A, вторая шина данных S2D, первый вход разрешения записи we1, второй вход разрешения записи we2, информационные входы входного преобразуемого кода Nпр соединены с информационными входами первой искусственной нейронной сети, входы весовых коэффициентов wj первой искусственной нейронной сети соединены с выходами первого блока памяти весовых коэффициентов, адресные входы первого блока памяти весовых коэффициентов соединены с первой шиной адреса S1A весовых коэффициентов, предназначенных для загрузки в первую искусственную нейронную сеть, информационные входы первого блока памяти весовых коэффициентов соединены с первой шиной данных S1D весовых коэффициентов, предназначенных для загрузки в первую искусственную нейронную сеть, вход разрешения записи we первого блока памяти весовых коэффициентов соединен с первым входом разрешения записи we1, информационные выходы Ny1 первой искусственной нейронной сети со второго по n-й соединены со входами соответствующих разрядов цифрового входа первого двоичного умножителя, старший разряд а1 выходного значения Ny1 первой искусственной нейронной сети соединен со входом первого инвертора, информационные входы входного корректирующего кода Nкорр соединены с информационными входами второй искусственной нейронной сети, входы весовых коэффициентов νj соединены с выходами второго блока памяти весовых коэффициентов, адресные входы второго блока памяти весовых коэффициентов соединены со второй шиной адреса S2A весовых коэффициентов, предназначенных для загрузки во вторую искусственную нейронную сеть, информационные входы второго блока памяти весовых коэффициентов соединены со второй шиной данных S2D весовых коэффициентов, предназначенных для загрузки во вторую искусственную нейронную сеть, вход разрешения записи we второго блока памяти весовых коэффициентов соединен со вторым сигналом разрешения записи we2, разряды b2…bk выходного значения Ny2 второй искусственной нейронной сети соединены со входами соответствующих разрядов цифрового входа второго двоичного умножителя, а старший разряд b1 выходного значения Ny2 второй искусственной нейронной сети соединен со входом второго инвертора.

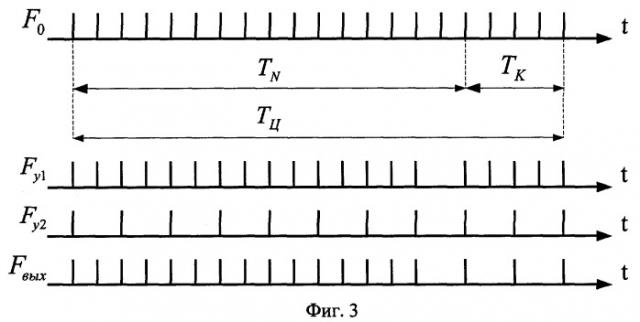

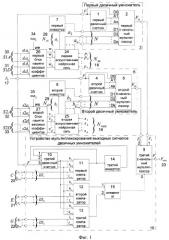

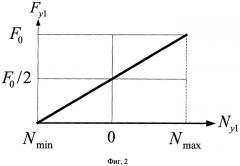

На фиг.1 представлена структурная схема предлагаемого преобразователя, на фиг.2 - график зависимости диапазона выходной частоты Fy1 первого двоичного умножителя от входного преобразуемого кода Nпр, на фиг.3 - временные диаграммы работы преобразователя.

Нейросетевой преобразователь кода в частоту содержит первый двоичный умножитель 3, второй двоичный умножитель 6, устройство мультиплексирования выходных сигналов двоичных умножителей 16, первый инвертор 7, второй инвертор 8, первую искусственную нейронную сеть 24, вторую искусственную нейронную сеть 25, первый блок памяти весовых коэффициентов 26, второй блок памяти весовых коэффициентов 27, входной преобразуемый код Nпр 18, входной корректирующий код Nкорр 19, вход опорной частоты преобразования F0 17, три входные константы С 20, E 21, G 22, вход первой шины адреса S1A 30, вход первой шины данных S1D 31, вход второй шины адреса S2A 32, вход второй шины данных S2D 33, первый вход разрешения записи we1 34, второй вход разрешения записи we2 35 и выходную частоту преобразователя Fвых 23.

Первая искусственная нейронная сеть 24 предназначена для реализации нелинейной зависимости входного преобразуемого кода Nпр=р1р2…pn-1pn 18 в код Ny1=a1a2…an-1an 28, который затем преобразуется в частоту Fy1 по линейному закону.

Первая искусственная нейронная сеть имеет входы весовых коэффициентов

вход преобразуемого кода Nпр 18 и выход кода

Ny1 28.

Вторая искусственная нейронная сеть 25 предназначена для реализации нелинейной зависимости входного корректирующего кода Nкорр=s1s21…sk-1sk

Nкорр 19 в код Ny2=b1b2…bk-1bk 29, который затем преобразуется в частоту Fy2 по линейному закону.

Вторая искусственная нейронная сеть имеет входы весовых коэффициентов вход корректирующего кода

Nкорр 19 и выход кода

Ny2 29.

Первый блок памяти весовых коэффициентов 26 предназначен для хранения значений весовых коэффициентов первой искусственной нейронной сети. Каждый весовой коэффициент wj представляет собой n-разрядный код.

Второй блок памяти весовых коэффициентов 27 предназначен для хранения значений весовых коэффициентов νj(j=1,2,…, d) второй искусственной нейронной сети. Каждый весовой коэффициент νj представляет собой k-разрядный код.

Первый инвертор 7 предназначен для обеспечения возможности преобразования знакопеременного кода Ny1 28, связанного со входным преобразуемым кодом Nпр 18 нелинейной зависимостью, в частоту Fy1, а именно для инверсии его старшего (знакового) разряда а1.

Второй инвертор 8 предназначен для обеспечения возможности преобразования знакопеременного кода Ny2 29, связанного со входным корректирующим кодом Nкорр 19 нелинейной зависимостью, в частоту Fy2, а именно для инверсии его старшего (знакового) разряда b1.

Вход опорной частоты преобразователя F0 17 соединен со входами тактирования первого 3 и второго 6 двоичных умножителей и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей 16. Информационные входы входного преобразуемого кода Nпр 18 соединены с информационными входами первой искусственной нейронной сети 24. Входы весовых коэффициентов первой искусственной нейронной сети 24 соединены с выходами первого блока памяти весовых коэффициентов 26. Адресные входы первого блока памяти весовых коэффициентов 26 соединены с первой шиной адреса S1A 30 весовых коэффициентов , предназначенных для загрузки в первую искусственную нейронную сеть 24. Информационные входы первого блока памяти весовых коэффициентов 26 соединены с первой шиной данных S1D 31 весовых коэффициентов , предназначенных для загрузки в первую искусственную нейронную сеть 24. Вход разрешения записи we первого блока памяти весовых коэффициентов соединен с первым входом разрешения записи we1 34. Информационные входы входного корректирующего кода Nкорр 19 соединены с информационными входами второй искусственной нейронной сети 25. Входы весовых коэффициентов νj второй искусственной сети 25 соединены с выходами второго блока памяти весовых коэффициентов 27. Адресные входы второго блока памяти весовых коэффициентов 27 соединены со второй шиной адреса S2A 32 весовых коэффициентов νj(j=1,2,…, d), предназначенных для загрузки во вторую искусственную нейронную сеть 25. Информационные входы второго блока памяти весовых коэффициентов 27 соединены со второй шиной данных S2D 33 весовых коэффициентов νj(j=1,2,…, d), предназначенных для загрузки во вторую искусственную нейронную сеть 25. Вход разрешения записи we второго блока памяти весовых коэффициентов соединен со вторым входом разрешения записи we2 35. Старший разряд a1 кода Ny1 18 соединен со входом первого инвертора 7, старший разряд b1 кода Ny2 19 соединен со входом второго инвертора 8. Выход первого инвертора 7, а также разряды а2…аn кода Ny1 28 соединены с соответствующими разрядами цифрового входа N первого двоичного умножителя 3. Выход второго инвертора 8, а также разряды b2…bk кода Ny2 29 соединены с соответствующими разрядами цифрового входа N второго двоичного умножителя 6. Выход первого двоичного умножителя 3 соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей 16. Выход второго двоичного умножителя 6 соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей 16. Входная константа С20 соединена с первой входной шиной Ш1 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Входная константа Е21 соединена со второй входной шиной Ш2 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Входная константа G22 соединена с третьей входной шиной Ш3 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Выход устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является выходной частотой Fвых 23 преобразователя.

Первый двоичный умножитель 3 содержит первый двоичный счетчик 1 и первый мультиплексор 2 (n - число разрядов первого счетчика и число каналов первого мультиплексора), вход тактирования F, цифровой вход N и частотный выход Fу1.

Вход тактирования F первого двоичного умножителя 3 одновременно является входом тактирования первого двоичного счетчика 1 и нулевым информационным входом D0 первого мультиплексора 2. Разряды a1…an цифрового входа N первого двоичного умножителя 3 одновременно являются информационными входами D1-Dn первого мультиплексора 2. Выходы разрядов первого двоичного счетчика 1 соединены с соответствующими адресными входами А1-Аn первого мультиплексора 2. Выход первого мультиплексора 2 одновременно является выходом первого двоичного умножителя 3.

Первый двоичный умножитель 3 осуществляет преобразование кода Ny1 28, связанного со входным преобразуемым кодом Nпр 18 нелинейной зависимостью, в частоту Fy1, пропорциональную знакопеременному коду Ny1=a1a2…an с интервалом неравномерности TN=2n (фиг. 3).

Второй двоичный умножитель 6 схемно-конструктивно аналогичен первому двоичному умножителю 3 и содержит второй двоичный счетчик 4 и второй мультиплексор 5 (k - число разрядов второго счетчика и число каналов второго мультиплексора), вход тактирования F, цифровой вход N и частотный выход Fy2.

Вход тактирования F второго двоичного умножителя 6 является одновременно входом тактирования второго двоичного счетчика 4 и нулевым информационным входом D0 второго мультиплексора 5. Разряды b1…bk цифрового входа N второго двоичного умножителя 6 одновременно являются информационными входами D1-Dk второго мультиплексора 5. Выходы разрядов второго двоичного счетчика 4 соединены с соответствующими адресными входами А1-Аk второго мультиплексора 5. Выход второго мультиплексора 5 одновременно является выходом второго двоичного умножителя 6.

Второй двоичный умножитель 6 осуществляет преобразование кода Ny2 29, связанного со входным корректирующим кодом Nкорр 19 нелинейной зависимостью, в частоту Fy2, пропорциональную знакопеременному корректирующему коду Ny2=b1b2…bk с интервалом неравномерности ТК=2k. Работа двоичных умножителей разнесена во времени. В результате интервал неравномерности преобразователя кода в частоту равен ТЦ=TN+ТК (фиг. 3).

Устройство мультиплексирования выходных сигналов двоичных умножителей 16 содержит третий двоичный счетчик 10, первый компаратор 11, второй компаратор 12, третий компаратор 13, третий инвертор 14, элемент "И" 15, третий мультиплексор 9 выполнен двухканальным, вход тактирования F, первый частотный вход F1, второй частотный вход F2, первую входную шину Ш1, вторую входную шину Ш2, третью входную шину Ш3 и выходную частоту преобразования Fy.

Третий двоичный счетчик 10 вычисляет номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя.

Первый компаратор 11 сравнивает номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя с константой С 20, равной TN+TK-1. Выходной сигнал первого компаратора 11 равен единице, если выходное значение третьего двоичного счетчика 10 меньше константы С 20. В противном случае выходной сигнал первого компаратора 11 равен нулю. Таким образом, первый компаратор 11 разрешает инкрементирование выходного значения третьего двоичного счетчика 10, пока оно не достигнет величины ТЦ.

Второй компаратор 12 сравнивает номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя с константой E 21, равной TN-1. Выходной сигнал второго компаратора 12 равен единице, если выходное значение третьего двоичного счетчика 10 больше константы E 21. В противном случае выходной сигнал второго компаратора 12 равен нулю.

Третий компаратор 13 сравнивает номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя с константой F 22, равной TN+TK. Выходной сигнал третьего компаратора 13 равен единице, если выходное значение третьего двоичного счетчика 10 меньше константы F 22. В противном случае выходной сигнал третьего компаратора 13 равен нулю.

Элемент "И" 15 выполняет объединение результатов сравнения второго 12 и третьего 13 компараторов. Выход элемента "И" 15 равен единице, если выходные значения второго 12 и третьего 13 компараторов равны единице. В противном случае выход элемента "И" 15 равен нулю. Третий двоичный счетчик 10, второй компаратор 12, третий компаратор 13 и элемент "И" 15 предназначены для формирования управляющего входа третьего мультиплексора 9.

Третий мультиплексор 9 осуществляет выбор выходной частоты преобразователя. Нулевой информационный вход третьего мультиплексора 9 является сигналом выбора. Когда сигнал на нулевом информационном входе третьего мультиплексора 9 равен нулю, на его выходе сигнал равен первому входному сигналу третьего мультиплексора 9. Когда сигнал на нулевом информационном входе третьего мультиплексора 9 равен единице, на его выходе сигнал равен второму входному сигналу третьего мультиплексора 9.

Вход тактирования F устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является входом тактирования третьего двоичного счетчика 10. Первый частотный вход F1 устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является первым входом третьего мультиплексора 9. Второй частотный вход F2 устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является вторым входом третьего мультиплексора 9. Нулевой информационный вход третьего мультиплексора 9 соединен с выходом элемента "И" 15. Выход третьего мультиплексора 9 одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей 16 и выходом устройства. Счетный выход третьего двоичного счетчика 10 соединен с первой входной шиной H=h1h2…hn+1 первого 11, второго 12 и третьего 13 компараторов. Выход первого компаратора 11 соединен с первым входом разрешения счета третьего двоичного счетчика 10 и входом третьего инвертора 14. Вторая входная шина L=l1l2…ln+1 первого компаратора 11 одновременно является первой входной шиной Ш1 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Вторая входная шина L=l1l2…ln+1 второго компаратора 12 одновременно является второй входной шиной Ш2 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Вторая входная шина L=l1l2…ln+1 третьего компаратора 13 одновременно является третьей входной шиной Ш3 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Выход второго компаратора 12 соединен с первым входом элемента "И" 15. Выход третьего компаратора 13 соединен со вторым входом элемента "И" 15. Выход третьего инвертора 14 соединен со вторым входом сброса третьего двоичного счетчика 10.

Устройство мультиплексирования выходных сигналов двоичных умножителей 16 осуществляет мультиплексирование выходных частот первого 3 и второго 6 двоичных умножителей, а именно вставляет в частотно-импульсный поток, пропорциональный входному преобразуемому коду Nпр 18 импульсы, пропорциональные входному корректирующему коду Nкорр 19.

Преобразователь работает следующим образом.

Пусть число разрядов n первого двоичного умножителя равно четырем, а число разрядов k второго двоичного умножителя равно двум (фиг. 3). Пусть в начальный момент времени первый 1, второй 4 и третий 10 двоичные счетчики находятся в нулевом состоянии. На вход 17 подается импульсная последовательность входной частоты F0. Первый 1, второй 4 и третий 10 двоичные счетчики могут изменять свои выходные значения только при появлении очередного импульса входной частоты F0 преобразователя.

Для загрузки новых весовых коэффициентов первой искусственной нейронной сети 24 на вход подтверждения записи we1 34 первого блока памяти весовых коэффициентов 26 необходимо подать сигнал we1=1. На первую шину адреса S1A 30 первого блока памяти весовых коэффициентов 26 подается адрес весового коэффициента. При этом на первую шину данных S1D 31 подается значение весового коэффициента. Первый блок памяти весовых коэффициентов 26 имеет число выходов, равное количеству весовых коэффициентов первой искусственной нейронной сети 24. В качестве устройства обучения искусственных нейронных сетей может выступать, например, персональный компьютер, формирующий значения адреса S1A 30 и данных S1D 31.

Для загрузки новых весовых коэффициентов второй искусственной нейронной сети 25 на вход подтверждения записи we2 35 второго блока памяти весовых коэффициентов 27 необходимо подать сигнал we2=1. На вторую шину адреса S2A 30 второго блока памяти весовых коэффициентов 27 подается адрес весового коэффициента. При этом на вторую шину данных S2D 33 подается значение весового коэффициента. Второй блок памяти весовых коэффициентов 27 имеет число выходов, равное количеству весовых коэффициентов второй искусственной нейронной сети 25.

На информационные входы первой искусственной нейронной сети 24 подается преобразуемый код Nпр 18. В соответствии с загруженными в первую искусственную нейронную сеть 24 значениями весовых коэффициентов wj с выхода первой искусственной нейронной сети 24 снимается код Ny1 28, находящийся по отношению к преобразуемому коду Nпр 18 в некоторой функциональной зависимости. На вход первого инвертора 7 подается старший (знаковый) разряд a1 кода Ny1 28, снимаемого с информационного выхода первой искусственной нейронной сети 24. Если а1=1, то на выходе первого инвертора 7 формируется сигнал, равный единице. Если а1=0, то на выходе первого инвертора 7 формируется сигнал, равный нулю. На информационные входы второй искусственной нейронной сети 25 подается корректирующий код Nкорр 19. На вход второго инвертора 8 подается старший (знаковый) разряд b1 кода

Ny2 29, снимаемого с информационного выхода второй искусственной нейронной сети 25. В соответствии с загруженными во вторую искусственную нейронную сеть 25 значениями весовых коэффициентов νj с выхода второй искусственной нейронной сети 24 снимается код Ny2 29, находящийся по отношению к преобразуемому коду

Nкорр 19 в некоторой функциональной зависимости. Если b1=1, то на выходе второго инвертора 8 формируется сигнал, равный единице. Если b1=0, то на выходе второго инвертора формируется сигнал, равный нулю. Таким образом, на цифровой вход первого двоичного умножителя 3 и соответствующие разряды информационного входа первого мультиплексора 2 подается код а на цифровой вход второго двоичного умножителя 6 и соответствующие разряды информационного входа второго мультиплексора 5 подается код . Разрядность первого двоичного счетчика 1 совпадает с разрядностью первого двоичного умножителя 3, а разрядность второго двоичного счетчика 4 совпадает с разрядностью второго двоичного умножителя 6. Таким образом, первый двоичный счетчик 1 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n-1=15. Второй же двоичный счетчик 4 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2k-1=3.

Выходные значения первого двоичного счетчика 1 являются адресными входами первого мультиплексора 2. Так, при выходном значении первого двоичного счетчика 1, равном "0", "2", "4", "6", "8", "10", "12" или "14", в выходную неравномерную последовательность импульсов Fy1, одновременно являющуюся выходом первого мультиплексора 2 и выходом первого двоичного умножителя 3, вставится импульс длительности верхнего фронта опорной частоты F0 преобразователя, если =1. При выходном значении первого двоичного счетчика 1, равном "1", "5", "9" или "13", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а2=1. При выходном значении первого двоичного счетчика 1, равном "3" или "11", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а3=1. При выходном значении первого двоичного счетчика 1, равном "7", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а4=1. Выходная последовательность импульсов Fy1 на выходе первого двоичного умножителя характеризуется частотой:

где n - количество разрядов преобразуемого кода Nпр;

f1 - линейная или нелинейная зависимость, связывающая выходной код Ny1 первой искусственной нейронной сети со входным преобразуемым кодом Nпр.

Выходная последовательность импульсов Fy1 на выходе первого двоичного умножителя характеризуется частотой, связанной с выходным кодом Ny1=а1а2…аn первой искусственной нейронной сети следующим образом: