Дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к технике аналогово-цифрового преобразования и может быть использовано в быстродействующих АЦП. Техническим результатом является увеличение быстродействия при сохранении малой потребляемой мощности покоя. Высокое быстродействие усилителя при разомкнутой цепи отрицательной обратной связи, при малом приращении входного сигнала над опорным и при сохранении малой потребляемой мощности покоя достигается за счет предварительного выравнивания потенциалов усилительных ветвей за счет включения выравнивающего транзисторного ключа, а затем при компарировании включения ускоряющих положительных обратных связей. 2 ил.

Реферат

Изобретение относится к технике аналогово-цифрового преобразования и может быть использовано в быстродействующих АЦП.

Известна схема дифференциального усилителя на биполярных транзисторах для быстродействующего аналогово-цифрового преобразователя сигналов, описанная в патенте США 3843934, J.N.Giles "High Speed Transistor Difference Amplifier", October 22 1974. Недостатком этой схемы является большая потребляемая мощность.

Наиболее близким аналогом к заявленному изобретению является схема, описанная в IEEE Journal of Solid-State Circuits, v.24, № 2, Apr. 1989, S.R.Norsworthy и др. "A 14-bit 80 kHz Sigma-Delta A/D Converter: Modeling, Design, and Performance Evaluation", содержащая входную и режимную части, две усилительные и две выходные ветви усилителя, два транзисторных источника тока, подключенных истоками к напряжению питания, затворами к напряжению смещения, стоками к усилительным и выходным ветвям.

Недостатком этой схемы является малое быстродействие при работе в режиме компаратора при разомкнутой цепи отрицательной обратной связи и при малом приращении входного сигнала над опорным уровнем.

Техническим результатом настоящего изобретения является увеличение быстродействия при сохранении малой потребляемой мощности покоя.

Указанный результат достигается за счет того, что в известном устройстве схемы дифференциального усилителя, содержащем входную и режимную части, две усилительные и две выходные ветви усилителя, два источника тока на транзисторах первого типа проводимости, подключенные истоками к напряжению питания, затворами к напряжению смещения, стоками к усилительным и выходным ветвям, предложено:

- между стоками транзисторов источников тока включить транзисторный ключ, уравнивающий во включенном состоянии их потенциалы,

- между источником напряжения смещения и затворами транзисторов источников тока включить два транзисторных ключа первого типа проводимости, другие два транзисторных ключа комплементарной первому типа проводимости включить соответственно между стоком транзистора одного источника тока и затвором транзистора другого источника тока попарно, а затворы транзисторов четырех последних указанных транзисторных ключей объединить и подключить к управляющему электроду.

Высокое быстродействие усилителя при разомкнутой цепи отрицательной обратной связи, при малом приращении входного сигнала над опорным и при сохранении малой потребляемой мощности покоя, достигается за счет предварительного выравнивания потенциалов усилительных ветвей, а затем при компарировании включения ускоряющих положительных обратных связей.

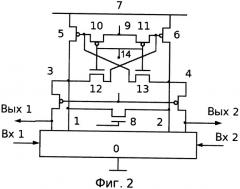

Перечень графических материалов, иллюстрирующих устройство, реализующее заявляемое изобретение:

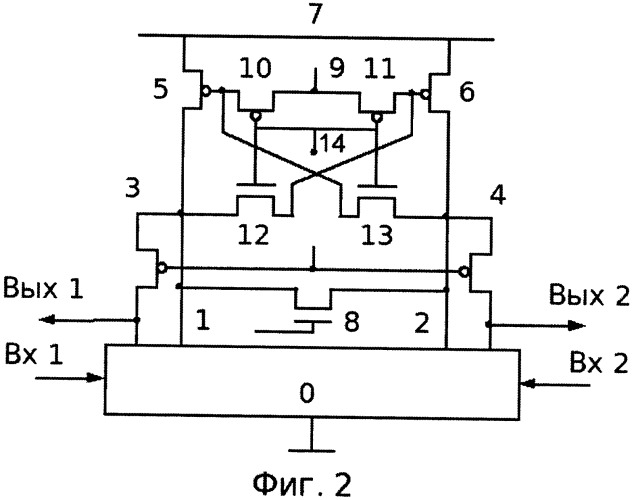

Фиг.1 иллюстрирует известное устройство дифференциального усилителя компаратора (прототип).

Фиг.2 показывает электрическую схему предлагаемого устройства.

Предлагаемый дифференциальный усилитель содержит входную и режимную части (0), две усилительные (1, 2) и две выходные (3, 4) ветви усилителя, два транзисторных источника тока (5, 6), подключенных истоками к напряжению питания (7), стоками к усилительным (1, 2) и выходным (3, 4) ветвям, между стоками источников тока включен транзисторный ключ (8), уравнивающий во включенном состоянии их потенциалы, между источником смещения (9) и затворами источников тока (5, 6) включены два транзисторных ключа (10, 11) первого типа проводимости, между стоком одного источника тока и затвором второго включены попарно два транзисторных ключа (12, 13) комплементарного первому типа проводимости, причем затворы четырех последних указанных транзисторных ключей (10, 11, 12, 13) объединены и подключены к управляющему электроду (14).

Схема работает следующим образом:

Сначала перед тактом компарирования включается ключ (8) для выравнивания потенциалов ветвей усилителя. Затем при компарировании ключи (8), (10, 11) выключаются, а ключи (12, 13) включаются, работают положительные обратные связи и усиление сигнала ускоряется. При токе потребления 2-5 мкА в предлагаемом усилителе достигается постоянная времени 5-10 нс.

Настоящее описание изобретения, в т.ч. состава и работы устройства, включая предлагаемый вариант его исполнения, предполагает его дальнейшее возможное совершенствование специалистами и не содержит каких-либо ограничений в части реализации. Все притязания сформулированы исключительно в формуле изобретения.

Дифференциальный усилитель, содержащий входную и режимную части, две усилительные и две выходные ветви, два источника тока на транзисторах первого типа проводимости, подключенные истоками к напряжению питания, а стоками к усилительным и выходным ветвям, отличающийся тем, что между стоками транзисторов источников тока включен транзисторный ключ, уравнивающий во включенном состоянии их потенциалы, между источником напряжения смещения и затворами транзисторов источников тока включены два транзисторных ключа первого типа проводимости, другие два транзисторных ключа комплементарной первому типу проводимости включены соответственно между стоком транзистора одного источника тока и затвором транзистора другого источника тока, причем затворы транзисторов четырех последних указанных транзисторных ключей объединены и подключены к управляющему электроду.