Интегральная схема с адаптивным отбором по скорости

Иллюстрации

Показать всеИзобретение относится к электронике и может быть использовано в системах для регулировки интегральной микросхемы. Технический результат - повышение точности настройки. Раскрыты системы и методы, которые относятся к настройке частоты электронного устройства, содержащего интегральную схему и электронный компонент, таким образом, чтобы улучшать производительность. Интегральная схема определяет набор схем распределения частот, каждая из которых соответствует распределению самых высоких значений прохождения диапазона задержек, и одной частоты из набора частот, при которой электронное устройство может работать. Основываясь на взаимодействии с электронным компонентом, интегральная схема реализует предпочтительную схему распределения частот. 3 н. и 26 з.п. ф-лы, 8 ил.

Реферат

Предшествующий уровень техники

Притязание на приоритет по §119 раздела 35 кодекса законов США

Настоящая заявка на патент испрашивает приоритет предварительной патентной заявки № 60/625223 под названием "Интегральная схема с адаптивным отбором по скорости" от 5 ноября 2004 г., и переуступленной ее правопреемнику, и тем самым явно включенной здесь путем ссылки.

Область техники, к которой относится изобретение

Настоящее изобретение относится к системам и методам регулировки интегральной схемы для электронного компонента.

Предшествующий уровень техники

Интегральные схемы революционизировали электронную промышленность, обеспечивая возможность новых применений, которые не были возможны с дискретными устройствами. Интегрирование позволяет сложные схемы, состоящие из миллионов электронных компонентов, размещать на единственном кристалле из полупроводникового материала. Кроме того, интегрирование предлагает преимущества изготовления сотен кристаллов на единственной кремниевой подложке, что значительно снижает стоимость и повышает надежность каждой из готовых схем.

Интегральные схемы в настоящее время широко используются в электронных устройствах, реализовывая усложненные схемы, такие как процессоры общего назначения и конкретного применения. Контроллер, интегрированный в кристалл, может использоваться для осуществления сопряжения различных процессоров с компонентами вне кристалла, такими как внешнее запоминающее устройство и т.п. Синхронизирующие импульсы, генерируемые контроллером, могут использоваться для доступа к этим компонентам вне кристалла. Эти синхронизирующие импульсы должны действовать с определенной номинальной частотой следования в пределах некоторого разрешенного допустимого отклонения, чтобы гарантировать, что контроллер сможет осуществлять связь с компонентами вне кристалла при условиях наихудшего случая температурного режима и напряжения.

Из-за процессов, присущих процессу изготовления на кремниевой подложке, набор кристаллов, производимых из одной подложки, может относиться к диапазону различных номинальных значений производительности. В зависимости от применения, некоторые изготовители вынуждены отбраковывать медленнодействующие кристаллы и быстродействующие кристаллы, которые находятся вне номинального диапазона допустимых значений. Это ведет к большим количествам отходов, которые могут быть очень дорогостоящими.

В попытке сохранить те участки подложки, которые не производят номинальные кристаллы, некоторые изготовители применяют способ сортировки (отбора) по скорости, при котором различные кристаллы, произведенные из единственной подложки, проверяют и группируют в соответствии с их номинальной производительностью. Этот способ группирования кристаллов в соответствии с их скоростью работы потребляет много времени и является дорогостоящим. Помимо этого, они несут убытки в результате продажи медленных кристаллов и быстрых кристаллов по пониженным ценам.

Отбор по скорости представляет собой относительно статический, передовой процесс, который является в общем полезным в характеризации технических характеристик интегральной схемы. Но после этого нет никакой возможности для интегральной схемы оптимизировать ее собственные рабочие характеристики или эксплуатационные параметры в зависимости от внешнего устройства.

Сущность изобретения

В одном аспекте изобретения электронное устройство включает в себя электронный компонент и интегральную схему, сконфигурированную так, чтобы генерировать системные синхронизирующие импульсы, имеющие программируемую частоту, и внешние синхронизирующие импульсы, имеющие программируемую задержку относительно системных синхронизирующих импульсов, причем интегральная схема дополнительно сконфигурирована так, чтобы обеспечивать внешние синхронизирующие импульсы для электронного компонента, определять диапазон задержек между системными синхронизирующими импульсами и внешними синхронизирующими импульсами, при которых интегральная схема и электронный компонент могут обмениваться данными, и программировать частоту системных синхронизирующих импульсов, основываясь на диапазоне задержек.

В другом аспекте изобретения способ приспосабливания интегральной схемы к электронному компоненту включает в себя генерирование системных синхронизирующих импульсов, имеющих программируемую частоту, и внешних синхронизирующих импульсов, имеющих программируемую задержку относительно системных синхронизирующих импульсов, обеспечение внешних синхронизирующих импульсов для электронного компонента, определение диапазона задержек между системными синхронизирующими импульсами и внешними синхронизирующими импульсами, при которых интегральная схема и электронный компонент могут сообщаться, и программирование частоты системных синхронизирующих импульсов в зависимости от диапазона задержек.

В другом аспекте изобретения электронное устройство включает в себя электронный компонент и интегральную схему, содержащую средство для генерирования системных синхронизирующих импульсов, имеющих программируемую частоту, средство для генерирования внешних синхронизирующих импульсов, имеющих программируемую задержку относительно системных синхронизирующих импульсов, и средство для обеспечения внешних синхронизирующих импульсов для электронного компонента, причем интегральная схема дополнительно включает в себя средство для определения диапазона задержек между системными синхронизирующими импульсами и внешними синхронизирующими импульсами, при которых интегральная схема и электронный компонент могут обмениваться данными, и средство для программирования частоты системных синхронизирующих импульсов, основываясь на диапазоне задержек.

Должно быть понятно, что специалистам в данной области техники из последующего подробного описания станут очевидны другие варианты осуществления настоящего изобретения, в котором различные варианты осуществления изобретения показаны и описаны посредством иллюстраций. Как должно быть понятно, изобретение допускает другие и различные варианты осуществления, а его отдельные детали допускают модификацию в различных других отношениях, не выходя при этом за рамки объема и сущности настоящего изобретения. Соответственно, чертежи и подробное описание следует рассматривать как иллюстративные по их характеру, а не как ограничительные.

Краткое описание чертежей

Аспекты настоящего изобретения иллюстрируются посредством примера, а не посредством ограничения, на прилагаемых чертежах, на которых:

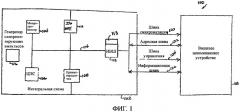

фиг.1 - концептуальная блок-схема, иллюстрирующая пример электронного устройства, использующего интегральную схему;

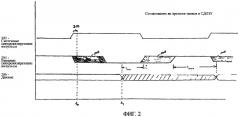

фиг.2 - временная диаграмма, иллюстрирующая пример согласования во времени параметров для записи в запоминающем устройстве вне кристалла;

фиг.3 - временная диаграмма, иллюстрирующая пример согласования во времени параметров для считывания с запоминающего устройства вне кристалла;

фиг.4 - функциональная блок-схема, иллюстрирующая пример работы контроллера;

фиг.5 - блок-схема процесса, иллюстрирующая пример способа определения схем распределения частот;

фиг.6 - график, показывающий распределения СВЗП (самое высокое значение прохождения) в зависимости от частоты;

фиг.7 - блок-схема процесса, иллюстрирующая алгоритм калибровки, используемый для определения СВЗП;

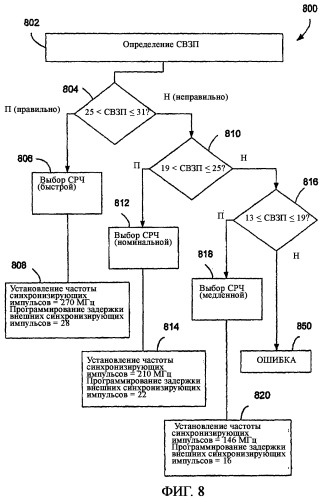

фиг.8 - репрезентативная блок-схема процесса, иллюстрирующая пример алгоритма адаптивного отбора по скорости.

Подробное описание

Подробное описание, сформулированное ниже в связи с прилагаемыми чертежами, предназначено в качестве описания различных вариантов осуществления настоящего изобретения и не предназначено для представления только тех вариантов осуществления, в которых настоящее изобретение может быть осуществлено на практике. Подробное описание включает в себя определенные подробности с целью обеспечения полного понимания настоящего изобретения. Однако специалистам в данной области техники должно быть понятно, что настоящее изобретение может быть осуществлено на практике без этих определенных подробностей. В некоторых примерах известные конструкции и устройства показаны в форме блок-схемы, чтобы избегать затенения концепций настоящего изобретения. Акронимы и другая описательная терминология могут использоваться просто для удобства и ясности и не предназначены для ограничения объема изобретения.

В последующем подробном описании различные аспекты настоящего изобретения могут быть описаны в контексте интегральной схемы, сконфигурированной для подсоединения по меньшей мере к одному устройству хранения данных. Интегральной схемой может быть, например, интегральная схема прикладной ориентации (ИСПО), содержащая по меньшей мере один процессор. Устройством хранения данных может быть, например, синхронное динамическое оперативное запоминающее устройство (СДОЗУ) или подобное устройство. Хотя эти обладающие признаками изобретения аспекты могут хорошо подходить для использования с этими компонентами, специалистам в данной области техники должно быть понятно, что эти обладающие признаками изобретения аспекты аналогичным образом могут подходить для использования в различных других электронных устройствах или компонентах. Соответственно, любая ссылка на конкретный тип интегральной схемы или компонента (например, внешнее запоминающее устройство или запоминающее устройство вне кристалла) предназначена только для иллюстрирования обладающих признаками изобретения аспектов, с пониманием того, что такие обладающие признаками изобретения аспекты имеют широкий диапазон применений.

Фиг. 1 представляет концептуальную блок-схему электронного устройства 100, которое использует интегральную схему 102, такую как ИСПО. Фиг. 1 не должна рассматриваться как требующая какого-либо конкретного фактического размещения электронного устройства 100. Интегральная схема 102 может включать в себя микропроцессор 104, цифровой процессор сигналов (ЦПС) 106, приемопередатчик 108, интерфейс 110 ввода/вывода (ВВОДА/ВЫВОДА) и интерфейс внешний шины (ИВШ) 112. Все эти компоненты могут быть соединены вместе с помощью внутренней системной шины (ВСШ) 114. Генератор 116 синхронизирующих импульсов может использоваться для генерирования системного синхронизирующего сигнала (или "системных синхронизирующих импульсов") для согласования во времени системы. Частота системных синхронизирующих импульсов может быть программируемой.

Микропроцессор 104 может использоваться как платформа, чтобы выполнять прикладные программы, которые, помимо всего прочего, обеспечивают функции управления для пользователя и управления всей системой для электронного устройства 100. ЦПС 106 может быть реализован с внедренным уровнем программного обеспечения связи, который выполняет алгоритмы, конкретные для приложений, чтобы снижать потребности в обработке на микропроцессоре 104. Приемопередатчик 108 может использоваться для обеспечения доступа к внешней среде, такой как радиолиния в случае беспроводного телефона, терминала, устройства для электронной почты или устройства с поддержкой "всемирной паутины", например персонального цифрового ассистента (ПЦА), или другого подобного устройства. В некоторых вариантах осуществления приемопередатчик 108 может обеспечивать доступ к локальной сети Ethernet, кабельной модемной линии, волоконно-оптическому кабелю, цифровой абонентской линии (ЦАЛ), коммутируемой телефонной сети общего пользования (КСОП) или любой другой среде для связи. В других вариантах осуществления электронное устройство может быть автономным, без приемопередатчика для поддерживания внешней связи. Интерфейс 110 ВВОДА/ВЫВОДА может использоваться, чтобы поддерживать различные пользовательские интерфейсы. Пользовательские интерфейсы могут включать в себя клавиатуру, "мышь", сенсорный экран, звуковой громкоговоритель или наушники, микрофон, камеру и/или подобное устройство.

ИВШ 112 может использоваться для обеспечения доступа между компонентами на ВСШ 114. ИВШ 112 может включать в себя контроллер 113, который обеспечивает сопряжение между ВСШ 114 и другими электронными компонентами, например, одним или больше компонентами вне кристалла, такими как внешнее запоминающее устройство 118. Интерфейс может включать в себя шину 120 синхронизации, адресную шину 122, шину 124 управления и информационную шину 126. Хотя это не показано, ИВШ 112 также может обеспечивает сопряжение с жидкокристаллическим дисплеем (ЖКД) и/или другими пользовательскими устройствами сопряжения.

В последующем описании электронного устройства внешнее запоминающее устройство 118 будет представлено СДОЗУ. Однако, как должно быть понятно специалистам в данной области техники, различные концепции, описанные в данном описании, могут быть распространены на другие компоненты вне кристалла, включая, в качестве примера, другие запоминающие устройства, такие как разделенный на части элемент ИЛИ-НЕ, разделенное на части ПСОЗУ (параметрическое статическое оперативное запоминающее устройство), ОЗУ (оперативное запоминающее устройство), ПЗУ (постоянное запоминающее устройство), ППЗУ (программируемое ПЗУ), ЭСППЗУ (электрически стираемое ППЗУ), ВОЗУ (видео-ОЗУ) или любой другой компонент запоминающего устройства, или устройство, или матрицу запоминающих устройств. Контроллер 113 может использоваться для генерирования внешнего синхронизирующего сигнала (или "внешних синхронизирующих импульсов") и синхронизирующего сигнала обратной связи (или "синхронизирующих импульсов обратной связи"), в зависимости от системных синхронизирующих импульсов от генератора 116 синхронизирующих импульсов. Внешние синхронизирующие импульсы можно обеспечивать для СДОЗУ через шину 120 синхронизации для считывания и записи во внешнем запоминающем устройстве 118, после этого в СДОЗУ 118. Синхронизирующие импульсы обратной связи могут использоваться контроллером 113 для считывания выборочных данных из СДОЗУ 118.

Пример требований к согласованию во времени для записи в СДОЗУ 118 показан на фиг. 2. Внешние синхронизирующие импульсы, которые представлены внешними синхронизирующими импульсами 204, могут задерживаться относительно системных синхронизирующих импульсов, которые представлены системными синхронизирующими импульсами 202. Данные, подлежащие записи в СДОЗУ 118, представлены данными (или сигналом данных) 206 и могут быть переданы на информационную шину 120 (см. фиг. 1) от контроллера 113 вскоре после перехода системных синхронизирующих импульсов в момент времени t0. Небольшая задержка 210 между переходом системных синхронизирующих импульсов и t0 обусловлена задержкой распространения от контроллера 113. Информационная шина 120 (см. фиг. 1) прибавляет дополнительную задержку распространения, приводя к тому, что данные 206 достигают входа в СДОЗУ в момент времени t1. Данные на входе в СДОЗУ показаны на фиг. 2 с помощью штрихования данных 206.

Чтобы гарантировать надежную работу, данные 206 должны быть стабильными на входе в СДОЗУ 118 в течение короткого периода времени перед тактовым переходом (переходом внешних синхронизирующих импульсов). Это называется "минимальное время подготовки к работе" и обозначено на фиг. 2 как tподг. Также имеется период времени, когда данные 206 должны оставаться стабильными после перехода внешних синхронизирующих импульсов, то есть после tподг. Это называется "минимальное время удержания" и обозначено на фиг. 2 как tудерж. Если минимальные время подготовки к работе и время удержания не удовлетворяют этому требованию, то операцию записи в СДОЗУ гарантировать нельзя. Таким образом, можно легко заметить на фиг. 2, что имеется требование к минимальной задержке между системными синхронизирующими импульсами 202 и внешними синхронизирующими импульсами 204, чтобы удовлетворять требованию минимального времени подготовки к работе и к максимальной задержке между ними, чтобы удовлетворять требованию минимального времени удержания. Задержка может быть программируемой и может быть установлена где-нибудь между этими граничными значениями, как показано на фиг.2 затененным участком 208 внешних синхронизирующих импульсов 204.

Пример требований к согласованию во времени для считывания с СДОЗУ 118 показан на фиг. 3. Как пояснялось ранее в связи с фиг.2, внешние синхронизирующие импульсы 204 могут задерживаться относительно системных синхронизирующих импульсов 202. Синхронизирующие импульсы 302 обратной связи также могут задерживаться относительно системных синхронизирующих импульсов 202, как показано на фиг.3. Синхронизирующие импульсы 302 обратной связи могут использоваться для считывания данных с СДОЗУ 118 в контроллер 113. Данные 206 могут быть переданы из СДОЗУ 118 на информационную шину 120 (см. фиг. 1) вскоре после перехода внешних синхронизирующих импульсов 204 в момент времени t0. Из-за задержки распространения сигнала СДОЗУ 118 и информационной шины 120 (см. фиг. 1) данные 206 достигают входа в контроллер 113 в момент времени t1. Данные на входе в контроллер 113 (которые показаны с помощью штрихования данных 206) должны оставаться стабильными в течение короткого периода времени перед переходом синхронизирующих импульсов обратной связи. Этот период времени определен минимальным временем tподг подготовки к работе контроллера 113.

Данные 206 также должны оставаться стабильными после перехода синхронизирующих импульсов 302 обратной связи в течение периода времени, определяемого минимальным временем tудерж удержания контроллера 113. Как только данные считываются в контроллер 113 с переходом синхронизирующих импульсов 302 обратной связи, они могут быть подвергнуты повторной выборке с помощью системных синхронизирующих импульсов. Процесс повторной выборки имеет свои собственные требования, включающие в себя минимальное время подготовки к работе, в течение которого выборочные данные должны оставаться стабильными перед следующим переходом системных синхронизирующих импульсов 202. Таким образом, можно легко заметить на фиг. 3, что имеется потребность в минимальной задержке между системными синхронизирующими импульсами 202 и синхронизирующими импульсами 302 обратной связи, чтобы удовлетворять требованию минимального времени подготовки к работе, и в максимальной задержке между ними, чтобы удовлетворять требованию минимального времени удержания и времени подготовки к повторной выборке. Задержка может быть программируемой на контроллере 113 и может быть установлена где-нибудь между этими граничными значениями, как показано на фиг. 3 затененным участком 304.

Фиг.4 представляет функциональную блок-схему варианта осуществления контроллера 113. В показанном варианте осуществления контроллер 113 может быть разделен на синхронный контроллер 402 и асинхронный контроллер 404. Это разделение представляет собой просто предпочтение конструкции, и специалистам в данной области техники должно быть понятно, что можно использовать любую конфигурацию для выполнения различных функций, описываемых на протяжении всего этого раскрытия. Контроллеры 402 и 404 могут быть сконфигурированы для осуществления сопряжения адресной шины 122, шины 124 управления и информационной шины 126 с ВСШ 114 с помощью средства, известного в технике.

Контроллер 113 может использоваться, чтобы генерировать внешние синхронизирующие импульсы 204 и синхронизирующие импульсы 302 обратной связи. Мультиплексор 408 может использоваться, чтобы выбирать соответствующие системные синхронизирующие импульсы 202 в зависимости от того, подвергаются ли данные 206 тактовому выходу от синхронного или асинхронного контроллера. В показанном варианте осуществления, мультиплексор 408 может быть установлен для выбора системных синхронизирующих импульсов, используемых синхронным контроллером 402, для осуществления сопряжения к СДОЗУ 118. Логический элемент "исключающее ИЛИ" 410 может использоваться для обеспечения гибкости благодаря использованию либо инвертированных, либо неинвертированных системных синхронизирующих импульсов 202, чтобы генерировать внешние синхронизирующие импульсы и синхронизирующие импульсы обратной связи. Программируемый элемент 412 задержки может использоваться для установления задержки внешних синхронизирующих импульсов 204. Управление мультиплексором и логическим элементом "исключающее ИЛИ", также как задержка внешних синхронизирующих импульсов, могут быть запрограммированы, например, с помощью программного обеспечения, выполняемого на микропроцессоре 104, или с помощью любого другого средства. Драйвер 414 шины может использоваться, чтобы обеспечивать внешние синхронизирующие импульсы 204 для СДОЗУ 118.

Синхронизирующие импульсы 302 обратной связи могут генерироваться либо из системных синхронизирующих импульсов 202, либо из внешних синхронизирующих импульсов 204. В описываемом варианте осуществления и те, и другие синхронизирующие импульсы можно передавать на мультиплексор 416, чтобы обеспечивать некоторую эксплуатационную гибкость программисту программного обеспечения. Выбранные системные синхронизирующие импульсы можно передавать в логический элемент "исключающее ИЛИ" 418. Логический элемент "исключающее ИЛИ" 418 позволяет использовать либо инвертированные, либо неинвертированные синхронизирующие импульсы. Программируемый элемент 420 задержки может использоваться, чтобы задерживать синхронизирующие импульсы обратной связи. Синхронизирующие импульсы 302 обратной связи могут затем подаваться обратно на контроллеры 402 и 404. Управление мультиплексором и логическим элементом "исключающее ИЛИ", также как задержка синхронизирующих импульсов обратной связи, могут быть запрограммированы с помощью программного обеспечения, выполняемого на микропроцессоре 104, или с помощью любого другого средства.

Как обсуждалось ранее, некоторые ограничения согласования во времени, накладываемые контроллером 113 и СДОЗУ 118, могут ограничивать возможные установочные параметры для задержки для внешних синхронизирующих импульсов и синхронизирующих импульсов обратной связи. Установочный параметр задержки для внешних синхронизирующих импульсов, например, может ограничиваться минимальным временем подготовки к работе и удержания для СДОЗУ 118. Точно так же, установочный параметр задержки для синхронизирующих импульсов обратной связи может ограничиваться минимальным временем подготовки к работе, удержания и подготовки к повторной выборке для контроллера. Эти ограничения согласования во времени могут изменяться с технологическим процессом, температурой и напряжением.

Установочные параметры для задержки для внешних синхронизирующих импульсов и синхронизирующих импульсов обратной связи могут быть запрограммированы во время процедуры определения параметров до отправки интегральных схем, например, на заводе. Этот процесс может влечь за собой сбор данных определения параметров для интегральной схемы на протяжении изменений технологического процесса, напряжения и температуры. Установочные параметры для задержки затем могут быть вычислены при анализе самого плохого случая исходя из данных определения параметров и технических требований к согласованию во времени для внешнего устройства. Эти вычисленные установочные параметры для задержки могут использоваться как предварительно запрограммированные задержки для калибровки программируемых элементов задержки в контроллере для таких интегральных схем перед отправкой.

Дополнительно, на максимальную частоту системных синхронизирующих импульсов (упоминаемую как "FMAX") могут быть наложены ограничения, чтобы предотвращать ошибки, вызываемые системными синхронизирующими импульсами, проходящими быстрее, чем могут приспосабливаться конкретная интегральная схема и компонент вне кристалла на месте. Как правило, когда наложены ограничения на FMAX, они имеют тенденцию заставлять системные синхронизирующие импульсы работать на относительно медленной частоте, чтобы вместить самый широкий возможный диапазон электронных устройств. Этот подход предварительного программирования задержек и FMAX может работать весьма неплохо для одной конкретной части процесса, но не может хорошо работать для других. Например, в случаях, где определенное электронное устройство может функционировать на более высокой частоте, наличие FMAX, предварительно запрограммированной на медленную частоту, заставляет электронное устройство работать субоптимально.

В соответствии с иллюстративным вариантом осуществления, может быть реализован алгоритм (или процесс) адаптивного отбора по скорости, который позволяет частоту (то есть FMAX) и задержки синхронизирующих импульсов устанавливать в зависимости от устройства. Алгоритм адаптивного отбора по скорости может основываться на наборе "схем распределения частот", определяемых из статистической информации для достаточно большой выборочной совокупности электронных устройств из конкретного семейства электронных устройств, например для некоторого типа интегральной схемы и компонента вне кристалла. Статистическая информация может быть собрана в течение процесса определения параметров, выполняемого на заводе. Набор схем распределения частот может сохраняться в электронном устройстве до отправки. На месте алгоритм адаптивного отбора по скорости выбирает и реализует соответствующую схему распределения частот для конкретного электронного устройства. В иллюстративном варианте осуществления каждая схема распределения частот содержит значение FMAX и значение задержки внешних синхронизирующих импульсов. Алгоритм адаптивного отбора по скорости может быть воплощен в программном обеспечении или реализован любым другим способом и может выполняться при начальной загрузке, каждый раз, когда выполняется загрузка электронного устройства, непрерывно во время работы электронного устройства, в ответ на воспринятый случай или состояние, или при любой комбинации указанных выше условий.

Процесс определения параметров может начинаться с вычисления задержки ("K") между синхронизирующими импульсами обратной связи и внешними синхронизирующими импульсами для выборочной совокупности электронных устройств. Возвращаясь к фиг.3, отметим, что на ней можно легко заметить, что время tподг подготовки к работе для контроллера 113 основано на задержке от перехода внешних синхронизирующих импульсов до перехода синхронизирующих импульсов обратной связи для операции считывания. Можно также заметить, что время tудерж удержания основано на задержке от перехода синхронизирующих импульсов обратной связи до следующего перехода внешних синхронизирующих импульсов. Соответственно, если задержка между внешними синхронизирующими импульсами и синхронизирующими импульсами обратной связи сокращается, время tподг подготовки к работе уменьшается, а время tудерж удержания увеличивается. И наоборот, если задержка между внешними синхронизирующими импульсами и синхронизирующими импульсами обратной связи увеличивается, время tподг подготовки к работе увеличивается, а время tудерж удержания уменьшается. Таким образом, начальный этап процесса определения параметров может быть вычислением задержки между синхронизирующими импульсами обратной связи и внешними синхронизирующими импульсами, которая удовлетворяет в самом плохом случае минимальным времени подготовки к работе и времени удержания контроллера 113 для выборочной совокупности электронных устройств.

При допущении, что задержка между обратной связью и внешним устройством синхронизирующих импульсов установлена такой, чтобы удовлетворять требованию минимального времени подготовки к работе и времени удержания контроллера в течение операции считывания, неуспешное или успешное выполнение операции считывания будет полностью зависеть от того, удовлетворяется ли требование минимального времени tподг подготовки к повторной выборке. Что касается фиг. 3, то на ней время tподг подготовки к повторной выборке является очень длительным, когда задержка между системными синхронизирующими импульсами и синхронизирующими импульсами обратной связи маленькая. Однако когда задержка между этими двумя синхронизирующими импульсами увеличивается, время tподг подготовки к повторной выборке уменьшается до тех пор, пока не достигает минимального времени tподг подготовки к повторной выборке. Это представляет собой "максимальную задержку" между системными синхронизирующими импульсами и синхронизирующими импульсами обратной связи, при которой можно гарантировать операцию считывания. Поскольку внешние синхронизирующие импульсы задерживаются относительно системных синхронизирующих импульсов с фиксированным смещением относительно синхронизирующих импульсов обратной связи, внешние синхронизирующие импульсы также имеют "максимальную задержку" относительно системных синхронизирующих импульсов, при которой можно гарантировать эту операцию. "Максимальная задержка" между системными синхронизирующими импульсами и внешними синхронизирующими импульсами упоминается как "самое высокое значение прохождения" (СВЗП).

Возвращаясь вновь к фиг.2, отметим, что успешное или неуспешное выполнение операции записи будет зависеть от двух параметров согласования во времени: минимального времени tподг подготовки к работе и минимального времени tудерж удержания для записи в СДОЗУ 118. Однако, с практической точки зрения, минимальное время удержания tудерж обычно не является ограничивающим фактором. Это происходит потому, что время удержания приблизительно равно периоду синхронизирующих импульсов меньшему, чем время tподг подготовки к работе, которое намного больше, чем минимальное время tудерж удержания. Соответственно, минимальное время tподг подготовки к работе СДОЗУ 118 будет определять "минимальную задержку" между системными синхронизирующими импульсами и внешними синхронизирующими импульсами, при которой можно гарантировать операцию записи. Эта "минимальная задержка" будет упоминаться как "самое низкое значение прохождения" (СНЗП).

Во время процесса определения параметров процедура испытаний может выполняться на каждом электронном устройстве в выборочной совокупности, чтобы определять диапазон значений задержек между системными синхронизирующими импульсами и внешними синхронизирующими импульсами, при которых контроллер 113 может записывать в СДОЗУ 118 и считывать из него. Этот диапазон представляет собой непрерывный диапазон, связанный с "максимальной задержкой", устанавливаемой минимальным временем tподг подготовки к повторной выборке контроллера 113, и "минимальной задержкой", устанавливаемой минимальным временем tподг подготовки к работе СДОЗУ 118. Процедура испытаний может включать в себя программирование вычисляемой задержки между синхронизирующими импульсами обратной связи и внешними синхронизирующими импульсами в программируемые элементы задержки контроллера 113 для каждого из электронных устройств при испытании. Затем, диапазон регулировки программируемых элементов задержки для каждого электронного устройства можно развертывать по всему диапазону регулировки, в то же время поддерживая задержки между синхронизирующими импульсами обратной связи и внешними синхронизирующими импульсами. Более конкретно, для каждого электронного устройства программируемый элемент 412 задержки для внешних синхронизирующих импульсов может быть установлен на нулевую задержку, а программируемый элемент 420 задержки для синхронизирующих импульсов обратной связи может быть установлен на -K. Тогда задержка программируемых элементов задержки может вместе увеличиваться с приращением. Для каждой возрастающей задержки, контроллер 113 считывает из СДОЗУ 118 и записывает в него, а затем классифицирует каждую попытку считывания и записи как неуспешное или успешное выполнение, в зависимости от результата. Это может выполняться на каждой FMAX, например, медленной, номинальной и быстрой.

Фиг. 5 представляет репрезентативную блок-схему 500 процесса, которая иллюстрирует способ определения и сохранения схем распределения частот для семейства электронных устройств во время процесса определения параметров. На этапе 502 устанавливаются значения FMAX. В данном описании используются три значения FMAX: медленное, номинальное и быстрое. Номинальное значение в общем принимается как равное приблизительно средней частоте диапазона частот, при которых электронное устройство может работать. На этапе 504 определяется диапазон СВЗП для каждой FMAX, например, как обсуждалось выше.

Диапазон СВЗП определяется исходя из СВЗП для всех электронных устройств в выборочной совокупности. Фиг. 6 представляет график 600, показывающий распределения СВЗП для всех электронных устройств в выборочной совокупности. Количество устройств, имеющих конкретное СВЗП, представлено в зависимости от диапазона регулировки задержки между системными синхронизирующими импульсами и внешними синхронизирующими импульсами, которые в этом случае представлены в цифровой области как 0-31. График 600 изображает три различных распределения процесса для значений СВЗП, по одному на каждой из трех частот: быстрой, номинальной и медленной, из этапа 502. Как правило, центр диапазона рабочих частот для интегральной схемы представляет собой номинальную частоту, приблизительно самая высокая частота представляет собой быструю частоту, а приблизительно самая низкая частота представляет собой медленную частоту. В иллюстративном варианте осуществления медленная частота может составлять приблизительно 146 МГц, номинальная частота может составлять приблизительно 210 МГц, а быстрая частота может составлять приблизительно 270 МГЦ. Эти три частоты представляют различные частоты, на которых контроллер интегральной схемы может работать при осуществлении связи с СДОЗУ. На фиг. 6A диапазон СВЗП определен так, чтобы n=13-31.

На фиг. 6A, распределение 602 соответствует FMAX, являющейся Медленной; распределение 604 соответствует FMAX, являющейся Номинальной; распределение 603 соответствует FMAX, являющейся Быстрой. Эти распределения в общем известны в технике интегральных схем, так что в данном описании подробно не обсуждаются. Поэтому, хотя другие электронные устройства могут иметь иные медленные, номинальные и быстрые частоты, распределения фиг. 6A могут быть все еще в общем подходящими. Однако диапазон СВЗП оси X является специфическим для конкретного семейства электронных устройств и в общем неизвестен. Поэтому, как только диапазон СВЗП определен, распределения могут быть подогнаны к диапазону СВЗП, как на этапе 506.

Распределения процесса на фиг. 6 принимают форму кривых нормального распределения, где смежные кривые нормального распределения перекрываются около оси X. Диапазон СВЗП разделен на "элементы разрешения", границы которых определяются в местах наложения кривых нормального распределения. Элементы разрешения имеют приблизительно одинаковую ширину, в данном описании каждая составляет приблизительно 6 единиц измерения задержки по ширине. Элементы разрешения позже используются в формировании схем распределения частот, а также используются алгоритмом адаптивного отбора по скорости, показанным на фиг. 8.

Возвращаясь к фиг. 5, отметим, что на этапе 508 определяется среднее значение СВЗП для каждого элемента разрешения. Например, на фиг. 6 для распределения 602 среднее значение, представленное стрелкой 612, составляет приблизительно СВЗП=16. Для распределения 604 среднее значение, представленное стрелкой 614, составляет приблизительно СВЗП=22. И для распределения 606 среднее значение, представленное стрелкой 612, составляет приблизительно СВЗП=28.

На этапе 510 схема распределения частот (СРЧ) определяется для каждой FMAX, определенной на этапе 502. В иллюстративном варианте осуществления каждая схема распределения частот связана с элементом разрешения. Схема распределения частот включает в себя FMAX, ширину элемента разрешения СВЗ