Устройство суммирования двоичных кодов

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия устройства. Каждый разряд устройства содержит восемь логических элементов И, два RS-триггера, шесть логических элементов ИЛИ, пять логических элементов НЕ, каждые три разряда имеют дополнительный логический элемент И. 2 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Известны способы и устройства суммирования двоичных кодов, заключающиеся в последовательном выполнении элементарных операций (ЭО) приема слагаемых, формирования переноса и суммы в каждом разряде и занесения результата суммирования в триггеры регистра результата или в триггеры первого слагаемого. При этом для повышения быстродействия суммирования используют схемы групповых переносов. Способы и устройство суммирования двоичных кодов детально рассмотрены в книге Карцева М.А. «Арифметика цифровых машин», М.: Наука, 1969 г., стр.201-220 и в книге Гаврилова Ю.В. и Пучко А.Н. «Арифметические устройства быстродействующих ЭВМ», М.: Советское радио, 1970, стр.85-109. Общим недостатком известных устройств является наличие трех RS-триггеров в каждом разряде и некоторые затраты оборудования для построения цепей ускоренного переноса (ЦУП), что определяет время выполнения суммирования, объем оборудования и стоимость устройства в целом. Наиболее близким, принятым за прототип, является суммирующее устройство, приведенное в книге Гаврилова Ю.В. и Пучко А.Н. на стр.109, рис 2.4.16. Для построения ЦУП указанного устройства требуется сравнительно малое число логических элементов, однако прототип имеет большой недостаток, присущий практически всем известным сумматорам, заключающийся в значительной временной задержке «выключения» потенциала переноса. На фиг.1 приведены временные диаграммы формирования переноса для различных вариантов построения суммирующих устройств.

Целью изобретения является повышение быстродействия выполнения операции сложения как отдельной операции, так и многократных операций сложения, имеющих место при выполнении операции умножения кодов. Для чего предложен способ, отличающийся тем, что по первому временному такту принимают код второго слагаемого во второй триггерный регистр, в первом триггерном регистре хранят код первого слагаемого, по второму временному такту с помощью комбинационного сумматора формируют сигналы переноса и суммы в каждом разряде, при этом формирование сигнала сквозного переноса первой и всех нечетных операций суммирования выполняют с помощью первой схемы формирования переноса, а при выполнении второй и всех четных операций суммирования формируют сигнал сквозного переноса с помощью второй схемы формирования переноса, кроме того, при выполнении нечетных операций суммирования запрещают работу второй схемы формирования переноса, а при выполнении четных операций суммирования запрещают работу первой схемы формирования переноса, по третьему временному такту заносят результаты суммирования в первый триггерный регистр.

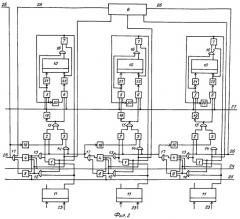

Для реализации способа предложено устройство суммирования двоичных кодов, содержащее в каждом разряде первый и второй RS-триггеры, восемь элементов И, шесть элементов ИЛИ, пять элементов НЕ, информационный вход, подключенный к единичному входу второго RS-триггера, отличающееся тем, что единичный выход второго RS-триггера соединен с первыми входами первых элементов И, ИЛИ, вторые входы упомянутых элементов связаны с выходом седьмого элемента И, выход первого элемента И соединен с первыми входами вторых элементов ИЛИ, И, вторые входы которых подключены к входу переноса из младшего разряда устройства, выход первого элемента ИЛИ соединен с первыми входами четвертого и восьмого элементов И и третьего элемента ИЛИ, вторые входы этих элементов И соединены с выходом второго элемента ИЛИ, третьи входы четвертого и восьмого элементов И связаны с первым и вторым входами управления формированием сигнала переноса соответственно, выходы упомянутых элементов И соединены с первым и вторым входами шестого элемента ИЛИ, выход шестого элемента ИЛИ является входом переноса в старший разряд, который через первый элемент НЕ подключен к первому входу третьего элемента И, второй вход этого элемента соединен с выходом третьего элемента ИЛИ, второй вход третьего элемента ИЛИ связан с входом переноса из младшего разряда, выходы второго и третьего элементов И соединены с входами четвертого элемента ИЛИ, выход которого подключен к первому входу шестого элемента И и входу второго элемента НЕ, выход которого связан с первым входом пятого элемента И, вторые входы пятого и шестого элементов И соединены с входом и выходом третьего элемента НЕ соответственно, третьи входы упомянутых элементов И соединены с входом управления приемом кода в первый триггер, выходы пятого и шестого элементов И через четвертый и пятый элементы НЕ соединены с нулевым и единичным входами первого RS-триггера соответственно, выход пятого элемента И соединен с первым входом пятого элемента ИЛИ, второй его вход связан с единичным выходом первого RS-триггера, а выход подключен к первому входу седьмого элемента И, второй вход которого подключен к выходу пятого элемента НЕ, выход седьмого элемента И соединен с входом третьего элемента НЕ, кроме того, выходы шестых элементов ИЛИ третьего, шестого, девятого разрядов связаны с четвертым входом девятого элемента И цепи ускоренного переноса старшей группы разрядов, выходы первых элементов ИЛИ первого, второго и третьего разрядов каждой группы соединены с первым, вторым и третьим входами девятого элемента И соответственно, выходы девятых элементов И соединены с третьими выходами шестых элементов ИЛИ третьего, шестого и девятого разрядов.

Отметим основные отличительные признаки способа и устройства суммирования и что позволяет получить каждый из этих признаков.

1. Формирование переноса нечетных операций сложения выполняется с помощью первой схемы формирования переноса (четвертый элемент И). При этом максимальная задержка сигнала в цепи формирования переноса будет равняться 2τK (здесь τ - задержка сигнала на одном элемент И (ИЛИ), К - число групп, на которое поделены все разряды устройства). В рассматриваемом случае в группу объединены три разряда. Таким образом простейшая схема ускорения переноса обеспечивает снижение задержки сигнала переноса в три раза, при этом «выключение» сигнала переноса исключается автоматически, т.к. следующее формирование переноса будет выполняться второй схемой переноса.

2. Формирование переноса четных операций сложения выполняется с помощью второй схемы формирования переноса (восьмой элемент И).

3. Для формирования ускоренного переноса используется девятый элемент И, первый, второй и третий входы которого соединены с выходами первых элементов ИЛИ первого, второго и третьего разрядов. Четвертый вход девятого элемента И связан с выходом шестого элемента ИЛИ третьего (старшего) разряда группы из трех разрядов.

4. Первый и второй входы управления формированием сигнала переноса подключены к третьим входам четвертого и восьмого элементов И соответственно и обеспечивают поочередное выключение названных элементов, что позволяет исключить время «выключения» сигнала переноса из суммарного времени выполнения операции суммирования и повысить быстродействие в 2-3 раза.

5. Подключение выхода пятого элемента И через пятый элемент ИЛИ к входу седьмого элемента И, второй вход которого связан с выходом пятого элемента НЕ, обеспечивает задержку сигнала с выхода седьмого элемента И, что позволяет заносить результат суммирования в первый триггер и построить каждый разряд устройства на двух RS-триггерах и выполнить операцию однократного сложения за три временных такта, а операцию многократного суммирования за - два временных такта. Это позволяет повысить быстродействие предлагаемого устройства по сравнению с известными устройствами в 1,5 раза.

Для пояснения работы объекта на фиг.1 приведены временные диаграммы выполнения операций суммирования трех вариантов устройств. На диаграмме приняты следующие обозначения: t1 - длительность каждого временного такта, Т.вкл. - время «включения» переноса, Т.выкл. - время «выключения» переноса, Т 1, 2, 3 - время суммирования без применения ЦУП, суммирование с ЦУП в известных устройствах и время суммирования в предлагаемом устройстве соответственно. На фиг.2 приведена функциональная схема трех разрядов предлагаемого устройства суммирования. Каждый разряд содержит элементы И 1-7, 9, RS-триггеры (Tr) 10, 11, элементы ИЛИ 12-17, элементы НЕ 18-22, информационный вход 23, входы управления (BУ) работой первой и второй схемой формирования переноса 24, 25, ВУ приемом кода в Tr.10, 27, вход переноса из старшего разряда младшей группы разрядов 26, выход И 8, 28, каждые три разряда устройства содержат ЦУП, построенную на основе четырехвходового элемента И 8.

Рассмотрим работу устройства при выполнении операции суммирования. В исходном состоянии (в статике) Tr 10, 11 установлены в нуль. На входах 23, 26 ВУ 25, 27 отсутствуют высокие потенциалы, на ВУ 24 присутствует высокий потенциал.

1. Операция сложения. Операция выполняется за три временных такта (t1, t2 и t3). По t1 выполняется ЭО приема кода второго слагаемого в Tr 11. При этом код первого слагаемого хранится в Tr 10 как результат выполнения предыдущей операции.

Второй временной такт отводится для формирования максимального сквозного переноса, который равен 2nτ (n - число двоичных разрядов; X - временная задержка сигнала на одном элементе И (ИЛИ), если не применяется ЦУП. Временная диаграмма формирования переноса без ЦУП приведена на фиг.1а. Из фиг.1а следует, что для формирования сигнала переноса, равного по времени длительности t, необходимо использовать ЦУП при «включении» переноса (Фиг.1б) и принять необходимые меры при его «выключении» (фиг.1в). В рассматриваемом устройстве применена ЦУП, объединяющая три разряда. При этом в каждой группе разрядов имеет место временная задержка сигнала, равная 2 τ, а максимальное время формирования сигнала «выключения» переноса Т.вкл будет в 3 раза меньше, чем без применения ЦУП.

Формирование сигнала сквозного переноса в каждом разряде выполняется согласно соотношению

здесь Ai, Bi - значение слагаемых i - того разряда;

Pi-1 - перенос из младшего разряда;

Pi - перенос, выработанный в i-том разряде.

При использовании ЦУП в каждой группе из трех разрядов перенос (Рк) вырабатывается согласно соотношению

Здесь Рк-1 - перенос из младшей группы. Соотношение (2) реализуется с помощью элементов ИЛИ 12 первого, второго и третьего разрядов группы и входа 26 из младшего разряда группы из трех разрядов. Формирование суммы в каждом разряде (Si) выполняется согласно соотношению

Это соотношение реализуется элементами И1, 2, 3, ИЛИ 15, НЕ 18.

По третьему временному такту сумма каждого разряда Si (элемент ИЛИ 15) заносится парафазным кодом в Tr 10, при этом в тех разрядах, где Si=1, с выхода ИЛИ 15 на вход И 6 поступит высокий потенциал. На третьи входы И 5, 6 всех разрядов по ВУ 27 поступит высокий потенциал и занесет в Tr 10 код единицы. Если значение Si=0, импульс, поступивший по ВУ 27, установит Tr 10 в нуль. На этом операция суммирования закончена.

2. Операция многократного сложения. В ряде вычислительных процедур имеет место выполнение многократного сложения принятого в Tr 11 второго слагаемого или множимого, например, при умножении. При этом, кроме использования ЦУП для ускорения «включения» переноса, необходимо свести к минимуму задержку «выключения» переносов. В рассматриваемом устройстве при всех нечетных суммированиях перенос в каждом разряде формируется с помощью элементов И 1, ИЛИ 12, 13, И 4, ИЛИ 17 и ВУ 24, при этом элемент И9 отключен. Формирование переноса при всех четных операциях суммирования обеспечивается элементами И 1, ИЛИ 12, 13, И 9, ИЛИ 17, ВУ 25. Временная диаграмма формирования переноса при многократном суммировании кодов приведена на Фиг.1в. По t2 выполняется ЭО занесения суммы в триггеры первого регистра, где ранее хранился код предыдущего суммирования. Таким образом, каждая операция многократного суммирования выполняется за два такта, вместо трех тактов в известных устройствах.

Таким образом, предложенный способ и устройство суммирования обеспечивают повышение быстродействия выполнения операций многократного сложения (умножения) при минимальных затратах оборудования по сравнению с известными устройствами.

Устройство суммирования двоичных кодов, содержащее в каждом разряде первый и второй RS-триггеры, восемь элементов И, шесть элементов ИЛИ, пять элементов НЕ, информационный вход, подключенный к единичному входу второго RS-триггера, отличающееся тем, что единичный выход второго RS-триггера соединен с первыми входами первых элементов И, ИЛИ, вторые входы упомянутых элементов связаны с выходом седьмого элемента И, выход первого элемента И соединен с первыми входами вторых элементов ИЛИ, И, вторые входы которых подключены к входу переноса из младшего разряда устройства, выход первого элемента ИЛИ соединен с первыми входами четвертого и восьмого элементов И и третьего элемента ИЛИ, вторые входы этих элементов И соединены с выходом второго элемента ИЛИ, третьи входы четвертого и восьмого элемента И связаны с первым и вторым входами управления формированием сигнала переноса соответственно, выходы упомянутых элементов И соединены с первым и вторым входами шестого элемента ИЛИ, выход шестого элемента ИЛИ является входом переноса в старший разряд, который через первый элемент НЕ подключен к первому входу третьего элемента И, второй вход этого элемента соединен с выходом третьего элемента ИЛИ, второй вход третьего элемента ИЛИ связан с входом переноса из младшего разряда, выходы второго и третьего элементов И соединены с входами четвертого элемента ИЛИ, выход которого подключен к первому входу шестого элемента И и входу второго элемента НЕ, выход которого связан с первым входом пятого элемента И, вторые входы пятого и шестого элементов И соединены с входом и выходом третьего элемента НЕ соответственно, третьи входы упомянутых элементов И соединены с входом управления приемом кода в первый триггер, выходы пятого и шестого элементов И через четвертый и пятый элементы НЕ соединены с нулевым и единичным входами первого RS-триггера соответственно, выход пятого элемента И соединен с первым входом пятого элемента ИЛИ, второй его вход связан с единичным выходом первого RS-триггера, а выход подключен к первому входу седьмого элемента И, второй вход которого подключен к выходу пятого элемента НЕ, выход седьмого элемента И соединен с входом третьего элемента НЕ, кроме того, выходы шестых элементов ИЛИ третьего, шестого, девятого разрядов связаны с четвертым входом девятого элемента И цепи ускоренного переноса старшей группы разрядов, выходы первых элементов ИЛИ первого, второго и третьего разрядов каждой группы соединены с первым, вторым и третьим входами девятого элемента И соответственно, выходы девятых элементов И соединены с третьими входами шестых элементов ИЛИ третьего, шестого и девятого разрядов.