Преобразователь двоично-десятичного кода в десятичный фазоимпульсный

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союа Советских

Социалистических

Республик

Зависимое от авт. свидетельства ¹

Кл. 42mI, 5/02

Заявлено 03,1.1968 (№ 1207670/18-24) с присоединением заявки №

Приоритет

Опубликовано 20.II.1969. Бюллетень ¹ 9

Дата опубликования описания 18Л/П.1969

;1 1ПК G 06f

УДК 681.325.63(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения К. Г, Борисов, Л. С. Ситников, С. Е. Токовенко и Л. Л. Утяков

Заявитель

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА

В ДЕСЯТИЧНЪ|Й ФАЗОИМПУЛЬСНЬ1Й

Изобретение относится к области радиоэлектроники и может быть использовано в цифровой измерительной и вычислительной технике, чапример, .для вывода информа цип с триггер,ных декад на газоразрядные и другие цифровые индикаторы и устройства.

Известные преобразователи двоично-десятичного кода в десятичный фазоимпульсный для целей индикации состояния триггерных декад не обеспечивают, вывода информации в режиме счета и требуют четкого разграничегния режимов счета и индикации, что ограничигает их применение.

В предлагаемом преобразователе преобразование кодов осуществляется независимо от режима работы триггерных декад, что позволяет упростить схему автоматики прибора и одновременно, повысить его быстродействие.

Предлагаемый преобразователь кодов отличается от известных тем, что в нем использованы логические схемы равнозначности и схема совпадения, причем .первые входы схемы равнозначности подключены к выходам опорной декады, а:вторыс подсоединены к за>кимам входных сигналов преобразователя, выходы с:,ем равнозначности через схему совпадения .подключены,к за>киму выходного сигнала.

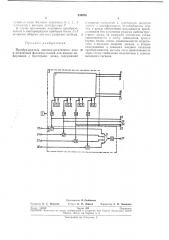

На чертеже приведена блок-схема описываемого преобразователя кодов.

Она состоит пз тактового генератора 1, опорH c I I д е к и д ы 2. В к.1 ю 1 а ю щ с и т 1> и Г Г е р ы 8 6 11 дешифратор 7 на десять выходов (клеммы ч — 17), а также формирователи 18 — 21 опорного двопчно-десятичного кода, который снимается с клемм 22 — -6. ссбстзснпо преобразователя кодов 26, состоящего из четырех логи Icскпх схем равнозначност;I 27 — 80. схемы сов.падения 81 на четыре вход<1 и выходного фор10 мпрователя 82. Связи между триггерами опорнсй декады (на чертеже не показаны) обеспечивают тождество Опорного и преобразуемого кодов.

Преобразователь работает следующим обра15: ом.

На клеммах 22 — 26 псрподпчсскп с частотой

/г —, где f, — частота импульсов на выходе гс10 псратора 1, появляются все кодовые комбпна20 ппи. Входной сигнал (число в двопчно-десятичном коде) поступает на входы 88 — 86 преобразователя. В моменты совпадения опорного

:1 преобразуемого кодов на выходах всех логических элементов равнозна 1ностп появля1отся

25 сигналы, совпадающие во времени, что приводит и пояB;Icíøî импульсов на выходе схемы 81. Этп импульсы усиливаются формирователем 82 и поступают на выходную клемму 87. Временное поло>кение импульсОВ прсд30 ставляет входное число в десятичном фазопмПред((ст изобретения

Составитель Л. Скобелева

Техрсд Л. Я. Левина

Корректор 3. И. Чванкина

Редактор Б. С. !(анкина

Заказ 1446/2 Тира>к 480 Подписное !

1111!!4ПИ Когвн четв !lo делаги изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, и. 4

Типографии, пр. Сапуновгч 2

";:(Ьо(1 i 3(КОДС. г4 азоВЬ КОНСтан 1 Ы О, 1, ... 3

" .I. 1(.e а;0 т с я с В ы х О до 3,:1 епи l l:, i р а 1 О р е(Б случа пр1 менении,подооного преобразователя в многоразрядных приборах блоки 1 и 2 ягпляются общими для всех разрядов прибора.

Преобразователь двоично-десятичного кода

:в десятичный фазоимпульсный для вывода информации с триггерных декад, содержащий (i н ратОр им.i) . 11 сов li . риггеpili 10 Опо Зн (О ,(Сиапгр С,ДЕЦ(1(фРатОРОМ, OTii!. -(Q!0LLjiiiiCA тЕМ, что, с целью обеспечения возможности преобразования без изменения режима работы триг5 гсрных;!el(ay, 0Н содер IHT логи lect Ise схемы равнозначнссги и схему совпадения, причеi( псрвыс входы схемы равнозначности подкгиочсны к выходам опорной декады, а вторые подсоединены к зажимам входных сигналов

10 преобразователя, вы. оды схем равнозначности через схему. совпадения подключены к зажиму выходного сигнала.