Десятичный сумматор

Иллюстрации

Показать всеРеферат

A-и с-А-- н и е

ИЗОБРЕТЕНИЯ

Союз Соеетскиз

Социалистических

Республик

К АВТОРСКОМ СВИДЕтЕЛЬСтВЮ

Зависимое от авт. свидетельства №

Заявлено 14.Х11.1967 (№ 1203153/18-24) с присоединением заявки ¹

Приоритет

Опубликовано 20.11.1969. Бюллетень ¹ 9

Дата опубликования описания 10.1Х.1969

Кл. 42m3, 7/50

МПК С 061

УДК 681.325.54(088.8) Комитет по делам изсбпетени1 и стккытии пси Сосете Мнии;тдас

СССР

Автор изобретения

В. П. Тульский

Институт электронных управляющих машин

Заявитель

ДЕСЯТИЧНЬ1Й СУММАТОР

Известен десятичный сумматор, содержащий четыре полных двоичных сумматора с поразрядным переносом внутри тетрады и работающий с применением цепи коррекций.

Предложенный десятичный сумматор содержит ряд связанных цепями переноса устройств сложения двух десятичных одноразрядных чисел (тетрад), каждое из которых состоит из четырех устройств выработки выходного сигнала суммы, соответственно в разрядах единиц, двоек, четверок и восьмерок, а также устройств выработки сигналов переноса и отсутствия переноса в следующую тетраду, и отличается тем, что каждое из устройств выработки сигналов суммы соединено со входами слагаемых соответствующих двоичных разрядов, а также со входами слагаемых предыдущих двоичных разрядов и со входами переноса и отсутствия переноса из предыдущей тетрады. Устройства выработки сигналов переноса и отсутствия переноса в следующую тетраду соединены также со входами всех разрядов слагаемых и со входом переноса из предыдущей тетрады, причем устройство выработки сигнала отсутствия переноса в следующую тетраду, кроме того, соединено со входом отсутствия переноса из предыдущей тетрады.

Это повышает быстродействие описываемого сумматора.

Сумматор отличается также тем, что, с целью обнаружения ошибок, каждое устройство сложения двух десятичных чисел содержит устройство контроля выходных сигналов, соединенное с выходами устройств выработки сигналов суммы трех старших разрядов и устройств выработки сигналов переноса.

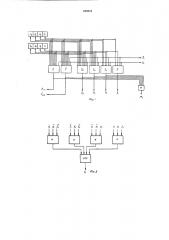

На фиг. 1 изображено устройство образования i- <; на фиг. 2 — устрой10 ство Х для образования выходного сигнала суммы $, в первом разряде i-й тетрады суммы; на фиг. 3 — устройство Хе для образования выходного сигнала суммы S в разряде двоек i-и тетрады; на фиг. 4 — устройство 1

15 для образования выходного сигнала S4 в разряде четверок 1-й тетрады; на фиг. 5 — устройство Хе для образования выходного сигнала Ss в разряде восьмерок i-й тетрады суммы; на фиг. 6 — устройство Z для образования

2о сигнала десятичного переноса Ет 1 в (i+1)-ю тетраду; на фиг. 7 — устройство Z для образования сигнала Et t, сигнализирующего об отсутствии переноса в (i + 1) -ю тетраду; на фиг. 8 — устройство контроля М.

На чертежах приняты следующие условные обозначения: Х1 и У» Хз и Уе, Х4 и У, Хе и Y — сигналы разрядов слагаемых; Е,— Е, — сигналы наличия и отсутствия переноса из пре30 дыдущей тетрады в i-ю тетраду; Et+>, Е;+1—

238231

10 соответственно из -й в (i+1)-ю тетраду; т, — сигнал ошибки.

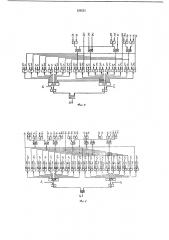

На вход устройства Ztt подаются сигналы

Хц, Х, Х, Х, Ytt, У4, У„Уь Е, и их инверсии.

На вход устройства Z4 подаются сигналы Х, Х, Х>, У4, У, Уь Е и их инверсии.

На вход устройства Z подаются сигналы

Х, Х,, У„Уь Е; и их инверсии. На вход устройства Х, подаются сигналы Х,, Уь Е, и их инверсии. На вход устройств Z u Z подаются сигналы Х8, Х., Х, Х,, У,, У4, У,, У> и их инверсии, а также Е, . На вход устройства Z заведен, кроме того, сигнал Е,. На выходе появлгпотся сигналы E; .> и Е;, > которые дают информацию о наличии или отсутствии переноса в стар шую (i+1) -ю тетр аду.

На вход устройства ЛП заведены сигналы

S8, 54, $,, Е;, E; . Появление на выходе единичного сигнала m< свидетельствует о наличии контролируемой ошибки в -й тетраде.

Функциональная схема десятичного сумматора может быть выполнена из переключателей «И», переключателей «ИЛИ» и инверторов или из элементов «НŠ— И». Узлы 2 .tt, Х4, Z>, Х„Z u Z каждой тетрады построены так, что выходы устройств образования переноса и отсутствия переноса из младшей тетрады заведены в предпоследние каскады перечисленных узлов.

В рабочем состоянии, когда на входы устройств поразрядного суммирования и образования сигналов переноса и отсутствия переноса одновременно поступают соответствующие сигналы, эти устройства выдают единичный сигнал, если выполнено одно из специальных логических условий. В противном случае на выходе названных устройств будет нулевой сигнал, Сигналы Е, и Е,, образованные соответствующими устройствам и в (i — 1)-й тетраде суммы, поступают в узлы Ztt, Х4, Z>, Zt, Z u Z -й тетрады суммы.

15 г0

З0

Превышение содержимым тетрады числа девять является контролируемой ошибкой.

Контролируется также одновременное появление или единичных или нулевых сигналов

Е и Е из каждой тетрады. Когда произойдет контролируемая ошибка, то устройство выдаст единичный сигнал т;.

Предмет изобретения

1. Десятичный сумматор, содержащий связанные цепями переноса устройства сложения двух десятичных одноразрядных чисел (тетрады), каждое из которых состоит из четырех устройств выработки выходного сигнала суммы, соответственно в разрядах единиц, двоек, четверок и восьмерок, а также устройств выработки сигналов переноса и отсутствия переноса в следующую тетраду, отличаюи ийся тем, что, с целью повышения быстродействия, каждое из устройств выработки сигналов суммы соединено со входами слагаемых соответствующих двоичных р азрядов, а также со входами слагаемых предыдущих двоичных разрядов и со входами переноса и отсутствия переноса из предыдущей тетрады; устройства выработки сигналов переноса и отсутствия переноса в следующую тетраду соединены также со входами всех разрядов слагаемых и со входом переноса из предыдущей тетрады, причем устройство выработки сигнала отсутствия переноса в следующую тетраду, кроме того, соединено со входом отсутствия переноса из предыдущей тетрады.

2. Сумматор по и. 1, отличающийся тем, что, с целью обнаружения ошибок, каждое устройство сложения двух десятичных чисел содержит устройство контроля выходных сигналов, соединенное с выходами устройств выработки сигналов суммы трех старших разрядов и устройств выработки сигналов переноса.

238231

Ф иг. 7

Е... Е,.1

Составитель И. Н. Горелова

Редактор Б. С. Нанкина Текред Л. Я. Левина Корректор О. И. Попова

Заказ 2134!6 Тираж 480 Подписное

ЦНИИГ1И Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2