Устройство сортировки информации методом преобразования данных в адрес

Иллюстрации

Показать всеИзобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания быстродействующих специализированных цифровых устройств по упорядочению двоичной информации, выполняющих сортировку положительных и отрицательных чисел и осуществляющих подсчет количества одинаковых чисел и символов. Техническим результатом является расширение функциональных возможностей устройства, снижение аппаратных затрат, повышение надежности работы, упрощение алгоритма работы блока управления. Устройство содержит блок ввода данных, блок сортировки положительных чисел, блок хранения результата, блок сортировки отрицательных чисел, блок управления. 21 ил.

Реферат

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для решения задач по упорядочению числовой и символьной информации по возрастанию и убыванию, осуществлению операций поиска данных в информационном массиве как по указанному интервалу, так по конкретному значению.

Известно "Устройство для сортировки чисел" (а.с. №1304015, 1987 г.), позволяющее упорядочить массив чисел как в возрастающем, так и в убывающем порядке.

Известно "Устройство для сортировки чисел" (а.с. №1277091, 1986 г.), позволяющее упорядочить числа в возрастающем и в убывающем порядке.

Известно "Устройство для реализации упорядочивающих подстановок" (патент №2067315), выполняющую задачу алфавитной сортировки слов.

В качестве прототипа выбрано "Устройство сортировки символов" (патент №2067317), которое позволяет упорядочить информацию по возрастанию и по убыванию.

Задача заключается в следующем:

1) упростить алгоритм работы устройства сортировки информации,

2) повысить скорость упорядочения входных данных,

3) расширить функциональные возможности устройства сортировки информации.

В представленном устройстве сортировки информации методом преобразования данных в адрес выполняется задача сортировки входной числовой и символьной информации по возрастанию и убыванию. В устройстве осуществляются поисковые операции по указанному интервалу или по конкретному заданному символу или числу. Сортировка информации осуществляется как положительных, так и отрицательных чисел и символов. Выполняется подсчет количества одинаковых чисел и символов.

Предлагаемое устройство сортировки информации методом преобразования данных в адрес позволит значительно снизить аппаратные средства, что ведет к упрощению комбинационной схемы, упростит алгоритм работы устройства, а также расширить функциональные возможности устройства.

Современные вычислительные системы работают наиболее эффективно при упорядоченных данных. Сортировка информации - это процесс расстановки элементов в некотором порядке. Элементы размещаются следующим образом: 1) вычисления, которые требуют определенного порядка расположения данных, могли выполняться эффективно, 2) результаты имели осмысленный вид, 3) последующие операции имели бы упорядоченные исходные данные. Есть много различных способов упорядочений информации таких, например, как сортировка имен в списке по алфавиту или упорядочение данных по возрастанию или по убыванию.

Упорядочение данных включает анализ возможностей аппаратных средств вычислительных систем, расположения их каналов, объема оперативной памяти, частоты обращений, быстродействия, диапазона обработки входной числовой и символьной информации.

Задача сортировки потоков информации в вычислительной технике является настолько важной, что ее следует осуществлять только тогда, когда тщательное изучение аппаратных средств и параметров данных оправдывает сортировку [1].

Представленное устройство сортировки информации методом преобразования данных в адрес может использовать методы внешней сортировки данных. Внешние методы приемлемы для файлов данных, которые слишком велики, чтобы поместиться в оперативной памяти процессора.

Решение задачи осуществляется тем, что устройство сортировки информации методом преобразования данных в адрес, содержащее блок управления, отличающееся тем, что дополнительно введены: блок сортировки положительных чисел, блок хранения результата, блок сортировки отрицательных чисел, причем информационный выход блока ввода данных, на котором формируются двоичные коды чисел в прямом коде со своими знаковыми разрядами и символы, представленные в двоичном коде, передача входных двоичных кодов символов и чисел осуществляется в параллельном режиме побайтно, соединен с шестым информационным входом блока сортировки положительных чисел и с шестым информационным входом блока сортировки отрицательных чисел, с первого по пятый информационные входы блока сортировки отрицательных чисел, на которых формируются: сигнал обнуления двоичного счетчика строк, генератор прямоугольных импульсов, сигнал установки в нулевое состояние двоичного счетчика столбцов, генератор тактовых импульсов, сигнал сброса в нулевое состояние, записи, чтения регистров, сигналы выбора микросхемы, сигнал записи-считывания, сигнал разрешения по выходу четвертого оперативного запоминающего устройства, сигналы выбора микросхемы, сигнал записи-считывания, сигнал разрешения по выходу пятого оперативного запоминающего устройства, соединены соответственно с шестым по десятый информационными выходами блока управления, с первого по пятый информационные входы блока сортировки положительных чисел, на которых формируются: сигнал обнуления двоичного счетчика строк, генератор прямоугольных импульсов, сигнал установки в нулевое состояние двоичного счетчика столбцов, генератор тактовых импульсов, сигнал сброса в нулевое состояние, записи, чтения регистров, сигналы выбора микросхемы, сигнал записи-считывания, сигнал разрешения по выходу первого оперативного запоминающего устройства, сигналы выбора микросхемы, сигнал записи-считывания, сигнал разрешения по выходу второго оперативного запоминающего устройства, соединены соответственно с первым по пятый информационными выходами блока управления, с первого по восьмой управляющие выходы блока управления, на которых формируются сигналы обнуления двоичных счетчиков, формирующих адреса строк и столбцов, сигналы прямоугольных и тактовых импульсов, поступающие на суммирующие входы двоичных счетчиков, сигналы выбора микросхемы, сигнал записи-считывания, сигнал разрешения по выходу третьего оперативного запоминающего устройства, соединены соответственно с первым по восьмой управляющими входами блока хранения результата, информационный выход блока сортировки положительных чисел, на котором формируется двоичный код и количество одинаковых положительных чисел, соединен с первым информационным входом блока хранения результата, информационный выход блока сортировки отрицательных чисел, на котором формируется двоичный код и количество одинаковых отрицательных чисел, соединен со вторым информационным входом блока хранения результата, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами устройства сортировки информации методом преобразования данных в адрес.

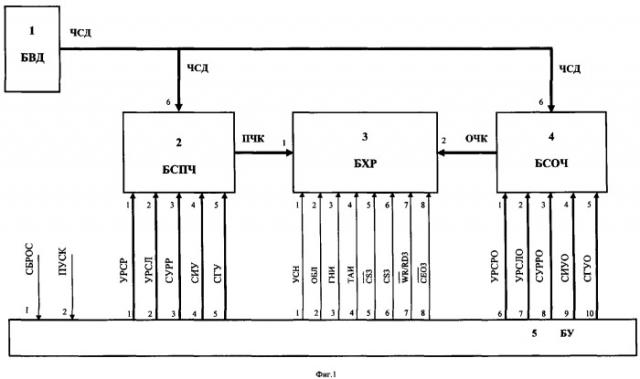

Устройство сортировки информации методом преобразования данных в адрес содержит: блок ввода данных, блок сортировки положительных чисел, блок хранения результата, блок сортировки отрицательных чисел, блок управления, оперативные запоминающие устройства, двоичные счетчики, пороговые элементы (фиг.1).

БВД - блок ввода данных служит для ввода чисел со своим знаковым разрядом и символов, информация представлена в двоичном коде.

БСПЧ - блок сортировки положительных чисел служит для определения знакового разряда двоичного числа, упорядочения положительных чисел, подсчета одинаковых положительных чисел и символов, а также для записи и хранения упорядоченной информации.

БХР - блок хранения результата служит для записи и хранения в нем результата упорядоченной двоичной информации.

БСОЧ - блок сортировки отрицательных чисел служит для определения знакового разряда двоичного числа, упорядочения отрицательных чисел, подсчета одинаковых отрицательных чисел, а также для записи и хранения упорядоченной информации.

БУ - блок управления служит для формирования управляющих сигналов, которые осуществляют процесс сортировки входной информации.

На фиг.1 изображена структурная схема устройства сортировки информации методом преобразования данных в адрес.

На фиг.2 представлен вариант технической реализации блока ввода данных.

На фиг.3 представлена структурная схема блока сортировки положительных чисел, блока электронных ключей первого, блока формирования адреса первого, блока памяти первого, блока формирования адреса второго, блока памяти второго.

На фиг.4 изображена функциональная схема блока электронных ключей первого, структурная схема блока формирования адреса первого и блока памяти первого.

На фиг.5 показана функциональна схема блока формирования адреса первого.

На фиг.6 представлен вариант технической реализации блока адреса первого.

На фиг.7 представлен вариант технической реализации блока памяти первого.

На фиг.8 изображена функциональная схема блока электронных ключей первого, структурная схема блока формирования адреса второго и блока памяти второго.

На фиг.9 показана функциональна схема блока формирования адреса второго.

На фиг.10 представлен вариант технической реализации блока памяти второго.

На фиг.11 показана функциональна схема блока хранения результата.

На фиг.12 представлена структурная схема блока сортировки отрицательных чисел, блока электронных ключей второго, блока формирования адреса третьего, блока памяти третьего, блока формирования адреса четвертого, блока памяти четвертого.

На фиг.13 изображена функциональная схема блока электронных ключей второго, структурная схема блока формирования адреса третьего и блока памяти третьего.

На фиг.14 показана функциональна схема блока формирования адреса третьего.

На фиг.15 представлен вариант технической реализации блока адреса третьего.

На фиг.16 изображена функциональная схема блока памяти третьего.

На фиг.17 изображена функциональная схема блока электронных ключей второго, структурная схема блока формирования адреса четвертого и блока памяти четвертого.

На фиг.18 представлен вариант технической реализации блока формирования адреса четвертого.

На фиг.19 представлен вариант технической реализации блока памяти четвертого.

На фиг.20а, 20б изображена содержательная граф-схема алгоритма ГСА работы устройства.

На фиг.21а, 21б представлена размеченная граф-схема алгоритма ГСА работы устройства.

Для описания алгоритма работы блока 5 управления используются следующие идентификаторы:

1. БВД - блок ввода данных.

2. БСПЧ - блок сортировки положительных чисел.

3. БХР - блок хранения результата.

4. БСОЧ - блок сортировки отрицательных чисел.

5. БУ - блок управления.

6. ШФР1 - шинный формирователь первый блока памяти второго.

7. СУМ1 - сумматор первый блока памяти второго.

8. ШФР2 - шинный формирователь второй блока памяти четвертого.

9. СУМ2 - сумматор второй блока памяти четвертого.

10. ЧСД - выходной информационный двоичный код числовых и символьных данных, поступающий из блока ввода данных.

11. ПЧК - информационный двоичный код положительных чисел, а также количество одинаковых чисел, поступающий из блока сортировки положительных чисел.

12. ОЧК - информационный двоичный код отрицательных чисел, а также количество одинаковых чисел, поступающий из блока сортировки отрицательных чисел.

13. УРСР - информационный сигнал, поступающий из блока управления на вход блока формирования адреса первого, состоящий из управляющих сигналов генератора импульсов ГИ и сигнала обнуления ОБН двоичного счетчика Сч1.

14. УРСЛ - информационный сигнал, поступающий из блока управления на вход блока формирования адреса первого, состоящий из управляющих сигналов генератора тактовых импульсов ТИ и сигнала обнуления УСО двоичного счетчика Сч2.

15. УРСРО - информационный сигнал, поступающий из блока управления на вход блока формирования адреса третьего, состоящий из управляющих сигналов генератора импульсов ГИН и сигнала обнуления ОБНЛ двоичного счетчика Сч5.

16. УРСЛО - информационный сигнал, поступающий из блока управления на вход блока формирования адреса третьего, состоящий из управляющих сигналов генератора тактовых импульсов ТИМ и сигнала обнуления УСНО двоичного счетчика Сч6.

17. СУРР - информационный сигнал, поступающий из блока управления, состоящий из управляющих сигналов: записи, чтения, сброса в нулевое состояние регистров блока формирования адреса второго.

18. СУРРО - информационный сигнал, поступающий из блока управления, состоящий из управляющих сигналов: записи, чтения, сброса в нулевое состояние регистров блока формирования адреса четвертого.

19. ЗАП - управляющий двоичный сигнал, разрешающий режим записи информации в регистры блока формирования адреса второго.

20. ЧТН - управляющий двоичный сигнал, разрешающий режим чтения информации из регистров блока формирования адреса второго.

21. СБР - управляющий двоичный сигнал, устанавливающий в нулевое состояние двоичные регистры блока формирования адреса второго.

22. ЗАПО - управляющий двоичный сигнал, разрешающий режим записи информации в регистры блока формирования адреса четвертого.

23. ЧТНО - управляющий двоичный сигнал, разрешающий режим чтения информации из регистров блока формирования адреса четвертого.

24. СБРО - управляющий двоичный сигнал, устанавливающий в нулевое состояние двоичные регистры блока формирования адреса четвертого.

25. СИУ - информационный сигнал управления, поступающий из блока управления, состоящий из управляющих сигналов, формирующих работу оперативного запоминающего устройства блока памяти первого: выбора микросхемы, записи считывания, разрешение по выбору.

26. СИУО - информационный сигнал управления, поступающий из блока управления, состоящий из управляющих сигналов, формирующих работу оперативного запоминающего устройства блока памяти третьего: выбора микросхемы, записи считывания, разрешение по выбору.

27. - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти первого.

28. CS21 - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти первого.

29. - управляющий сигнал записи считывания информации оперативного запоминающего устройства блока памяти первого.

30. - управляющий сигнал разрешение по выбору оперативного запоминающего устройства блока памяти первого.

31. ЗРЧ - знаковый разряд двоичных положительных чисел.

32. ЗРОЧ - знаковый разряд двоичных отрицательных чисел.

33. - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти третьего.

34. CS24 - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти третьего.

35. - управляющий сигнал записи считывания информации оперативного запоминающего устройства блока памяти третьего.

36. - управляющий сигнал разрешение по выбору оперативного запоминающего устройства блока памяти третьего.

37. СГУ - информационный сигнал, поступающий из блока управления, состоящий из управляющих сигналов, формирующих работу оперативного запоминающего устройства блока памяти второго: выбора микросхемы, записи считывания, разрешение по выбору.

38. СГУО - информационный сигнал, поступающий из блока управления, состоящий из управляющих сигналов, формирующих работу оперативного запоминающего устройства блока памяти четвертого: выбора микросхемы, записи считывания, разрешение по выбору.

39. - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти второго.

40. CS22 - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти второго.

41. - управляющий сигнал записи считывания информации оперативного запоминающего устройства блока памяти второго.

42. - управляющий сигнал разрешение по выбору оперативного запоминающего устройства блока памяти второго.

43. - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти четвертого.

44. CS25 - управляющий сигнал выбора микросхемы оперативного запоминающего устройства блока памяти четвертого.

45. - управляющий сигнал записи считывания информации оперативного запоминающего устройства блока памяти четвертого.

46. - управляющий сигнал разрешение по выбору оперативного запоминающего устройства блока памяти четвертого.

47. ДКЧС - информационный двоичный код положительных чисел и символов, поступающих с выхода шифратора блока ввода данных.

48. ДКОЧС - информационный двоичный код отрицательных чисел, поступающих с выхода шифратора блока ввода данных.

49. БЭК1 - блок электронных ключей первый.

50. БФАБП1 - блок формирования адреса и блок памяти первый.

51. БФА1 - блок формирования адреса первый.

52. БПАМ1 - блок памяти первый.

53. БФАБП2 - блок формирования адреса и блок памяти второй.

54. БФАБП3 - блок формирования адреса и блок памяти третий.

55. БФАБП4 - блок формирования адреса и блок памяти четвертый.

56. БФА2 - блок формирования адреса второй.

57. БФА3 - блок формирования адреса третий.

58. БФА4 - блок формирования адреса четвертый.

59. БПАМ2 - блок памяти второй.

60. БПАМ3 - блок памяти третий.

61. БПАМ4 - блок памяти четвертый.

62. ДКАСР - двоичный код адреса строк оперативного запоминающего устройства блока памяти первого, информационный сигнал, поступающий из блока формирования адреса первого.

63. ДКАСРО - двоичный код адреса строк оперативного запоминающего устройства блока памяти третьего, информационный сигнал, поступающий из блока формирования адреса третьего.

64. ДКАСЛ - двоичный код адреса столбцов оперативного запоминающего устройства блока памяти первого, информационный сигнал, поступающий из блока формирования адреса первого.

65. ДКАСЛО - двоичный код адреса столбцов оперативного запоминающего устройства блока памяти третьего, информационный сигнал, поступающий из блока формирования адреса третьего.

66. ДКАСС - информационный сигнал, формирующий адресную шину строк оперативного запоминающего устройства блока памяти второго, поступающий с выходов логических схем ИЛИ блока формирования адреса второго.

67. ДКАССО - информационный сигнал, формирующий адресную шину строк оперативного запоминающего устройства блока памяти четвертого, поступающий с выходов логических схем ИЛИ блока формирования адреса четвертого.

68. ДКАСТ - информационный сигнал, формирующий адресную шину столбцов оперативного запоминающего устройства блока памяти второго, поступающий с выходов логических схем ИЛИ блока формирования адреса второго.

69. ДКАСТО - информационный сигнал, формирующий адресную шину столбцов оперативного запоминающего устройства блока памяти четвертого, поступающий с выходов логических схем ИЛИ блока формирования адреса четвертого.

70. ПЧС - упорядоченные положительные числа, информационный сигнал, поступающий из блока памяти первого.

71. ОЧС - упорядоченные отрицательные числа, информационный сигнал, поступающий из блока памяти третьего.

72. КПЧ - количество одинаковых положительных чисел, информационный сигнал, поступающий из блока памяти второго.

73. КОЧ - количество одинаковых отрицательных чисел, информационный сигнал, поступающий из блока памяти четвертого.

74. ГИ - генератор прямоугольных импульсов, поступающих на суммирующий вход двоичного счетчика Сч1, формирующего адреса строк, блока формирования адреса первого.

75. ОБН - управляющий сигнал установки в нулевое состояние двоичного счетчика Сч1, формирующего адреса строк, блока формирования адреса первого.

76. ТИ - генератор тактовых импульсов, поступающих на суммирующий вход двоичного счетчика Сч2, формирующего адреса столбцов, блока формирования адреса первого.

77. УС0 - управляющий сигнал установки в нулевое состояние двоичного счетчика Сч2, формирующего адреса столбцов, блока формирования адреса первого.

78. УСН - управляющий сигнал установки в нулевое состояние двоичного счетчика Сч3, формирующего адреса строк, блока хранения результата.

79. ОБЛ - управляющий сигнал установки в нулевое состояние двоичного счетчика Сч4, формирующего адреса столбцов, блока хранения результата.

80. ГНИ - прямоугольные импульсы, поступающие с выхода генератора сигналов блока управления на суммирующий вход двоичного счетчика Сч3 блока хранения результата.

81. ТАИ - тактовые импульсы, поступающие с выхода генератора сигналов блока управления на суммирующий вход двоичного счетчика Сч4 блока хранения результата.

82. - управляющий сигнал выбора микросхемы третьего оперативного запоминающего устройства блока хранения результата.

83. CS23 - управляющий сигнал выбора микросхемы третьего оперативного запоминающего устройства блока хранения результата.

84. - управляющий сигнал записи считывание информации третьего оперативного запоминающего устройства блока хранения результата.

85. - управляющий сигнал разрешение по выбору третьего оперативного запоминающего устройства блока хранения результата.

86. ВУИ - выходной упорядоченный информационный сигнал, поступающий с выхода третьего оперативного запоминающего устройства блока хранения результата.

87. АДСТР - информационный сигнал, формирующий адресную шину строк, поступающий на информационные входы логической схемы И с выхода двоичного счетчика Сч1 блока формирования адреса первого.

88. АДСТЛ - информационный сигнал, формирующий адресную шину столбцов, поступающий на информационные входы логической схемы И с выхода двоичного счетчика Сч2 блока формирования адреса первого.

89. АДСТРР - информационный сигнал, формирующий адресную шину строк, поступающий на информационные входы оперативного запоминающего устройства ОЗУ3 с выхода двоичного счетчика Сч3 блока хранения результата.

90. АДСТЛР - информационный сигнал, формирующий адресную шину столбцов, поступающий на информационные входы оперативного запоминающего устройства ОЗУ3 с выхода двоичного счетчика Сч4 блока хранения результата.

91. АДСТРО - информационный сигнал, формирующий адресную шину строк, поступающий на информационные входы логической схемы И с выхода двоичного счетчика Сч5 блока формирования адреса третьего.

92. АДСТЛО - информационный сигнал, формирующий адресную шину столбцов, поступающий на информационные входы логической схемы И с выхода двоичного счетчика Сч6 блока формирования адреса третьего.

93. КПОЧ - информационный сигнал, отображающий количество входных одинаковых положительных чисел, поступающий с выхода сумматора на вход шинного формирователя блока памяти второго.

94. КОТЧ - информационный сигнал, отображающий количество входных одинаковых отрицательных чисел, поступающий с выхода сумматора на вход шинного формирователя блока памяти четвертого.

95. ПУСК - внешний управляющий сигнал блока управления, означающий пуск работы устройства сортировки информации.

96. СБРОС - внешний управляющий сигнал блока управления, означающий сброс всех элементов памяти и двоичных счетчиков в нулевое состояние устройства сортировки информации.

Работа алгоритма управления устройства сортировки информации методом преобразования данных в адрес.

Содержательная ГСА управления приведена на фиг.20а, 20б и отражает работу устройства и блока управления (фиг.1).

Блок 1 алгоритма является начальным блоком алгоритма.

В блоке 2 алгоритма подается сигнал "СБРОС" установки в нулевое состояние на входы всех элементов устройства сортировки.

В блоке 2 алгоритма по команде «ОБН:=1» подается управляющий сигнал обнуления двоичного счетчика Сч1 блока формирования адреса первого, по команде «УС0:=1» подается управляющий сигнал обнуления двоичного счетчика Сч2 блока формирования адреса первого, по команде «ОБЛ:=1» подается управляющий сигнал обнуления двоичного счетчика Сч4 блока хранения результата, по команде «УСН:=1» подается управляющий сигнал обнуления двоичного счетчика Сч3 блока хранения результата, по команде «ОБНЛ:=1» подается управляющий сигнал обнуления двоичного счетчика Сч5 блока формирования адреса третьего, по команде «УСН0:=1» подается управляющий сигнал обнуления двоичного счетчика Сч6 блока формирования адреса первого.

В блоке 4 алгоритма подается внешний управляющий сигнал «ПУСК», означающий начала работы устройства.

В блоке 5 проверяется признак завершения ввода информационного двоичного кода числовых и символьных данных. Если ввод не завершен, то выполняется переход на блок 6, если все данные введены в устройство, то осуществляется переход на блоки 21 и 43 алгоритма.

В блоке 6 алгоритма по командам «БСПЧ:=ЧСД» и «БСОЧ:=ЧСД» двоичный код числовых и символьных данных поступает на входы блоков сортировки положительных и отрицательных чисел соответственно.

В блоке 7 анализируется знаковый разряд двоичного числа. Если знаковый разряд равен единичному значению, то осуществляется переход на блок 30 алгоритма, в случае равенства знакового разряда нулю происходит переход на блок 8 алгоритма.

В блоках 8-20 алгоритма выполняется упорядочение положительных чисел и символьных данных.

В блоке 8 по команде "ОЗУ1:=СИУ" на управляющие входы первого оперативного запоминающего устройства подается информационный сигнал, формирующий работу ОЗУ1 блока памяти первого, в состав информационного сигнала СИУ входят управляющие сигналы: выбора микросхемы, записи, считывания, разрешение по выбору.

В блоке 9 по команде «» поступает управляющий сигнал разрешения записи информации в первое оперативное запоминающее устройство блока памяти первого.

В блоке 10 по командам «ДКАСР:=ДКЧС», «ДКАСЛ:=ДКЧС» осуществляется формирование адресов строк и столбцов первого оперативного запоминающего устройства блока памяти первого.

В блоке 11 по командам «ОЗУ1:=ДКАСР» и «ОЗУ1:=ДКАСЛ» осуществляется подача адресов строк и столбцов на входы первого оперативного запоминающего устройства блока памяти первого.

В блоке 12 по команде «ОЗУ1:=ПЧС» информационная последовательность в виде символов и числовых данных записывается в первое оперативное запоминающее устройство блока памяти первого.

В блоке 13 по команде «ОЗУ2:=СГУ» на управляющие входы второго оперативного запоминающего устройства подается информационный сигнал, формирующий работу ОЗУ2 блока памяти второго, в состав информационного сигнала СГУ входят управляющие сигналы: выбора микросхемы, записи, считывания, разрешение по выбору.

В блоке 14 по командам «ДКАСС:=ДКЧС» и «ДКАСТ:=ДКЧС» осуществляется формирование адресов строк и столбцов на входы второго оперативного запоминающего устройства блока памяти второго.

В блоке 15 по команде «» подается управляющий сигнал разрешения чтения информации из второго оперативного запоминающего устройства блока памяти второго.

В блоке 16 по команде «ШФР1:=КПЧ» на вход первого шинного формирователя блока памяти второго поступает выходной информационный сигнал с выхода второго оперативного запоминающего устройства блока памяти второго. По команде «СУМ1:=КПЧ» на вход первого сумматора блока памяти второго поступает выходной информационный сигнал с выхода первого шинного формирователя блока памяти второго.

В блоке 17 по команде «КПОЧ:=КПЧ+1» выходной информационный сигнал первого сумматора СУМ1, соответствующий количеству одинаковых символов и положительных чисел, увеличивается на единицу.

В блоке 18 по команде «ШФР1:=КПОЧ» на вход первого шинного формирователя блока памяти второго поступает выходной информационный сигнал с выхода первого сумматора блока памяти второго.

В блоке 19 по команде «» подается управляющий сигнал, равный нулевому значению, для разрешения записи информации во второе оперативное запоминающее устройство блока памяти второго.

В блоке 20 по команде «ОЗУ2:=КПОЧ» производится запись во второе оперативное запоминающее устройство количества одинаковых символов и положительных чисел блока памяти второго.

В блоках 21-29 алгоритма осуществляется вывод упорядоченных в алфавитном порядке и количество одинаковых символов и положительных чисел.

В блоке 21 по команде «ОЗУ1:=СИУ» на управляющие входы первого оперативного запоминающего устройства подается информационный сигнал СИУ из блока управления, формирующий работу ОЗУ1 блока памяти первого: выбора микросхемы, записи, считывания, разрешение по выбору, по команде «ОЗУ2:=СГУ» на управляющие входы второго оперативного запоминающего устройства подается информационный сигнал СГУ из блока управления, формирующий работу ОЗУ2 блока памяти второго: выбора микросхемы, записи, считывания, разрешение по выбору.

В блоке 22 по команде подается управляющий сигнал на вход первого оперативного запоминающего устройства блока памяти первого для разрешения чтения информации. По команде « подается управляющий сигнал на вход второго оперативного запоминающего устройства блока памяти второго для разрешения чтения информации.

В блоке 23 по команде «ДКАСР:=АДСТР» происходит формирование адресов строк первого оперативного запоминающего устройства блока памяти первого, по команде «ДКАСЛ:=АДСТЛ» происходит формирование адресов столбцов первого оперативного запоминающего устройства блока памяти первого.

В блоке 24 по командам «ОЗУ1:=ДКАСР» и «ОЗУ1:=ДКАСЛ» осуществляется подача адресов строк и столбцов на входы первого оперативного запоминающего устройства блока памяти первого.

В блоке 25 по команде «ДКАСС:=ДКАСР» » происходит подача адресов строк на адресные входы второго оперативного запоминающего устройства блока памяти второго, по команде «ДКАСТ:=ДКАСЛ» происходит подача адресов столбцов на адресные входы второго оперативного запоминающего устройства блока памяти второго.

В блоке 26 по команде «ПЧК:=КПЧ U ПЧС» из информационного сигнала упорядоченных положительных чисел и символов ПЧС, поступающего из блока памяти первого, и информационного сигнала количества одинаковых положительных чисел и символов КПЧ, поступающего из блока памяти второго, формируется информационный двоичный код положительных чисел и количества одинаковых входных данных ПЧК. По этой команде происходит объединение двух информационных сигналов в один.

В блоке 27 по команде «БХР:=ГНИ» прямоугольные импульсы поступают с выхода генератора сигналов блока управления на суммирующий вход двоичного счетчика Сч3 блока хранения результата. По команде «БХР:=ТАИ» тактовые импульсы поступают с выхода генератора сигналов блока управления на суммирующий вход двоичного счетчика Сч4 блока хранения результата.

В блоке 28 по команде «» подается управляющий сигнал из блока управления, равный нулевому значению для разрешения записи входной информации в оперативное запоминающее устройство блока хранения результата.

В блоке 29 по команде «ОЗУ3:=ПЧК» в оперативное запоминающее устройство блока хранения результата записывается информационный двоичный код, состоящий из упорядоченных положительных чисел и символов, а также количества одинаковых входных данных.

В блоках 30-42 алгоритма выполняется упорядочение отрицательных чисел.

В блоке 30 по команде "ОЗУ4:=СИУО" на управляющие входы четвертого оперативного запоминающего устройства подается информационный сигнал, формирующий работу ОЗУ блока памяти третьего, в состав информационного сигнала СИУО входят управляющие сигналы: выбора микросхемы, записи, считывания, разрешение по выбору.

В блоке 31 по команде «» поступает управляющий сигнал разрешения записи информации в четвертое оперативное запоминающее устройство блока памяти третьего.

В блоке 32 по командам «ДКАСРО:=ДКОЧС», «ДКАСЛО:=ДКОЧС» осуществляется формирование адресов строк и столбцов четвертого оперативного запоминающего устройства блока памяти третьего.

В блоке 33 по командам «ОЗУ4:=ДКАСРО» и «ОЗУ4:=ДКАСЛО» осуществляется подача адресов строк и столбцов на входы четвертого оперативного запоминающего устройства блока памяти третьего.

В блоке 34 по команде «ОЗУ4:=ОЧС» информационная последовательность в виде числовых отрицательных чисел записывается в четвертое оперативное запоминающее устройство блока памяти третьего.

В блоке 35 по команде «ОЗУ5:=СГУО» на управляющие входы пятого оперативного запоминающего устройства подается информационный сигнал, формирующий работу ОЗУ5 блока памяти четвертого, в состав информационного сигнала СГУО входят управляющие сигналы: выбора микросхемы, записи, считывания, разрешение по выбору.

В блоке 36 по командам «ДКАССО:=ДКОЧС» и «ДКАСТО:=ДКОЧС» осуществляется формирование адресов строк и столбцов на входы пятого оперативного запоминающего устройства блока памяти четвертого.

В блоке 37 по команде « подается управляющий сигнал разрешения чтения информации из пятого оперативного запоминающего устройства блока памяти четвертого.

В блоке 38 по команде «ШФР2:=КОЧ» на вход второго шинного формирователя блока памяти четвертого поступает выходной информационный сигнал с выхода пятого оперативного запоминающего устройства блока памяти четвертого. По команде «СУМ2:=КОЧ» на вход второго сумматора блока памяти четвертого поступает выходной информационный сигнал с выхода второго шинного формирователя блока памяти четвертого.

В блоке 39 по команде «КОТЧ:=КОЧ+1» выходной информационный сигнал второго сумматора СУМ2, соответствующий количеству одинаковых отрицательных чисел, увеличивается на единицу.

В блоке 40 по команде «ШФР2:=КОТЧ» на вход второго шинного формирователя блока памяти четвертого поступает выходной информационный сигнал с выхода второго сумматора блока памяти четвертого.

В блоке 41 по команде «» подается управляющий сигнал, равный нулевому значению, для разрешения записи информации в пятое оперативное запоминающее устройство блока памяти четвертого.

В блоке 42 по команде «ОЗУ5:=КОТЧ» осуществляется запись в пятое оперативное запоминающее устройство количества одинаковых отрицательных чисел блока памяти четвертого.

В блоках 43-51 осуществляется вывод результатов сортировки в алфавитном порядке отрицательных чисел.

В блоке 43 по команде «ОЗУ4:=СИУО» на управляющие входы четвертого оперативного запоминающего устройства подается информационный сигнал СИУО из блока управления, формирующий работу ОЗУ4 блока памяти третьего: выбора микросхемы, записи, считывания, разрешение по выбору. По команде «ОЗУ5:=СГУО» на управляющие входы пятого оперативного запоминающего устройства подается информационный сигнал СГУО из блока управления, формирующий работу ОЗУ5 блока памяти четвертого: выбора микросхемы, записи, считывания, разрешение по выбору.

В блоке 44 по команде подается управляющий сигнал на вход четвертого оперативного запоминающего устройства блока памяти третьего для разрешения чтения информации. По команде « подается управляющий сигнал на вход пятого оперативного запоминающего устройства блока памяти четвертого для разрешения чтения информации.

В блоке 45 по команде «ДКАСРО:=АДСТРО» происходит формирование адресов строк четвертого оперативного запоминающего устройства блока памяти третьего. По команде «ДКАСЛО:=АДСТЛО» происходит формирование адресов столбцов четвертого операти