Блок сменный кодовый

Иллюстрации

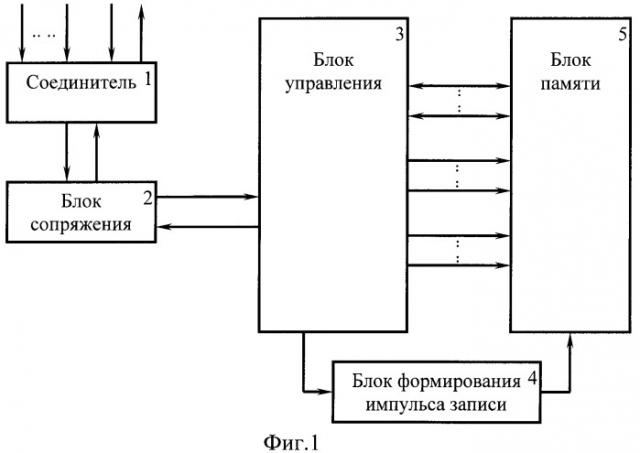

Показать всеИзобретение относится к технике защиты различных объектов от доступа посторонних лиц, в частности, к носителям информации. Достигаемый технический результат - повышение надежности и срока службы блока кодового сменного, а также в увеличении срока хранения информации. Блок сменный кодовый содержит соединитель (1), блок (2) сопряжения, блок (3) управления, блок (4) формирования импульса записи и блок (5) памяти. Первые вход и выход блока (2) сопряжения соединены соответственно с выходом и входом соединителя (1). Вход и первый выход блока (3) управления соединены соответственно со вторым выходом и вторым входом блока (2) сопряжения, а второй выход блока (3) управления соединен с входом блока (4) формирования импульса записи, выход которого соединен с входом блока (5) памяти. Группа входов-выходов и две группы входов блока (5) памяти соединены, соответственно, с группой входов-выходов и двумя группами выходов блока (3) управления. 4 ил.

Реферат

Изобретение относится к технике защиты различных объектов от доступа посторонних лиц, в частности, к носителям информации.

Известен блок кодовый сменный (см. патент Франции №2642544, кл. G06K 19/07, опубл. 1990), содержащий встроенное электрически стираемое программируемое постоянное запоминающее устройство и магнитную полосу.

Недостатками известного устройства являются незначительный срок службы из-за наличия магнитной полосы и малый срок хранения информации.

Наиболее близким по совокупности существенных признаков к предлагаемому изобретению является блок кодовый сменный (см. свидетельство РФ на полезную модель №5273 от 28.09.94 «Интеллектуальная карта»: G06K 19/07, Чудновский Г.А., Абрамович A.M., опубл. 16.10.97, Бюл. №10), содержащий электрически стираемое программируемое постоянное запоминающее устройство (блок памяти) и магнитную полосу.

Недостатками известного устройства являются незначительные срок службы и надежность, обусловленные наличием магнитной полосы, и малый срок хранения информации из-за отсутствия устройств, создающих специализированные условия при записи информации для продолжительного ее хранения.

Технический результат заключается в повышении надежности и срока службы блока сменного кодового, а также в увеличении срока хранения информации.

Этот технический результат достигается тем, что в блок сменный кодовый, содержащий блок памяти, дополнительно введены последовательно соединенные соединитель, блок сопряжения, блок управления, блок формирования импульса записи, выход которого соединен с входом блока памяти, группа входов-выходов и две группы входов которого соединены соответственно с группой входов-выходов и двумя группами выходов блока управления, второй выход которого соединен со вторым входом блока сопряжения, второй выход которого соединен с входом соединителя, информационные выход и вход и группа входов которого являются соответственно выходом и входами блока кодового сменного.

Указанная совокупность существенных признаков позволяет повысить надежность и срок службы кодового устройства за счет исключения магнитной полосы и обеспечить длительное хранение информации за счет введения блока формирования импульса записи.

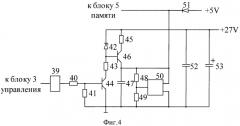

На фиг.1 представлена функциональная схема блока сменного кодового, на фиг.2 представлена схема блока сопряжения, на фиг.3 - схема блока управления, на фиг.4 - схема блока формирования импульса записи.

Блок сменный кодовый (см. фиг.1) содержит соединитель 1, блок 2 сопряжения, блок 3 управления, блок 4 формирования импульса записи и блок 5 памяти. Первый вход и второй выход блока 2 сопряжения соединены соответственно с выходом и входом соединителя 1. Вход и второй выход блока 3 управления соединены соответственно с первым выходом и вторым входом блока 2 сопряжения, а первый выход блока 3 управления соединен с входом блока 4 формирования импульса записи, выход которого соединен с входом блока 5 памяти. Группа входов-выходов и две группы входов блока 5 памяти соединены соответственно с группой входов-выходов и двумя группами выходов блока 3 управления.

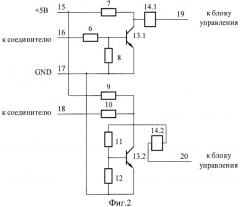

В частности, блок 2 сопряжения (фиг.2) содержит резисторы 6-12, транзисторы 13.1 и 13.2 и микросхемы 14.1 и 14.2. Первый 15 и третий 17 входы блока 2 сопряжения соединены с шинами питания (+5 В и GND, соответственно), второй вход 16 и первый выход 18 соединены с входом и выходом соединителя 1, второй выход 19 и четвертый вход 20 соединены с входом и первым выходом блока 3 управления. Вход 15 через резистор 7 соединен с коллектором транзистора 13.1 и через микросхему 14.1 с выходом 19, а через резистор 9 - с коллектором транзистора 13.2. Эмиттер транзистора 13.2 соединен с шиной 17 GND и через резистор 12 соединен со своей базой. Вход 16 через резистор 6 подключен к базе транзистора 13.1 и через резистор 8 к шине 17 GND, к которой подключен эмиттер транзистора 13.1. Вход 20 через последовательно соединенные микросхему 14.2 и резистор 11 подключен к базе транзистора 13.2, коллектор которого через резистор 10 подключен к выходу 18.

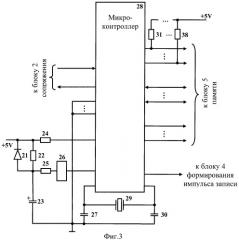

В частности, блок 3 управления (фиг.3) содержит диод 21, резисторы 22, 24, 25, 31…38, конденсаторы 23, 27, 30, микроконтроллер 28 и резонатор 29. Первые вход и выход микроконтроллера 28 соединены с блоком 2 сопряжения. Первая группа входов микроконтроллера 28 соединена с общей шиной, второй вход через резистор 24 соединен с шиной питания (+5 V), катодом диода 21 и первым выводом резистора 22. Третий вход микроконтроллера 28 через последовательно соединенные микросхему 26 и резистор 25 соединен с анодом диода 21 и вторым выводом резистора 22, который через конденсатор 23 подключен к общей шине. Второй выход микроконтроллера 28 подключен к блоку 4 формирования импульса записи. Третий выход микроконтроллера 28 подключен к первому выводу резонатора 29 и через конденсатор 27 к общей шине, а четвертый выход - подключен ко второму выводу резонатора 29 и через конденсатор 30 к общей шине. Каждый выход первой группы выходов микроконтроллера 28 соединен через соответствующий резистор 31…38 с шиной питания (+5 V) и непосредственно с блоком 5 памяти. Вторая группа выходов и группа входов-выходов микроконтроллера 28 соединены с блоком 5 памяти.

Блок 4 формирования импульса записи (фиг.4) содержит микросхемы 39 и 50, резисторы 40, 41, 43, 45, 48 и 49, транзисторы 44 и 46, диод 51, стабилитрон 42 и конденсаторы 47, 52 и 53. Вход блока 4 формирования импульса записи соединен через последовательно соединенные микросхему 39 и резистор 40 с базой транзистора 44, и через резистор 41 с общей шиной. Эмиттер транзистора 44 соединен с общей шиной, а коллектор транзистора 44 через резистор 43 соединен с базой транзистора 46 и через стабилитрон 42 с шиной питания (+27 V). Коллектор транзистора 46 через резистор 45 соединен с шиной питания (+27 V). Эмиттер транзистора 46 соединен с первым выводом микросхемы 50, через резистор 48 со вторым выводом микросхемы 50, а через конденсатор 47 с общей шиной. Третий вывод микросхемы 50 через резистор 49 и второй вывод микросхемы 50 соединены с общей шиной. Первый вывод микросхемы 50 соединен с выходом блока 4 формирования импульса записи и через диод 51 с шиной питания (+5 V). Второй вывод микросхемы 50 через параллельно соединенные конденсаторы 52 и 53 соединен с шиной питания (+27 V).

Блок сменный кодовый (фиг.1) работает следующим образом.

Перед началом работы блок сменный кодовый подключается к устройству управления (на фигурах не показано). Обмен информацией производится через блок 2 сопряжения и соединитель 1 по двухпроводной линии связи (на фигурах не показана) в дуплексном режиме обмена при помощи команд, имеющих следующий формат: код операции, имя операнда, размерность, данные. Код операции определяет тип выполняемой команды. Имя операнда предназначено для поиска операнда, с которым производится действие, размерность - для определения его размера. Операнд, находящийся в блоке 5 памяти, имеет следующий формат: имя операнда, размерность и данные операнда. Т.е. в блоке 5 памяти сначала размещается имя операнда, затем - размерность, а потом - данные.

После подключения указанных цепей к соединителю 1 из устройства управления в блок 3 управления поступает команда выбора модуля, по которой производится поиск модуля в блоке 5 памяти. При условии нахождения данного модуля из устройства управления поступает команда сравнения, по которой производится поиск кода защиты модуля в блоке 5 памяти. Код защиты считывается в блок 3 управления, где производится его сравнение с данными, поступившими в составе команды сравнения. В случае их равенства блок 3 управления разрешает работу с данным модулем. Устройство управления функционирует совместно с блоком сменным кодовым. Для проверки наличия блока сменного кодового устройство управления во время работы проводит контроль идентификатора (признака) блока сменного кодового. Идентификатор выполнен в виде перемычки заданных цепей. Контроль идентификатора производится при помощи команды чтения. При необходимости код защиты модуля в блоке 5 памяти может быть изменен. Для этого в блок 3 управления поступает команда записи данных, соответствующих новому коду защиты модуля. По этой команде блок 3 управления формирует информационные и управляющие сигналы на выводах блока 5 памяти и формирует импульс управления в блок 4 формирования импульса записи. Блок 4 формирования импульса записи формирует сигнал записи, который поступает на соответствующий вход блока 5 памяти. По окончании записи нового кода защиты модуля блок 3 управления передает в устройство управления команду об окончании записи, а устройство управления передает в блок 3 управления команду сравнения с новым кодом защиты модуля. По этой команде в блоке 3 управления производится сравнение нового кода защиты модуля, считанного из блока 5 памяти с данными, поступившими в составе команды сравнения. В случае положительного результата производится уничтожение старого кода защиты модуля путем программирования каждого бита кода защиты с уровнем логической единицы до уровня логического нуля.

Блок 2 сопряжения (фиг.2) работает следующим образом.

Блок 2 сопряжения начинает работать сразу после подачи напряжения (+5 V) на соответствующие выводы. Появление информационного сигнала низкого уровня напряжения (признак начала информационного обмена) на входе 16 приводит к запиранию транзистора 13.1 и формированию на его коллекторе сигнала высокого уровня напряжения, поступающего на вход микросхемы 14.1. Микросхема 14.1 инвертирует полученный сигнал и передает его в блок 3 управления. Информационный сигнал низкого уровня напряжения (признак начала информационного обмена) на входе 20 блока 2 сопряжения инвертируется микросхемой 14.2, преобразуясь в сигнал высокого уровня напряжения, который, поступая в базу транзистора 13.2, вызывает его отпирание. Это обуславливает появление на коллекторе транзистора 13.2 сигнала низкого уровня напряжения, который передается на выход 18 блока 2 сопряжения.

Блок 3 управления (фиг.3) работает следующим образом.

После подачи напряжения питания (+5 V) интегрирующая цепь, состоящая из диода 21, резисторов 22 и 25 и конденсатора 23, формирует импульс сброса, который, передаваясь через микросхему 26, приводит микроконтроллер 28 в исходное состояние. После этого микроконтроллер 28 начинает свою работу под управлением программы, находящейся в нем. Микроконтроллер 28 производит обмен информацией с блоком 2 сопряжения и блоком 5 памяти через соответствующие выводы. Для обращения к блоку 5 памяти микроконтроллер 28 формирует адрес, по которому производится обращение. Резисторы 31…38 являются нагрузкой адресных выводов, имеющих открытый выход.

Блок 4 формирования импульса записи (фиг.4) работает следующим образом.

На вход блока 4 формирования импульса записи поступает сигнал низкого уровня напряжения определенной длительности, который, инвертируясь микросхемой 39, поступает в базу транзистора 44. Появление в базе транзистора 44 сигнала с высоким уровнем напряжения вызывает его отпирание и запитывание цепей параметрического стабилизатора напряжения, в состав которого входят резисторы 43 и 45, стабилитрон 42 и транзистор 46. Сигнал, сформированный параметрическим стабилизатором, поступает на входы микросхемы 50, откуда передается на выход блока 4 формирования импульса записи.

Соединитель 1 (фиг.1) может быть представлен вилкой РПММ1-11Ш3-В. Блок 5 памяти (фиг.1) может быть выполнен на микросхеме 558РР4У3. В качестве микросхем 14.1, 14.2 (фиг.2), 26 (фиг.3) и 39 (фиг.4) может быть использована микросхема 1554ТЛ2. Микроконтроллер 28 (фиг.3) может быть выполнен на микросхеме Н1880ВЕ51У. В качестве микросхемы 50 (фиг.4) может быть использована микросхема Н142ЕН19.

Изготовлен лабораторный макет блока сменного кодового, испытания которого подтвердили работоспособность и практическую ценность заявляемого объекта.

Блок сменный кодовый, содержащий блок управления, блок памяти, последовательно соединенные соединитель и блок сопряжения, предназначенные соответственно для обмена информацией и согласования информационных сигналов с внешним устройством управления, отличающийся тем, что содержит выполненный в виде перемычки заданных цепей идентификатор, блок формирования импульса записи, а блок управления выполнен на основе микроконтроллера; при этом идентификатор предназначен для проверки внешним устройством управления наличия блока сменного кодового при поступлении из внешнего устройства управления команды чтения; микроконтроллер предназначен для приема от внешнего устройства управления команды выбора модуля в блоке памяти и поиска соответствующего модуля в блоке памяти, приема от внешнего устройства управления при условии нахождения в блоке памяти соответствующего модуля команды сравнения для осуществления поиска в блоке памяти кода защиты упомянутого модуля и сравнения его с данными, поступившими в составе команды сравнения, разрешения работы с данным модулем в случае совпадения упомянутых данных; приема команды записи данных для изменения кода защиты модуля блока памяти, формирования на основании данной команды информационных и управляющих сигналов на соответствующие выводы блока памяти и импульса управления на блок формирования импульса записи для подачи на соответствующий вход блока памяти сигнала записи; передачи во внешнее устройство управления команды об окончании записи; приема от внешнего устройства управления команды на сравнение с новым кодом защиты модуля блока памяти и уничтожения старого кода защиты модуля блока памяти в случае положительного результата данного сравнения.