Устройство шифрования и дешифрования формализованных сообщений хэширующей функцией

Иллюстрации

Показать всеИзобретение относится к области электросвязи, а именно к передаче зашифрованных формализованных сообщений. Техническим результатом является повышение достоверности передачи формализованных сообщений по каналам связи с помехами и имитозащита. Технический результат достигается тем, что устройство шифрования и дешифрования формализованных сообщений хэширующей функцией, включающее передающий и приемный узлы, в передающем узле с помощью итерационного хэширования криптограммы по методу Уинтерница получает дайджест, соответствующий криптограмме, причем присоединение дайджеста к криптограмме происходит в модуле памяти криптограммы, затем комбинация дайджеста и криптограммы передается по прямому каналу связи, затем в приемном узле принятый дайджест записывается в блок выделения дайджеста, затем вычисляется дайджест, соотвествующий принятой криптограмме путем итерационного хэширования блоков принятой криптограммы, идентично аналогичному процессу в передающем узле, затем полученный дайджест сравнивается с принятым дайджестом, причем при совпадении дайджестов принятое сообщение поступает на выход устройства, а при их несовпадении формируется сигнал «запрос», который по обратному каналу связи поступает в передающий узел для повтора криптограммы, в которой обнаружена ошибка или модификация. 3 ил.

Реферат

Предлагаемое изобретение относится к области электросвязи, а именно к передаче зашифрованных формализованных сообщений, и может найти применение в системах передачи телеграфной, факсимильной, командно-кодовой и других видов конфиденциальной информации, в которых объем сообщения известен до начала его передачи.

Наиболее близким по своей технической сущности к предлагаемому устройству является устройство шифрования и дешифрования сообщений хэширующей функцией, описанное в патенте США 5483598, МПК6 Н04L 9/20 от 09.01.96 г. Устройство-прототип состоит из передающего и приемного узлов. Передающий узел включает модуль памяти сообщения, модуль памяти секретного ключа, модуль памяти стартового блока, модуль памяти предыдущего хэшированного блока, модуль памяти блока криптограмм, блок коммутации, блок хэширования и сумматор по модулю два. Приемный узел включает модуль памяти принятой криптограммы, модуль памяти секретного ключа, модуль памяти стартового блока, модуль памяти предыдущего хэшированного блока, блок коммутации, блок хэширования и сумматор по модулю два. В передающем узле вход модуля памяти сообщения является входом устройства, первый вход блока хэширования подключен к выходу модуля памяти секретного ключа, а второй вход блока хэширования соединен с выходом блока коммутации, первый вход которого подключен к выходу модуля памяти стартового блока, а второй вход подключен к выходу модуля памяти предыдущего хэшированного блока, выход модуля памяти сообщения соединен с первым входом сумматора по модулю два, выход блока хэширования соединен со вторым входом сумматора по модулю два и с входом модуля памяти предыдущего хэшированного блока, выход сумматора по модулю два соединен с входом модуля памяти криптограмм, выход модуля памяти криптограмм соединен с входом канала связи. В приемном узле вход модуля памяти принятой криптограммы соединен с выходом канала связи, выход модуля памяти принятой криптограммы соединен с первым входом сумматора по модулю два, выход модуля памяти стартового блока соединен с первым входом блока коммутации, второй вход блока коммутации соединен с выходом модуля памяти предыдущего хэшированного блока, выход блока коммутации соединен с первым входом блока хэширования, второй вход блока хэширования соединен с выходом модуля памяти секретного ключа, выход блока хэширования соединен со вторым входом сумматора по модулю два и с входом модуля памяти предыдущего хэшированного блока, выход сумматора по модулю два является выходом устройства.

Недостатком устройства-прототипа является низкая достоверность передачи по каналам связи с помехами.

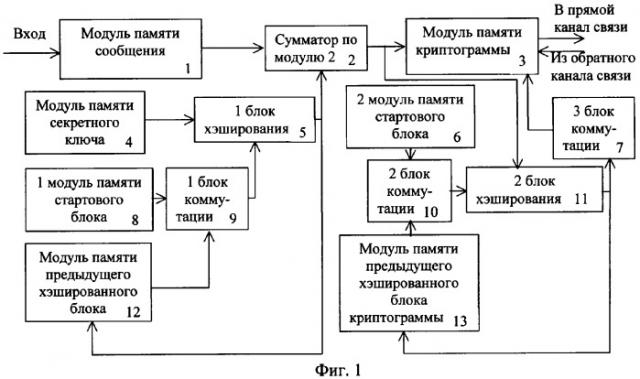

Сущность изобретения заключается в том, что в передающий узел дополнительно введены второй и третий блоки коммутации, второй модуль памяти стартового блока, второй блок хэширования, модуль памяти предыдущего хэшированного блока криптограммы, а в приемный узел дополнительно введены модуль памяти принятого сообщения, блок выделения дайджеста, блок сравнения дайджестов, второй и третий блоки коммутации, второй модуль памяти стартового блока, второй блок хэширования, модуль памяти предыдущего хэшированного блока криптограммы. В передающем узле второй вход модуля памяти криптограммы соединен с выходом обратного канала связи, третий вход модуля памяти криптограммы соединен с выходом третьего блока коммутации, первый вход второго блока хэширования соединен с выходом сумматора по модулю два, второй вход второго блока хэширования соединен с выходом второго блока коммутации, выход модуля памяти криптограммы соединен с входом прямого канала связи, первый вход второго блока коммутации соединен с выходом модуля памяти предыдущего хэшированного блока криптограммы, второй вход второго блока коммутации соединен с выходом второго модуля памяти стартового блока, выход второго блока хэширования соединен с входом третьего блока коммутации и с входом модуля памяти предыдущего хэшированного блока криптограммы.

Структурная схема передающего узла предлагаемого устройства приведена на фиг.1.

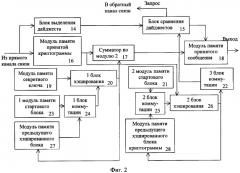

В приемном узле вход блока выделения дайджеста соединен с выходом прямого канала связи, выход блока выделения дайджеста соединен с первым входом блока сравнения дайджестов, второй вход блока сравнения дайджестов соединен с выходом третьего блока коммутации, первый вход модуля памяти принятого сообщения соединен с выходом сумматора по модулю два, первый выход блока сравнения дайджестов соединен с входом обратного канала связи, второй выход блока сравнения дайджестов соединен со вторым входом модуля памяти принятого сообщения, первый вход второго блока коммутации соединен с выходом второго модуля памяти стартового блока, второй вход второго блока коммутации соединен с выходом модуля памяти предыдущего хэшированного блока криптограммы, выход второго блока коммутации соединен с первым входом второго блока хэширования, второй вход второго блока хэширования соединен с выходом модуля памяти принятой криптограммы, выход второго блока хэширования соединен с входом третьего блока коммутации и с входом модуля памяти предыдущего хэшированного блока криптограммы, выход модуля памяти принятого сообщения является выходом устройства. Структурная схема приемного узла приведена на фиг.2.

Устройство работает следующим образом. Предварительно формируются секретный ключ, который записывается в модули памяти секретного ключа (4, 19), и стартовый блок, который записывается в первые и вторые модули памяти стартовых блоков передающего и приемного узлов (6, 8, 21, 23). Передаваемое сообщение, представленное в виде последовательного двоичного кода, поступает на вход модуля памяти сообщения (1), который разбивает его на N блоков фиксированной длины n, при необходимости дополняя последний блок до требуемой длины n путем добавления нулевых символов. По сигналам управления (на структурной схеме не показаны) информационные блоки последовательно поступают на вход сумматора по модулю два (2). Одновременно секретный ключ и стартовый блок поступают на вход первого блока хэширования (5, 20), который преобразует их по функции хэширования, например, используя функцию хэширования на основе возведения в степень примитивного элемента поля Галуа по модулям простых чисел p и g.

Математически процесс хэширования можно описать как вычисление функции секретного ключа К и предыдущего хэшированного блока Hi-1

Hi=f(Ki, Hi-1)

На первом шаге, при i=1, Н0 является стартовым боком.

Получаемый в результате такого преобразования хэш-код поступает на второй вход сумматора по модулю два, где происходит его поэлементное суммирование с информационным блоком. Зашифрованное таким образом сообщение поступает на вход модуля памяти криптограммы и запоминается. Одновременно блоки криптограммы с выхода сумматора по модулю два поступают на второй блок хэширования (11), где путем их итерационного хэширования получается дайджест криптограммы, равный длине одного блока. Процесс итерационного хэширования методом Уинтерница поясняется фиг.3. Математически этот процесс хэширования можно описать как вычисление функции блока криптограммы Еi и предыдущего хэшированного блока Hi-1.

Hi=f(Ei, Hi-1).

Первые (9, 24) и вторые (10, 25) блоки коммутации предназначены для подключения на вход соответствующих блоков хэширования стартового блока при первой итерации или предыдущего хэшированного блока при последующих итерациях. Третьи блоки коммутации (7, 22) предназначены для подключения выхода второго блока хэширования к модулю памяти криптограммы или к блоку сравнения дайджестов только на последней итерации хэширования.

Количество итераций хэширования равно количеству блоков, на которые разбивается сообщение. При выборе хэш-функции, стойкой к образованию коллизий, получается дайджест, соответствующий криптограмме. Любая модификация криптограммы приведет к изменению дайджеста.

В модуле памяти криптограммы (3) происходит присоединение дайджеста к криптограмме, запоминание этой комбинации и передача ее по прямому каналу связи.

Принятая комбинация криптограммы и дайджеста поступает на приемный узел, где разделяется. Криптограмма записывается в модуль памяти криптограммы (16), а дайджест - в блок выделения дайджеста (14). Криптограмма последовательным кодом поступает на сумматор по модулю два (17), где путем ее поэлементного суммирования с хэш-кодом, идентичным, синхронным и синфазным с хэш-кодом шифрования, происходит дешифрование. Одновременно блоки криптограммы поступают на вход второго блока хэширования (26), где путем их итерационного хэширования, идентичным аналогичному процессу в передающем узле, получается дайджест криптограммы. Дешифрованное сообщение записывается в модуль памяти принятого сообщения (18) и запоминается, а полученный дайджест поступает на второй вход блока сравнения дайджестов. При совпадении дайджестов принятое сообщение поступает на выход устройства, а при их несовпадении формируется сигнал «запрос», который по обратному каналу связи поступает в передающий узел для повтора криптограммы, в которой обнаружена ошибка или модификация.

Все элементы предлагаемого устройства могут быть реализованы на современной элементной базе,

Технико-экономический эффект от использования данного устройства заключается в повышении достоверности передачи формализованных сообщений по каналам связи с помехами и имитозащита.

Устройство шифрования и дешифрования формализованных сообщений хэширующей функцией, включающее передающий и приемный узлы, передающий узел включает модуль памяти сообщения, модуль памяти секретного ключа, модуль памяти стартового блока, модуль памяти предыдущего хэшированного блока, модуль памяти блока криптограмм, блок коммутации, блок хэширования и сумматор по модулю два, приемный узел включает модуль памяти принятой криптограммы, модуль памяти секретного ключа, модуль памяти стартового блока, модуль памяти предыдущего хэшированного блока, блок коммутации, блок хэширования и сумматор по модулю два, причем в передающем узле вход модуля памяти сообщения является входом устройства, первый вход блока хэширования подключен к выходу модуля памяти секретного ключа, а второй вход блока хэширования соединен с выходом блока коммутации, первый вход которого подключен к выходу модуля памяти стартового блока, а второй вход подключен к выходу модуля памяти предыдущего хэшированного блока, выход модуля памяти сообщения соединен с первым входом сумматора по модулю два, выход блока хэширования соединен со вторым входом сумматора по модулю два и с входом модуля памяти предыдущего хэшированного блока, выход сумматора по модулю два соединен с входом модуля памяти криптограмм, выход модуля памяти криптограмм соединен с входом канала связи, в приемном узле вход модуля памяти принятой криптограммы соединен с выходом канала связи, выход модуля памяти принятой криптограммы соединен с первым входом сумматора по модулю два, выход модуля памяти стартового блока соединен с первым входом блока коммутации, второй вход блока коммутации соединен с выходом модуля памяти предыдущего хэшированного блока, выход блока коммутации соединен с первым входом блока хэширования, второй вход блока хэширования соединен с выходом модуля памяти секретного ключа, выход блока хэширования соединен со вторым входом сумматора по модулю два и с входом модуля памяти предыдущего хэшированного блока, выход сумматора по модулю два является выходом устройства, отличающееся тем, что в передающий узел дополнительно введены второй и третий блоки коммутации, второй модуль памяти стартового блока, второй блок хэширования, модуль памяти предыдущего хэшированного блока криптограммы, а в приемный узел дополнительно введены модуль памяти принятого сообщения, блок выделения дайджеста, блок сравнения дайджестов, второй и третий блоки коммутации, второй модуль памяти стартового блока, второй блок хэширования, модуль памяти предыдущего хэшированного блока криптограммы, причем в передающем узле второй вход модуля памяти криптограммы соединен с выходом обратного канала связи, третий вход модуля памяти криптограммы соединен с выходом третьего блока коммутации, первый вход второго блока хэширования соединен с выходом сумматора по модулю два, второй вход второго блока хэширования соединен с выходом второго блока коммутации, выход модуля памяти криптограммы соединен с входом прямого канала связи, первый вход второго блока коммутации соединен с выходом модуля памяти предыдущего хэшированного блока криптограммы, второй вход второго блока коммутации соединен с выходом второго модуля памяти стартового блока, выход второго блока хэширования соединен с входом третьего блока коммутации и с входом модуля памяти предыдущего хэшированного блока криптограммы, в приемном узле вход блока выделения дайджеста соединен с выходом прямого канала связи, выход блока выделения дайджеста соединен с первым входом блока сравнения дайджестов, второй вход блока сравнения дайджестов соединен с выходом третьего блока коммутации, первый вход модуля памяти принятого сообщения соединен с выходом сумматора по модулю два, первый выход блока сравнения дайджестов соединен с входом обратного канала связи, второй выход блока сравнения дайджестов соединен со вторым входом модуля памяти принятого сообщения, первый вход второго блока коммутации соединен с выходом второго модуля памяти стартового блока, второй вход второго блока коммутации соединен с выходом модуля памяти предыдущего хэшированного блока криптограммы, выход второго блока коммутации соединен с первым входом второго блока хэширования, второй вход второго блока хэширования соединен с выходом модуля памяти принятой криптограммы, выход второго блока хэширования соединен с входом третьего блока коммутации и с входом модуля памяти предыдущего хэшированного блока криптограммы, выход модуля памяти принятого сообщения является выходом устройства.