Тепловизор на основе "смотрящей" матрицы формата 256×256

Иллюстрации

Показать всеИзобретение относится к технике формирования и передачи изображений, а точнее к тепловидению. Техническим результатом является увеличение предельной температурной чувствительности, контрастности и качества изображения. Результат достигается тем, что в тепловизор, содержащий объектив, матрицу фотоприемников (МФП), микрокриогенную систему (МКС), блок управления МКС, АЦП, ЦАП, телевизор, блок цифровой обработки, состоящий из центрального процессора, ОЗУ и ПЗУ, дополнительно введены второй АЦП, блок управления матрицей фотоприемников, блок формирования данных, блок управления с клавиатуры, клавиатура, блок прерываний, блок управления, блок формирования цифровых сигналов, блок формирования телевизионных сигналов. При этом увеличение предельной температурной чувствительности достигается за счет увеличения разрядности АЦП (14 разрядов), увеличение контрастности в области относительной интенсивности, близкой к нулю, достигается за счет некоторого сокращения квантов, выделенных для кодирования интенсивностей вне этой области, а увеличение качества изображения достигается за счет увеличения матрицы и за счет более точных калибровок механизмов обнаружения и исправления дефектных точек. 9 з.п. ф-лы, 1 табл., 14 ил.

Реферат

Изобретение относится к технике формирования и передачи изображений, а точнее к тепловидению, и может использоваться для поиска и идентификации потерь тепла и анализа выхода из строя в тепловых машинах и сетях, жилых и производственных помещениях с целью энергосбережения, а также для контроля электросетей для предотвращения аварийных ситуаций.

Известен тепловизор, в котором отсутствует ручная регулировка по эталонному источнику, так как опорная температура автоматически вводится в алгоритм обработки сигнала. [1] Указанный тепловизор содержит зеркало, служащее оптическим переключателем, с датчиком положения и приводом вращения, оптически связанный с ним источник эталонного излучения, с датчиком температуры, находящимся с ним в тепловом контакте, последовательно расположенные по ходу оптического сигнала объектив и фотоприемник (ФП), а также последовательно соединенные с ФП усилитель, аналого-цифровой преобразователь (АЦП) и микропроцессорный контроллер с блоком памяти. Сигнал с датчика температуры эталонного источника поступает в микропроцессорный контроллер и используется для вычисления температуры объекта. Оптический зеркальный переключатель попеременно направляет на ФП поток от объекта и эталонного источника. ФП преобразует оптический сигнал в электрический, который после усиления поступает на АЦП, где преобразуется в цифровую форму и заносится в память микропроцессорного контроллера. В свою очередь, в память микропроцессорного контроллера записана калибровочная кривая зависимости амплитуды сигнала, поступающего на АЦП от температуры. Сигнал с эталонного источника и сигнал с датчика температуры эталонного источника используется для автоматической корректировки калибровочной кривой сигнала по оси температур. Таким образом, достигается соответствие (привязка) выходного сигнала опорной температуре.

Недостатками известного прибора являются увеличенные габариты, обусловленные наличием эталонного источника, и связанное с этим повышенное энергопотребление, а также наличие ошибки, возникающей в результате дрейфа параметров ФП. Эта ошибка в описанном тепловизоре не может быть устранена, так как автоматическая корректировка калибровочной кривой в нем возможна только по одной точке.

Известен тепловизор на основе «смотрящей» матрицы из Cd0,2Hg0,8Те формата 128×128. [2]

Указанный тепловизор содержит матрицу фотоприемников (МФП), микрокриогенную систему типа Сплит-Стирлинга, ИК-объектив с фокусным расстоянием 70 мм и относительным отверстием 1:1,5, аналого-цифровой преобразователь (АЦП) и блок цифровой обработки, первый выход которого соединен с первым входом МФП, второй вход которой соединен со вторым выходом блока цифровой обработки, третий выход которого соединен с телевизором, причем первый вход блока цифровой обработки соединен с первым выходом МФП, третий вход которой соединен с выходом объектива, вход которого является входом тепловизора, четвертый вход МФП соединен с микрокриогенной системой, вход которой соединен с блоком управления микрокриогенной системы, причем блок цифровой обработки, состоящий из центрального процессора (ЦП), ОЗУ и ПЗУ, выполняет двухточечную коррекцию неравномерности чувствительности и осуществляет алгоритм устранения из изображения дефектных элементов. На выходе блока формируется стандартный телевизионный сигнал с частотой кадров 25 Гц. Описанное устройство, как наиболее близкое к предлагаемому, принято за прототип и представлено на фиг.1.

Данное устройство имеет следующие недостатки:

- не слишком высокая предельная температурная чувствительность;

- недостаточная контрастность изображения;

- недостаточное качество изображения.

Задачей изобретения является увеличение предельной температурной чувствительности, контрастности и качества изображения.

Увеличение предельной температурной чувствительности достигается за счет увеличения разрядности АЦП (14 разрядов).

Увеличение контрастности в области относительной интенсивности, близкой к нулю, достигается за счет некоторого сокращения квантов, выделенных для кодирования интенсивностей вне этой области.

Увеличение качества изображения достигается за счет увеличения матрицы и за счет более точных калибровок механизмов обнаружения и исправления дефектных точек.

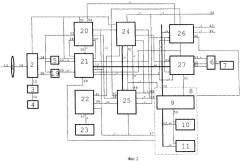

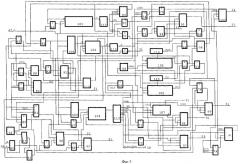

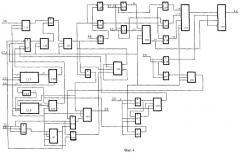

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.2-11, где

- на фиг.2 представлена структурная схема тепловизора;

- на фиг.3 представлена функциональная схема блока управления МФП;

- на фиг.4 представлена функциональная схема блока формирования данных;

- на фиг.5 представлена функциональная схема блока формирования цифровых сигналов;

- на фиг.6 представлена функциональная схема блока формирования телевизионных сигналов;

- на фиг.7 представлена функциональная схема блока прерываний;

- на фиг.8 представлена функциональная схема блока управления;

- на фиг.9 представлена функциональная схема блока управления с клавиатуры;

- на фиг.10 представлена функциональная схема формирователя одиночного импульса;

- на фиг.11 представлена функциональная схема узла устранения дребезга;

- на фиг.12 представлен алгоритм формирования управляющих импульсов на МФП 2 в блоке управления МФП 20;

- на фиг.13 представлено продолжение алгоритма формирования управляющих импульсов на МФП 2 в блоке управления МФП 20;

- на фиг.14 представлен график кусочно-линейного контрастирования с подстройкой параметров в реальном времени.

Указанные преимущества заявляемого устройства перед прототипом достигаются за счет того, что в тепловизор, содержащий объектив 1, матрицу фотоприемников (МФП) 2, микрокриогенную систему (МКС) 3, блок управления МКС 4, АЦП 5, ЦАП 6, телевизор 7, блок цифровой обработки 8, состоящий из центрального процессора 9, ОЗУ 10, ПЗУ 11, группа входов-выходов 12 которого соединена с группами входов-выходов ОЗУ 10 и центрального процессора 9, причем вход тепловизора является входом 13 объектива, выход 14 которого соединен с первым входом МФП 2, второй вход 15 которой соединен с выходом МКС 3, вход 16 которой соединен с блоком управления МКС 4, выход ЦАП 17 соединен с входом телевизора 7, причем первый выход 18 МФП соединен с первым входом первого АЦП 5, дополнительно введены второе АЦП 19, блок управления матрицей фотоприемников 20, блок формирования данных 21, блок управления с клавиатуры 22, клавиатура 23, блок прерываний 24, блок управления 25, блок формирования цифровых сигналов 26, блок формирования телевизионных сигналов 27, группа входов-выходов 12 которого соединена с группами входов-выходов блока цифровой обработки 8, блока управления 25, блока формирования цифровых сигналов 26, блока прерываний 24 и блока формирования данных 21, выход 28 которого соединен с первым входом центрального процессора 9, первая группа выходов 29 которого соединена с первыми группами входов блока управления 25 и блока прерываний 24, блока формирования цифровых сигналов 26, блока формирования телевизионных сигналов 27 и блока формирования данных 21, вторая группа 30 входов которого соединена с первой группой выходов блока управления МФП 20, вторая группа выходов 31 которого соединена с первой группой входов МФП 2, с первым входом блока прерываний 24 и с третьей группой входов блока формирования данных 21, четвертая группа входов 32 которого соединена с группой выходов первого АЦП 5, второй вход 33 которого соединен с первым входом второго АЦП 19 и первым выходом блока управления МФП 20, второй выход 34 которого соединен с первым входом блока формирования данных 21, пятая группа входов 35 которого соединена с группой выходов второго АЦП 19, второй вход 36 которого соединен со вторым выходом МФП 2, причем третий выход 37 блока управления МФП 20 соединен со вторым входом блока формирования данных 21, шестая группа входов 38 которого соединена с первой группой входов блока управления МФП 20 и с первой группой выходов блока управления 25, вторая группа входов 39 которого соединена с первой группой выходов блока управления с клавиатуры 22, выход 40 которого соединен со вторым входом блока прерываний 24, первая группа выходов 41 которого соединена с первой группой входов центрального процессора 9 и третьей группой входов блока управления 25, первый выход 42 которого соединен с первым входом блока формирования цифровых сигналов 26, первая 43 и вторая 44 группы выходов которого являются первой и второй группами выходов тепловизора соответственно, группа входов 45 которого соединена со второй группой входов блока прерываний 24 и четвертой группой входов блока управления 25, причем выход 46 блока формирования цифровых сигналов 26 соединен со вторым входом центрального процессора 9, вторая группа выходов 47 которого соединена с первой группой входов блока управления с клавиатуры 22, со вторыми группами входов блока формирования цифровых сигналов 26 и блока формирования телевизионных сигналов 27, с третьими группами входов блока прерываний 24, блока управления МФП 20, с пятой группой входов блока управления 25 и седьмой группой входов блока формирования данных 21, восьмая группа входов 48 которого соединена со вторым входом блока формирования цифровых сигналов 26 и первым входом блока формирования телевизионных сигналов 27, с четвертой группой входов блока прерываний 24 и второй группой выходов блока управления 25, шестая группа входов 49 которого соединена с пятой группой входов блока прерывания 24 и с третьей группой выходов центрального процессора 9, четвертая группа выходов 50 которого соединена с первыми группами входов ОЗУ 10 и ПЗУ 11. причем третий вход 51 центрального процессора 9 соединен с первым выходом блока формирования телевизионных сигналов 27, второй 52 и третий 53 выходы которого соединены с первым и вторым входами ЦАП 6 соответственно, группа входов которого соединена с группой выходов 54 блока формирования телевизионных сигналов 27, четвертый выход 55 которого соединен с третьим входом блока прерываний 24, причем третья группа выходов 56 блока управления МФП 20 соединена с третьей группой входов блока формирования цифровых сигналов 26, а первая группа выходов 57 клавиатуры 23 соединена со второй группой входов блока управления с клавиатуры 22.

Блок управления МФП 20 состоит из первой 58 константы, второй 59 константы, первой 60 схемы сравнения, второй 61 схемы сравнения, первого 62 элемента ИЛИ, второго 63 элемента ИЛИ, третьего 64 элемента ИЛИ, четвертого 65 элемента ИЛИ, пятого 66 элемента ИЛИ, шестого 67 элемента ИЛИ, седьмого 68 элемента ИЛИ, восьмого 69 элемента ИЛИ, девятого 70 элемента ИЛИ, десятого 71 элемента ИЛИ, одиннадцатого 72 элемента ИЛИ, двенадцатого 73 элемента ИЛИ, тринадцатого 74 элемента ИЛИ, четырнадцатого 75 элемента ИЛИ, пятнадцатого 76 элемента ИЛИ, шестнадцатого 77 элемента ИЛИ, семнадцатого 78 элемента ИЛИ, восемнадцатого 79 элемента ИЛИ, первого 80 элемента И, второго 81 элемента И, третьего 82 элемента И, четвертого 83 элемента И, пятого 84 элемента И, шестого 85 элемента И, седьмого 86 элемента И, сумматора 87, первого 88 триггера, второго 89 триггера, третьего 90 триггера, четвертого 91 триггера, пятого 92 триггера, шестого 93 триггера, седьмого 94 триггера, восьмого 95 триггера, девятого 96 триггера, десятого 97 триггера, одиннадцатого 98 триггера, двенадцатого 99 триггера, тринадцатого 100 триггера, четырнадцатого 101 триггера, первого 102 счетчика, второго 103 счетчика, третьего 104 счетчика, четвертого 105 счетчика, пятого 106 счетчика, шестого 107 счетчика, первого 108 мультиплексора констант, второго 109 мультиплексора констант, формирователя одиночного импульса 110, первого 111 дешифратора, второго 112 дешифратора, третьего 113 дешифратора, четвертого 114 дешифратора, пятого 115 дешифратора, элемента НЕ 116, выход которого является первым сигналом второй группы выходов 31 блока управления МФП 20, второй сигнал второй группы выходов 31 блока управлений МФП 20 соединен с выходом первого 88 триггера, первыми входами первого 62 элемента ИЛИ, четвертого 83 элемента И, первого 108 мультиплексора констант, с инверсным, информационным входом второго 103 счетчика и информационным входом формирователя одиночного импульса 110, третий сигнал второй группы выходов 31 блока управления МФП 20 соединен с выходом девятого 96 триггера, четвертый сигнал второй группы выходов 31 блока управления МФП 20 соединен с выходом шестого 107 счетчика, пятый, шестой и седьмой сигналы второй группы выходов 31 блока управления МФП 20 соединены с выходами третьего 90 триггера, пятого 92 триггера и двенадцатого 99 триггера, информационный вход которого соединен с первыми входами семнадцатого 78 элемента ИЛИ и третьего 64 элемента ИЛИ и является первым сигналом группы выходов второго 112 дешифратора, второй сигнал которой соединен с первым входом тринадцатого 74 элемента ИЛИ, третий сигнал группы выходов второго 112 дешифратора соединен с первыми входами второго 63 и восьмого 69 элементов ИЛИ, с информационными входами первого 88 триггера и шестого 107 счетчика, четвертый сигнал группы выходов второго 112 дешифратора соединен с первым входом пятнадцатого 76 элемента ИЛИ и информационным входом тринадцатого 100 триггера, пятый сигнал группы выходов второго 112 дешифратора соединен с первыми входами первого 80 и второго 81 элементов И, шестой сигнал группы выходов второго 112 дешифратора соединен с первым входом восемнадцатого 79 элемента ИЛИ, седьмой сигнал группы выходов второго 112 дешифратора соединен со вторым входом восемнадцатого 79 элемента ИЛИ и информационным входом четырнадцатого 101 триггера, восьмой сигнал группы выходов второго 112 дешифратора является первым сигналом первой группы выходов 30 блока управления МФП 20, второй сигнал которой соединен с выходом четырнадцатого 101 триггера, третий и четвертый сигналы первой группы выходов 30 блока управления МФП 20 соединены с первым и вторым выходами третьего 113 дешифратора, пятый сигнал первой группы выходов 30 блока управления МФП 20 соединен с выходом третьего 82 элемента И, со вторыми входами первого 108 мультиплексора констант, первого 62, третьего 64, восьмого 69, тринадцатого 74, семнадцатого 78 элементов ИЛИ, с первыми входами второго 109 мультиплексора констант и шестого 67 элемента ИЛИ и третьим входом восемнадцатого 79 элемента ИЛИ, выход которого соединен с разрешающим входом четырнадцатого 101 триггера, тактовый вход которого соединен с тактовыми входами первого 102, второго 103, третьего 104, четвертого 105, пятого 106, шестого 107 счетчиков, первого 88, второго 89, третьего 90, четвертого 91, пятого 92, шестого 93, седьмого 94, восьмого 95, девятого 96, десятого 97, одиннадцатого 98, двенадцатого 99, тринадцатого 100, четырнадцатого 101 триггеров, формирователя одиночного импульса 110 и является первым сигналом третьей группы входов 47 блока управления МФП 20, второй сигнал которой соединен со сбросовыми входами первого 88, третьего 90, пятого 92, девятого 96, двенадцатого 99, тринадцатого 100, четырнадцатого 101 триггеров, второго 103, пятого 106, шестого 107 счетчиков, с первыми входами пятого 66 и шестнадцатого 77 элементов ИЛИ, со вторыми входами второго 109 мультиплексора констант и шестого 67 элемента ИЛИ, с третьим входом первого 108 мультиплексора констант, причем выход первого 62 элемента ИЛИ соединен с разрешающим входом четвертого 91 триггера, инверсный выход которого соединен со вторым входом четвертого 83 элемента И, выход которого соединен с информационным входом четвертого 91 триггера, выход второго 63 элемента ИЛИ соединен с разрешающим входом второго 89 триггера, выход которого является первым сигналом третьей группы выходов 56, второй сигнал которой соединен с выходом десятого 97 триггера, информационный вход которого соединен с первым входом одиннадцатого 72 элемента ИЛИ и третьим выходом третьего 113 дешифратора, четвертый выход которого соединен со вторым входом одиннадцатого 72 элемента ИЛИ и сбросовым входом третьего 104 счетчика, группа выходов которого соединена с группой входов третьего 113 дешифратора, пятый выход которого соединен с первым входом двенадцатого 73 элемента ИЛИ, установочным входом шестого 107 счетчика и информационным входом девятого 96 триггера, разрешающий вход которого соединен с выходом двенадцатого 73 элемента ИЛИ, второй вход которого соединен с шестым выходом третьего 113 дешифратора, группа выходов блока констант 58 соединена с первой группой входов сумматора 87, группа выходов которого соединена с первой группой входов второй 61 схемы сравнения, выход которой соединен с инверсными входами первого 80 и второго 81 элементов И и первыми входами четвертого 65 и седьмого 68 элементов ИЛИ, выход седьмого 68 элемента ИЛИ соединен с разрешающим входом пятого 92 триггера, информационный вход которого соединен со вторым входом седьмого 68 элемента ИЛИ и выходом второго 81 элемента И, второй инверсный вход которого соединен со вторым входом первого 80 элемента И и выходом четвертого 91 триггера, первая группа входов 38 блока управления МФП 20 соединена со второй группой входов сумматора 87 и первой группой входов первой 60 схемы сравнения, выход которой соединен с третьим входом семнадцатого 78 элемента ИЛИ, выход которого соединен с разрешающим входом двенадцатого 99 триггера, первый выход 33 блока управления МФП 20 соединен с выходом седьмого 94 триггера, инверсный выход которого соединен с седьмым 86 элементом И, выход которого соединен с первым входом четырнадцатого 75 элемента ИЛИ, выход которого соединен с информационным входом седьмого 94 триггера, второй выход 34 блока управления МФП 20 соединен с выходом тринадцатого 100 триггера, разрешающий вход которого соединен с выходом пятнадцатого 76 элемента ИЛИ, второй вход которого соединен с выходом тринадцатого 74 элемента ИЛИ, третий выход 37 блока управления МФП 20 соединен с выходом восьмого 95 триггера, информационный вход которого соединен с первым входом десятого 71 элемента ИЛИ и выходом девятого 70 элемента ИЛИ, первый вход которого является первым сигналом группы выходов первого 111 дешифратора, второй сигнал которой соединен с инверсным сбросовым и информационным входами шестого 93 триггера, вторым входом пятого 66 элемента ИЛИ и инверсным разрешающим входом первого 102 счетчика, третий сигнал которой соединен со вторым входом десятого 71 элемента ИЛИ, выход которого соединен с разрешающим входом восьмого 95 триггера, причем группа выходов второго 103 счетчика соединена с группой входов второго 112 дешифратора и вторыми группами входов первой 60 и второй 61 схем сравнения, третий вход первого 80 элемента И соединен со вторым входом второго 81 элемента И, с первым входом третьего 82 элемента И, с разрешающим входом пятого 106 счетчика и выходом шестого 93 триггера, выход первого 80 элемента И соединен со вторым входом четвертого 65 элемента ИЛИ и информационным входом третьего 90 триггера, разрешающий вход которого соединен с выходом четвертого 65 элемента ИЛИ, второй вход третьего 82 элемента И соединен с выходом одиннадцатого 98 триггера, информационный вход которого соединен с выходом пятого 84 элемента И, первый вход которого соединен с выходом четвертого 114 дешифратора, группа входов которого соединена с группой выходов четвертого 105 счетчика, выход которого соединен с первым входом шестого 85 элемента И, выход которого соединен со вторым входом шестнадцатого 77 элемента ИЛИ и инверсным разрешающим входом четвертого 105 счетчика, сбросовый вход которого соединен с выходом второй 59 константы, вход которой соединен с выходом шестнадцатого 77 элемента ИЛИ, выход пятого 66 элемента ИЛИ соединен со сбросовым входом первого 102 счетчика, группа выходов которого соединена с группой входов первого 111 дешифратора, группа выходов первого 108 мультиплексора констант соединена с группой установочных входов второго 103 счетчика, выход которого соединен с входом элемента НЕ 116, выход формирователя одиночного импульса 110 соединен со вторыми входами девятого 70 и четырнадцатого 75 элементов ИЛИ и инверсным входом седьмого 86 элемента И, группа выходов второго 109 мультиплексора констант соединена с группой установочных входов третьего 104 счетчика, инверсный разрешающий вход которого соединен с выходом шестого 67 элемента ИЛИ, выход восьмого 69 элемента ИЛИ соединен с разрешающим входом шестого 107 счетчика, выход пятого 106 счетчика соединен со вторым входом шестого 85 элемента И, выход одиннадцатого 72 элемента ИЛИ соединен с разрешающим входом десятого 97 триггера, выход пятого 115 дешифратора соединен со вторым входом пятого 84 элемента И.

Блок формирования данных 21 состоит из сдвигового регистра 117 счетчика 118, первого 119, второго 120, третьего 121, четвертого 122, пятого 123, шестого 124, седьмого 125 триггеров, первого 126 элемента И, второго 127 элемента И, третьего 128 элемента И, четвертого 129 элемента И, пятого 130 элемента И, шестого 131 элемента И, седьмого 132 элемента И, восьмого 133 элемента И, девятого 134 элемента И, первой 135 группы элементов И, второй 136 группы элементов И, третьей 137 группы элементов И, четвертой 138 группы элементов И, пятой 139 группы элементов И, константы 140, первого 141 формирователя одиночного импульса, второго 142 формирователя одиночного импульса, первого 143 элемента ИЛИ, второго 144 элемента ИЛИ, третьего 145 элемента ИЛИ, четвертого 146 элемента ИЛИ, пятого 147 элемента ИЛИ, первого 148 мультиплексора, второго 149 мультиплексора, первого 150 регистра, второго 151 регистра, группа выходов которого соединена с первой группой входов второго 149 мультиплексора, вторая группа входов которого соединена с группой входов пятой 139 группы элементов И и с группой выходов первого 150 регистра, первая группа входов которого соединена с группой выходов первой 135 группы элементов И, группа входов которых соединена с группой входов третьей 137 группы элементов И и является четвертой 32 группой входов блока формирования данных 21, группа выходов 12 которого соединена с группой выходов второго 149 мультиплексора, вход которого соединен с инверсным входом второго 149 мультиплексора и выходом девятого 134 элемента И, первый и второй инверсные входы которого соединены с первым и вторым входами пятого 147 элемента ИЛИ соответственно и являются первым и вторым сигналами первой 29 группы входов блока формирования данных 21, выход которого соединен с выходом пятого 123 триггера, информационный вход которого соединен с разрешающим входом пятого 123 триггера, с разрешающим входом счетчика 118 и с выходом четвертого 129 элемента И, первый вход которого соединен с разрешающим входом шестого 124 триггера, первым входом седьмого 132 элемента И и выходом четвертого 122 триггера, информационный вход которого соединен с выходом третьего 128 элемента И, первый вход которого соединен с выходом первого 119 триггера, информационный вход которого является первым 34 входом блока формирования данных 21, первый, второй, третий, четвертый, пятый сигналы второй 30 группы входов которого соединены соответственно с первым входом восьмого 133 элемента И, с первым входом четвертого 146 элемента ИЛИ. с первым входом третьего 145 элемента ИЛИ, со вторым входом восьмого 133 элемента И, со вторым входом третьего 145 элемента ИЛИ, выход которого соединен с разрешающим входом седьмого 125 триггера, выход которого соединен с первым входом второго 127 элемента И, выход которого соединен с информационным входом первого 141 формирователя одиночного импульса, выход которого соединен со вторым входом третьего 128 элемента И, второй сигнал третьей 31 группы входов блока формирования данных 21 соединен с первым входом первого 126 элемента И, третий сигнал третьей 31 группы входов блока формирования данных 21 соединен со вторым входом первого 126 элемента И и с первыми входами первого 143 элемента ИЛИ и второго 144 элемента ИЛИ, выход которого соединен со сбросовым входом шестого 124 триггера, выход которого соединен со вторым входом четвертого 129 элемента И, инверсным входом пятого 130 элемента И и первым входом шестого 131 элемента И, выход которого соединен с первыми входами третьей 137 группы элементов И, четвертой 138 группы элементов И и пятой 139 группы элементов И, группы выходов которых соединены с первой, второй и третьей группами входов второго 151 регистра, пятая 35 группа входов блока формирования данных 21 соединена с группой входов второй 136 группы элементов И и с группой входов четвертой 138 группы элементов И, тактовый вход второго 151 регистра является первым сигналом седьмой 47 группы входов и соединен с тактовыми входами первого 150 регистра, первого 141 и второго 142 формирователей одиночного импульса, сдвигового регистра 117, счетчика 118, первого 119, второго 120, третьего 121, четвертого 122, пятого 123, шестого 124, седьмого 125 триггеров, сбросовый вход которого является вторым сигналом седьмой 47 группы входов и соединен со сбросовыми сигналами первого 119, третьего 121, четвертого 122, седьмого 125 триггеров, сдвигового регистра 117, первого 150 регистра, второго 151 регистра, первого 141 и второго 142 формирователей одиночного импульса, со вторыми входами второго 144, четвертого 146 элементов ИЛИ и первого 143 элемента ИЛИ, выход которого соединен со сбросовым входом пятого 123 триггера, причем шестая 38 группа входов блока формирования данных 21 соединена с первой группой входов первого 148 мультиплексора, выход которого соединен с первым инверсным входом второго 127 элемента И, второй инверсный вход которого соединен с третьим входом первого 143 элемента ИЛИ и выходом третьего 121 триггера, информационный и разрешающий входы которого соединены с выходом первого 126 элемента И, инверсный вход которого является первым сигналом восьмой 48 группы входов, второй сигнал которой соединен с инверсным входом седьмого 132 элемента И, выход которого соединен со вторым входом шестого 131 элемента И и первым входом пятого 130 элемента И, выход которого соединен с входами первой группы 135 элементов И и второй группы 136 элементов И, группа выходов которой соединена с информационной группой входов первого 150 регистра, причем группа выходов константы 140 соединена с установочной группой входов счетчика 118, выход которого соединен с информационным, инверсным входом второго 120 триггера, выход которого соединен со вторым входом второго 127 элемента И, причем вход константы соединен с установочным входом второго 120 триггера и выходом четвертого 146 элемента ИЛИ, второй вход 37 блока формирования данных 21 соединен с информационным, инверсным входом сдвигового регистра 117, группа выходов которого соединена со второй группой входов первого 148 мультиплексора, инверсный выход пятого 147 элемента ИЛИ соединен с информационным входом второго 142 формирователя одиночного импульса, выход которого соединен с четвертым входом первого 143 элемента ИЛИ, инверсный выход шестого 124 триггера соединен с его информационным входом, выход восьмого 133 элемента И соединен с третьим входом третьего 145 элемента ИЛИ и информационным входом седьмого 125 триггера.

Блок формирования цифровых сигналов состоит из первого 152 формирователя одиночного импульса, второго 153 формирователя одиночного импульса, третьего 154 формирователя одиночного импульса, сдвигового регистра 155, первого 156 счетчика, второго 157 счетчика, первого 158 регистра, второго 159 регистра, третьего 160 регистра, первого 161 триггера, второго 162 триггера, третьего 163 триггера, четвертого 164 триггера, пятого 165 триггера, шестого 166 триггера, седьмого 167 триггера, константы 168, первого 169 элемента ИЛИ, второго 170 элемента ИЛИ, третьего 171 элемента ИЛИ, четвертого 172 элемента ИЛИ, пятого 173 элемента ИЛИ, первого 174 элемента И, второго 175 элемента И, третьего 176 элемента И, четвертого 177 элемента И, пятого 178 элемента И, шестого 179 элемента И, первой группы 180 элементов И, второй группы 181 элементов И, первого 182 мультиплексора, второго 183 мультиплексора, дешифратора 184 и элемента НЕ 185, выход 46 которого соединен с выходом блока формирования цифровых сигналов 26, второй и третий сигналы первой группы входов 29 которого соединены с первым и вторым инверсными входами первого элемента И 174, выход которого соединен с информационным входом первого 152 формирователя одиночного импульса, выход которого соединен с первыми входами третьего 176 и четвертого 177 элементов И, четвертого 172 элемента ИЛИ и разрешающим входом первого 161 триггера, выход которого соединен с инверсным входом третьего 176 элемента И и вторым входом четвертого 177 элемента И, выход которого соединен с группой входов второй группы 181 элементов И, группа выходов которых соединена с информационной группой входов второго 159 регистра, группа выходов которого соединена с первой группой входов первого 182 мультиплексора, группа выходов которого соединена с первой группой входов второго 183 мультиплексора, группа выходов которого соединена с информационной группой входов третьего 160 регистра, группа выходов которого является второй группой выходов 44 блока формирования цифровых сигналов 26, первая группа 43 выходов которого соединена с выходами пятого 165 и шестого 166 триггеров, установочные входы которых соединены со сбросовыми входами первого 158, второго 159 и третьего 160 регистров, установочным входом второго 162 триггера, первыми входами первого 169, второго 170 и пятого 173 элементов ИЛИ, вторым входом четвертого 172 элемента ИЛИ, сбросовым входом сдвигового регистра 155 и является вторым сигналом второй 47 группы входов блока формирования цифровых сигналов 26, первый сигнал которой соединен с тактовыми входами первого 152, второго 153 и третьего 154 формирователей одиночного импульса, первого 161, второго 162, третьего 163, четвертого 164, пятого 165 и шестого 166 триггеров, первого 156 счетчика, третьего 160, второго 159 и первого 158 регистров, группа выходов которого соединена со второй группой входов первого 182 мультиплексора, прямой и инверсный входы которого соединены с выходом четвертого 164 триггера, инверсный выход которого соединен с информационным входом четвертого 164 триггера, разрешающий вход которого соединен с первым выходом второго 157 счетчика, второй выход которого соединен с первым входом шестого 179 элемента И, выход которого соединен с информационным входом третьего 154 формирователя одиночного импульса, выход которого соединен с первым входом третьего 171 элемента ИЛИ и разрешающим входом первого 156 счетчика, выход которого соединен с прямым и инверсным входами седьмого 167 триггера, выход которого соединен со вторым входом шестого 179 элемента И, третий вход которого соединен с выходом пятого 178 элемента И и разрешающим входом второго 157 счетчика, группа выходов которого соединена с группой входов дешифратора 184, группа выходов которого соединена с группой входов второго 183 мультиплексора, причем первый сигнал третьей 56 группы входов блока формирования цифровых сигналов 26 соединен с инверсным входом пятого 173 элемента ИЛИ и инверсным, информационным входом сдвигового регистра 155, информационным входом шестого 166 триггера и первым входом пятого 178 элемента И, второй сигнал третьей 56 группы входов блока формирования цифровых сигналов 26 соединен со вторыми входами пятого 178 элемента И и первого 169 элемента ИЛИ, инверсным, разрешающим входом второго 162 триггера, первым входом второго 175 элемента И, инверсным входом второго 170 элемента ИЛИ и информационным входом пятого 165 триггера, группа входов-выходов 12 блока формирования цифровых сигналов 26 соединена с группами входов второй группы 184 элементов И и первой группы 180 элементов И, группа выходов которой соединена с информационной группой входов первого 158 регистра, первый 42 вход блока формирования цифровых сигналов 26 соединен с тактовыми входами сдвигового регистра 155 и второго 157 счетчика, сбросовый вход которого соединен с выходом пятого 173 элемента ИЛИ, со сбросовым входами четвертого 164 триггера и третьего 154 формирователя одиночного импульса и входом константы 168, группа выходов которой соединена с группой установочных входов первого 156 счетчика, второй 48 вход блока формирования цифровых сигналов 26 соединен с инверсным информационным входом второго 162 триггера, выход которого соединен с третьим входом четвертого 172 элемента ИЛИ, выход которого соединен со сбросовым входом третьего 163 триггера, выход которого соединен со входом элемента НЕ 185, причем выход первого 169 элемента ИЛИ соединен со сбросовым входом первого 161 триггера, инверсный выход которого соединен с его информационным входом, выход второго 175 элемента И соединен с информационным входом второго 153 формирователя одиночного импульса, выход которого соединен со вторым входом третьего 171 элемента ИЛИ, выход которого соединен с информационным и разрешающим входами третьего 163 триггера, второй вход второго 175 элемента И соединен с выходом сдвигового регистра 155, выход второго 170 элемента ИЛИ соединен со сбросовыми входами первого 152 и второго 153 формирователей одиночного импульса, выход третьего 176 элемента И соединен с группой входов первой группы 180 элементов И.

Блок формирования телевизионных сигналов 27 состоит из первого 186 формирователя одиночного импульса, второго 187 формирователя одиночного импульса, первого 188 счетчика, второго 189 счетчика, третьего 190 счетчика, четвертого 191 счетчика, пятого 192 счетчика, шестого 193 счетчика, седьмого 194 счетчика, восьмого 195 счетчика, первого 196 регистра, второго 197 регистра, кодера 198, константы 199, первого 200 триггера, второго 201 триггера, третьего 202 триггера, четвертого 203 триггера, пятого 204 триггера, шестого 205 триггера, седьмого 206 триггера, восьмого 207 триггера, девятого 208 триггера, десятого 209 триггера, одиннадцатого 210 триггера, двенадцатого 211 триггера, тринадцатого 212 триггера, четырнадцатого 213 триггера, мультиплексора 214, первого 215 дешифратора, второго 216 дешифратора, третьего 217 дешифратора, четвертого 218 дешифратора. пятого 219 дешифратора, шестого 220 дешифратора, первого 221 элемента И, второго 222 элемента И. третьего 223 элемента И, четвертого 224 элемента И, пятого 225 элемента И, шестого 226 элемента И, седьмого 227 элемента И, восьмого 228 элемента И, девятого 229 элемента И, десятого 230 элемента И, одиннадцатого 231 элемента И, двенадцатого 232 элемента И, тринадцатого 233 элемента И, четырнадцатого 234 элемента И, пятнадцатого 235 элемента И, шестнадцатого 236 элемента И, семнадцатого 237 элемента И, первой группы 238 элементов И, второй группы 239 элементов И, первого 240 элемента ИЛИ, второго 241 элемента ИЛИ, третьего 242 элемента ИЛИ, четвертого 243 элемента ИЛИ, пятого 244 элемента ИЛИ, шестого 245 элемента ИЛИ, седьмого 246 элемента ИЛИ, восьмого 247 элемента ИЛИ, девятого 248 элемента ИЛИ, десятого 249 элемента ИЛИ, одиннадцатого 250 элемента ИЛИ, двенадцатого 251 элемента ИЛИ, тринадцатого 252 элемента ИЛИ, четырнадцатого 253 элемента ИЛИ, пятнадцатого 254 элемента ИЛИ, шестнадцатого 255 элемента ИЛИ, семнадцатого 256 элемента ИЛИ, восемнадцатого 257 элемента ИЛИ, девятнадцатого 258 элемента ИЛИ, двадцатого 259 элемента ИЛИ, двадцать первого 260 элемента ИЛИ, двадцать второго 261 элемента ИЛИ, двадцать третьего 262 элемента ИЛИ, двадцать четвертого 263 элемента ИЛИ, двадцать пятого 264 элемента ИЛИ, двадцать шестого 265 элемента ИЛИ, двадцать седьмого 266 элемента ИЛИ, двадцать восьмого 267 элемента ИЛИ, двадцать девятого 268 элемента ИЛИ, тридцатого 269 элемента ИЛИ, тридцать первого 270 элемента ИЛИ, выход тридцать первого 270 элемента ИЛИ соединен с разрешающим входом четырнадцатого 213 триггера и входом тридцатого 269 элемента ИЛИ, выход которого соединен со сбросовым входом тринадцатого 212 триггера, выход которого соединен с первыми входами шестого 226, восьмого 228, десятого 230 и тринадцатого 233 элементов И, выход тринадцатого 233 элемента И соединен с разрешающим входом шестого 205 триггера, выход которого соединен с прямым и инверсным входами мультиплексора 214, группа выходов которого является первой 54 группой выходов блока формирования телевизионных сигналов 27, первый 51 выход которого соединен с инверсным выходом двенадцатого 211 триггера, информационный и разрешающий входы которого соединены с выходом второго 187 формирователя одиночного импульса и разрешающим входом седьмого 194 счетчика, выход которого соединен с инверсным информационным входом седьмого 206 триггера и первым входом двадцать первого 260 элемента ИЛИ, выход которого соединен со сбросовым входом седьмого 206 триггера, выход которого соединен с первым входом девятого 229 элемента И, выход которого соединен с информационным входом второго 187 формирователя одиночного импульса, сбросовый вход которого соединен со сбросовыми входами шестого 193 счетчика и шестого 205 триггер