Система стереотелевидения

Иллюстрации

Показать всеИзобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания. Техническим результатом является снижение энергоемкости системы в два раза по отношению к прототипу и введение учета времени просмотра телевизионных каналов. Результат достигается тем, что в системе стереотелевидения на передающей стороне вводятся две матрицы ПЗИ /приборы с зарядовой инжекцией/, передатчик выполняется одноканальным, на приемной стороне вводятся два приемных регистра, пульт дистанционного управления и блок учета времени приема телевизионных каналов. 19 ил., 2 табл.

Реферат

Изобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания.

Прототипом принята "Система стереотелевидения" [1], содержащая передающую и приемную стороны. Передающая сторона включает фотоэлектрический преобразователь /ФЭП/ на основе трех пьезодефлекторов, содержащий правый и левый объективы, с первого по шестой предварительные усилители и блоки строчной и кадровой разверток, включает с первого по пятый ключи, два триггера, с первого по шестой АЦП видеосигналов, с первого по шестой кодеры, два АЦП сигнала звука, задающий генератор и синтезатор частот, два формирователя кодов, два самоходных распределителя импульсов /СРИ/ и двухканальный передатчик радиосигналов. Приемная сторона включает антенну, блок управления /выбор каналов/, два тракта приема и обработки кодов видеосигналов, плоскопанельный светодиодный экран /СД-экран/, канал формирования управляющих сигналов, два канала воспроизведения звука, ИК-передатчик на корпусе СД-экрана и 3Д-очки с ИК-приемником на оправе. Первый тракт включает последовательно соединенные блок приема радиосигналов, усилитель радиочастоты и двухполярный амплитудный детектор, два формирователя импульсов, канал сигнала R и канал сигнала G, второй тракт включает блок приема радиосигналов, усилитель радиочастоты и двухполярный амплитудный детектор, два формирователя импульсов и канал сигнала В. Каждый из каналов сигналов R, G, В включает последовательно соединенные декодер, блок обработки /удвоения/ кодов, первый блок задержек и сумматор, второй блок задержек, два накопителя кодов кадра и два блока формирования управляющих сигналов. Канал формирования управляющих сигналов содержит блок выделения строчных синхроимпульсов /ССИ/, синтезатор частот, ключ, счетчик импульсов, дешифратор и блок выделения синхроимпульсов стереопар /СИС/. На передающей стороне видеорежим 960отсч×540 строк×50 Гц, на приемной стороне видеорежим 1920×1080×50 Гц. Изображение зрителем воспринимается объемным через 3Д-очки с ИК-приемником, стекла очков синхронно с правым и левым кадрами стереопары поочередно теряют прозрачность на 20 мс, каждый глаз видит свой кадр, что и дает стереоэффект. Стекла ЗД-очков выполнены по технологии ИК-ячеек просветного типа и используются как электронно-управляемые светофильтры /затворы/ [2, с.558-565]. Частота стереопар 25 Гц. Недостатки прототипа: высокая энергоемкость системы из-за передачи-приема по двум радиоканалам, отсутствие на приемной стороне поканального учета работы приемной стороны.

Цель изобретения - снижение энергоемкости системы и введение на приемной стороне поканального учета времени просмотра передач. Техническим результатом является снижение энергоемкости системы в два раза выполнением приема-передачи информации по одному каналу и увеличение функций приемной стороны введением в ней учета времени просмотра телевизионных каналов.

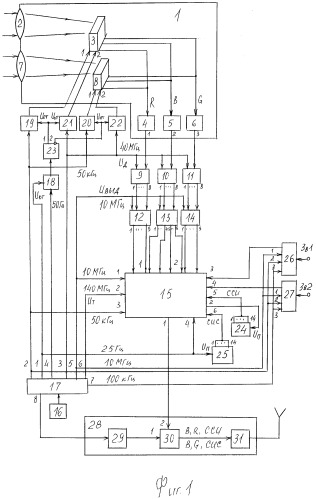

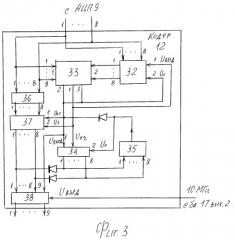

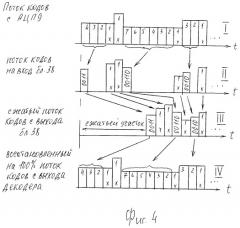

Сущность изобретения в том, что в системе стереотелевидения на передающей стороне передатчик выполняется одноканальным и в ФЭП вводятся две матрицы ПЗИ /приборы с зарядовой инжекцией/, на приемной стороне вводятся два приемных регистра и блок учета времени приема телевизионных каналов. Передающая сторона на фиг.1, структура цифрового потока на фиг.2, кодер на фиг.3, диаграмма работы кодера на фиг.4, формирователь кодов на фиг.5, приемная сторона на. фиг.6, спектр адалитудно-модулированного сигнала на фиг.7, двухполярный амплитудный детектор на фиг.8, декодер на фиг.9, накопитель кодов кадра на фиг.10, блок регистров на фиг.11, 12, блок формирования управляющих сигналов на фиг.13, блок выделения ССИ /СИС/ на фиг.17, СД-ячейка на фиг.14, элемент матрицы на фиг.15, расположение элементов в матрице СД-экрана на фиг.16, временные диаграммы работы системы на фиг.18, блок учета времени приема телевизионных каналов на фиг.19.

На передающей стороне с выходов АЦП видеосигналов /9, 10, 11/ идет видеорежим 800отсч×1000строк×50 Гц, где 800 - число кодируемых отсчетов в строке, 1000 - число кодируемых строк в кадре, 50 Гц - частота кадров /25 правых плюс 25 левых/. Частота стереопар 25 Гц. Коды правого и левого кадров стереопары передаются последовательно друг за другом. Частота дискретизации в АЦП видеосигналов составляет: fд=800×1000×50=40 МГц. Отсюда частота строк 50 кГц /50 Гц×1000/. При частоте дискретизации 40 МГц в каждом кадре много кодов, равных по величине, следовательно, поток кодов кадра подлежит сжатию без утраты качества изображения. Сжатие потока кодов выполняется раздельно по цветовым сигналам R, В, G. Коэффициент сжатия кодов в каждом потоке кодов цветового сигнала принимается не менее 4, поэтому частота дискретизации на выходе кодеров составляет 10 МГц . Период следования кодов в потоке 100 нс , период следования разрядов в коде 7,1 нс . С первого по девятый разряды кода R и 1-4 разряды кода В идут последовательно в одной посылке и представляют собой суммарный код /фиг.2/. 1-9 разряды кода G и 5-9 разряды кода В идут последовательно в посылке и составляют второй суммарный код, число разрядов в суммарном коде 14. Тактовая частота для формирования суммарных кодов составляет: ƒт=10 МГц×14разр=140 МГц. Несущая частота в передающей стороне принимается: ƒн=140 МГц×15=2100 МГц.

Верхняя боковая частота несущей составляет: 2240 МГц /2100+140/, нижняя боковая частота несущей: 1960 МГц /2100-140/.

Передающая сторона включает /фиг.1/ фотоэлектрический преобразователь 1 /ФЭП/, являющийся датчиком цветовых видеосигналов двух изображений: правого и левого кадров стереопары, и содержит первый объектив 2 /правый/, в фокальной плоскости которого расположена фоточувствительная сторона первой матрицы ПЗИ 3 - прибора с зарядовой инжекцией по технологии Foveon Х3 из трехслойного КМОП-датчика [2, с.832, 3, с.552] с соответствующим оптическим разрешением /1600×1000/ и обеспечивающего 24-битную глубину цвета [2, с.835]. Первый-третий выходы матрицы ПЗИ 3 подключены к входам соответственно предварительных усилителей 4, 5, 6. ФЭП включает второй 7 объектив /левый/, расположенный на соответствующем расстоянии от объектива 2. В фокальной плоскости объектива 7 расположена фоточувствительная сторона второй матрицы ПЗИ 8, первый-третий выходы которой подключены тоже к входам соответственно предварительных усилителей 4, 5, 6. Передающая сторона включает первый 9, второй 10, третий 11 АЦП видеосигналов сигналов R, B, G, первый 12, второй 13, третий 14 кодеры, формирователь 15 кодов, генератор 16 синусоидальных колебаний и синтезатор 17 частот, первый 18, второй 19, третий 20, четвертый 21 и пятый 22 ключи, триггер 23, первый самоходный распределитель 24 импульсов /СРИ/, формирующий 14-разрядный код строчных синхроимпульсов /ССИ/, второй СРИ 25, формирующий 14-разрядный код синхроимпульсов стереопар /СИС/, первый АЦП 26 сигнала звука 3в1 и второй АЦП 27 сигнала звука 3в2, передатчик 28 радиосигналов, включающий последовательно соединенные усилитель 29 несущей частоты, амплитудный модулятор 30 и выходной усилитель 31. Амплитудный модулятор 30 содержит последовательно соединенные кольцевой модулятор и полосовой фильтр [4, с.234]. АЦП видеосигналов 9, 10, 11 выполнены идентично прототипу [1, с.5, фиг.5], АЦП 26, 27 сигнала звука выполнены идентично [5, с.30, фиг.7] и преобразуют сигналы звука в 14-разрядные коды с дискретизацией 100 кГц. Кодеры 12, 13, 14 идентичны, каждый включает /фиг.3/ последовательно соединенные регистр 32, схему сравнения 33 /компаратор/, счетчик 34 импульсов и дешифратор 35, последовательно соединенные блок 36 элементов задержек, блок 37 ключей и буферный накопитель 38 кодов кадра. Информационными входами являются поразрядно объединенные 1-8 входы регистра 32, первые входы схемы 33 сравнения и входы блока 36 элементов задержек. Выходами являются 1-9 выходы буферного накопителя 38 кодов кадра с объемом 200×103 9-разрядных кодов. Управляющим входом является управляющий вход /10 МГц/ блока 38.

Формирователь 15 кодов включает /фиг.5/ три канала. Первый и второй каналы идентичны, выходы их объединены. Первый канал включает последовательно соединенные первый блок 39 элементов И, которых 13 штук, первые входы которых являются первым информационным входом и принимают 1-9 разряды кодов R с кодера 12 и 1-4 разряды кодов В с кодера 13, первый 40 и второй 41 элементы ИЛИ и первый выходной ключ 42, первый СРИ 43. Второй канал включает второй блок 44 элементов И, которых 14 штук, первые входы их являются вторым информационным входом блока 15 и принимают 1-9 разряды кодов G и 5-9 разряды кодов В с кодера 13, третий 45 и четвертый 46 элементы ИЛИ и второй выходной ключ 47, второй СРИ 48. Третий канал включает третий блок 49 элементов И, которых 14 штук, первые входы которых являются третьим информационным входом блока 15 и принимают 14-разрядные коды звукового сигнала с АЦП 26, пятый элемент ИЛИ 50, выход его подключен к второму входу второго элемента ИЛИ 41, и третий СРИ 51, включает четвертый блок 52 элементов И, которых 14 штук, первые входы которых являются четвертым информационным входом блока 15 и принимают коды звука с АЦП 27, шестой элемент ИЛИ 53, выход которого подключен к второму входу четвертого элемента ИЛИ 46, и четвертый СРИ 54. Блок 15 также включает первый 55, второй 56, третий 57 ключи и последовательно соединенные счетчик 58 импульсов и дешифратор 59. СРИ все 14-разрядные. Пятым информационным входом является сигнальный вход ключа 57, шестым - третий вход четвертого элемента ИЛИ 46. Выходами блока 15 являются: первым - объединенные выходы выходных ключей 42, 47, вторым - третий выход дешифратора 59. Управляющими входами являются: первым - объединенные сигнальные входы ключей 55, 56 и счетный вход счетчика 58 импульсов, вторым - сигнальные входы /140 МГц/ выходных ключей 42, 47, третьим - управляющий вход /50 кГц/ счетчика 58 импульсов, четвертым - управляющий вход /25 Гц/ третьего ключа 57. Первый выход дешифратора 59 подключен к первому управляющему входу ключа 55, второй выход - к второму управляющему входу ключа 55 и к первому управляющему входу ключа 56, третий выход - к второму управляющему входу второго ключа 56 и является вторым выходом блока 15. Вторые входы блоков 39, 44, 49, 52 подключены к выходам СРИ соответственно 43, 48, 51, 54. Выход ключа 55 подключен к входам СРИ 43, 48, выход ключа 56 подключен к входам СРИ 51, 54.

Приемная сторона включает /фиг.6/ антенну, блок 60 управления /выбор каналов/, один тракт приема и обработки кодов видеосигналов, плоскопанельный светодиодный экран /СД-экран/, канал формирования управляющих сигналов, два канала воспроизведения звука, ИК-передатчик на корпусе СД-экрана, ИК-приемник на оправе 3Д-очков и блок учета времени приема телевизионных каналов. Тракт приема и обработки кодов видеосигналов производит прием кодов правого и левого кадров стереопар и включает последовательно соединенные блок 61 приема радиосигналов, усилитель 62 радиочастоты и двухполярный амплитудный детектор 63, первый 64 и второй 65 формирователи импульсов, первый 66 и второй 67 приемные регистры, каждый из которых включает по 14 разрядов, и три идентичных канала сигналов R, B, G. Канал сигнала R включает последовательно соединенные регистр 68 сигнала R, декодер 69, блок 70 обработки кодов, накопитель 71 кодов кадра и блок 72 формирования управляющих сигналов. Канал сигнала В включает последовательно соединенные регистр 73 сигнала В, декодер 74, блок 75 обработки /удвоения/ кодов, накопитель 76 кодов кадра и блок 77 формирования управляющих сигналов. Канал сигнала G включает регистр 78 сигнала G, декодер 79, блок 80 обработки /удвоения/ кодов, накопитель 81 кодов кадра и блок 82 формирования управляющих сигналов. Выходы блоков 72, 77, 82 подключены к соответствующим входам СД-экрана 83, на корпусе которого расположен ИК-передатчик 84. Приемная сторона включает 3Д-очки 85 с ИК-приемником 86 на оправе очков и соединительный кабель с переключателем 87. При воспроизведении на экране правого кадра теряет прозрачность левое стекло очков, при воспроизведении левого кадра теряет на 20 мс прозрачность правое стекло 3Д-очков. В этой системе применяется и второй вариант: вход ИК-приемника 86 через кабель и переключатель 87, подключая к выходу триггера 95, получаем процесс управления 3Д-очками без участия ИК-передатчика 84. Порядок работы приемной стороны определяется каналом формирования управляющих сигналов, включающим блок 88 выделения строчных синхроимпульсов /ССИ/, синтезатор 89 частот, первый ключ 90, счетчик 91 импульсов, дешифратор 92, блок 93 выделения синхроимпульсов стереопар /СИС/, второй ключ 94 и триггер 95. Приемная сторона включает первый 96, второй 97 каналы воспроизведения звука, каждый из которых содержит регистр, ЦАП с фильтром низкой частоты, усилитель мощности и громкоговоритель. В состав приемной стороны введены пульт 98 дистанционного управления и блок 99 учета времени приема телевизионных каналов /блок учета ВПТК/. СД-экран 83 представляется числом излучающих элементов соответственно разрешению кадра /1600×1000/, выполненных в экранном материале /стекле/. Каждый излучающий элемент матрицы содержит три светодиодных ячейки /СД-ячейки/, каждая из которых излучает один из основных цветов R, B, G. СД-ячейка /фиг.14/ содержит светодиод белого свечения 124 и соответствующий цветной светофильтр 125 на излучающей стороне светодиода. Излучающий элемент матрицы на фиг.15, расположение излучающих элементов в матрице СД-экрана на фиг.16. Уровень яркости излучения СД-ячейки зрением воспринимается прямо пропорционально числу выполняемых импульсов излучений светодиодом за период кадра 20 мс. Каждый импульс излучения длительностью 78 мкс, их может быть от одного /78 мкс/ при коде сигнала 00000001 до 255 /20 мс/ при коде 11111111. Суммарное излучение трех цветов от излучающего элемента формирует и яркость и цветовой тон одного пиксела на экране 83. В качестве светодиодов могут применяться светодиоды с полимерными органическими молекулами - светодиоды технологии СДТ или PLEД [6, с.43], или сверхяркие светодиоды белого свечения фирм «Nichia», "Ledtronics" [7, c.47]. Светодиоды как технологии СДТ, так и сверхяркие выполняются непосредственно в экранном материале методом микроэлектронной технологии. Размеры сверхярких светодиодов диаметром 0,5 мм, размер излучающего элемента 1×1 мм /фиг.16/, размер СД-экрана: по горизонтали 1600×1 мм=1600 мм,

по вертикали 1000×1 мм=1000 мм,

по диагонали 188 см или 74″. Светодиоды технологии СДТ пригодны для получения экранов и малых и больших размеров.

Декодеры 69, 74, 79 идентичны, каждый включает /фиг.9/ последовательно соединенные первый 9-разрядный регистр 100, накопитель 101 кодов кадра емкостью 200×103 9-разрядных кодов /200отсч×1000с/, второй 9-разрядный регистр 102, первый блок 103 ключей из восьми ключей и третий 8-разрядный регистр 104, последовательно соединенные второй блок 105 ключей из восьми ключей, 8-разрядный вычитающий счетчик 106 импульсов и дешифратор 107, первый 108, второй 109, третий 110, четвертый 111 ключи. Информационным входом декодера являются 1-9 входы первого регистра 100, выходом являются 1-8 выходы третьего регистра 104. Управляющими входами являются: первым - объединенные управляющий вход регистра 100 и сигнальный вход /10 МГц/ третьего ключа 110, вторым - объединенные сигнальные входы /40 МГц/ ключей 108, 109, 111. Выход девятого разряда регистра 102 подключен параллельно к первому управляющему входу второго ключа 109, к вторым управляющим входам ключей 110, 111, 108, к второму управляющему входу блока 103 и к первому управляющему входу второго блока 105 ключей. Выход ключа 108 подключен к первому управляющему входу регистра 104, второй управляющий вход которого подключен к выходу второго ключа 109, к которому подключен и счетный вход вычитающего счетчика 106 импульсов. Выход дешифратора 107 подключен параллельно к первому управляющему входу первого блока 104 ключей, к второму управляющему входу блока 105 ключей, к первым управляющим входам ключей 108, 110, 111 и к второму управляющему входу ключа 109. Выход третьего ключа 110 подключен к управляющему входу накопителя 101 кодов кадра, выход ключа 111 подключен к управляющему входу второго регистра 102. Блоки 70, 75, 80 обработки /удвоения/ кодов идентичны этим же блокам в прототипе и приняты без изменений [1, с.7, фиг.14]. Накопители 71, 76, 81 кодов кадра идентичны, каждый включает /фиг.10/ блоки 112 регистров по числу строк в кадре /1000/. Информационным входом являются поразрядно объединенные 1-8 входы блоков 1121-1000 регистров. Управляющими входами являются: первым - первый управляющий вход /50 Гц/ первого блока 1121 регистров, вторым - объединенные вторые управляющие входы /50 кГц/ блоков 112 регистров, третьим - объединенные третьи управляющие входы /80 МГц/ блоков 112 регистров. Каждый управляющий выход предыдущего блока 112 регистров является первым управляющим входом для каждого последующего блока регистров. Управляющий выход последнего блока 112 регистров подключен параллельно к четвертым управляющим входам всех блоков 112 регистров. Выходами накопителя 71 /76, 81/ кодов кадра являются выходы всех блоков 112 регистров, всего выходов 12,8×106 /12800×1000/. Блоки 112 регистров идентичны, каждый включает /фиг.11, 12/ первый 113, второй 114 ключи, распределитель 115 импульсов и восемь регистров 116, каждый из которых содержит по 1600 разрядов /по числу отсчетов в строке/. Информационным входом блока 112 являются 1-8 поразрядно объединенные третьи входы разрядов восьми регистров 116. Выходами являются параллельные выходы всех /1600/ разрядов восьми регистров 116, всего выходов 12800 /1600×8/. А выходы 1000 блоков 112 являются выходами накопителя кодов кадра, 12,8×106. Управляющими входами блока 112 являются: первым - первый управляющий вход /50 Гц/ первого ключа 113, вторым - сигнальный вход /50 кГц/ ключа 114, третьим - сигнальный вход ключа 113 /80 МГц/, четвертым - управляющий первый вход второго ключа 114. Выход первого ключа 113 подключен к входу распределителя 115 импульсов, выходы которого последовательно подключены к первым /тактовым/ входам разрядов восьми регистров 116 параллельно, последний выход /1600/ является управляющим выходом блока 112 регистров для следующего блока 112 /фиг.12/ и подключен к первому управляющему входу первого ключа 113. Выход второго ключа 114 подключен параллельно к вторым входам разрядов восьми регистров 116 и к второму управляющему входу своего ключа 114, прошедший первый импульс и закрывает ключ 114. Выходы накопителей кодов кадра 71, 76, 81 /фиг.6/ подключены к информационным входам своего блока формирования управляющих сигналов соответственно 72, 77, 82, назначение которых выполнять преобразование "код-число импульсов излучений" для каждого кода кадра. Блоки 72, 77, 82 идентичны, каждый включает /фиг.13/ блок 117 схем формирования импульсов, содержащий 1,6×106 схем, и преобразователи "код-число импульсов излучений" по числу разрешения кадра 1,6×106. Каждый преобразователь содержит последовательно соединенные дешифратор 118, 1-8 входы которого являются входами преобразователя, блок 119 ключей из 255 ключей и выходной ключ 120, включает СРИ 121 и источник 122 питания /для одного светодиода/. Выходы дешифратора 118 подключены к первым управляющим входам соответствующих из 255 ключей в блоке 119, выходы ключей объединены и подключены к управляющему входу Uот выходного ключа 120, сигнальный вход которого подключен к выходу источника питания 122. Входы СРИ 121 подключены к выходам своих схем формирования импульсов в блоке 117, каждый СРИ 121 имеет 255 разрядов, выходы которых подключены к сигнальным входам соответствующих ключей в блоке 119 /вход 2/. Информационными входами в блоках 72, 77, 82 являются входы всех дешифраторов 118. Выходы всех выходных ключей являются выходами этих блоков. Исходное состояние выходных ключей 120 и ключей в блоках 119 закрытое. С поступлением на управляющий вход блока 72 /77, 82/ импульса 50 Гц схемы блока 117 выдают параллельно на входы СРИ 121 импульсы Uп, запускающие СРИ 121 в работу. Длительность работы СРИ 121 - прохождение импульса Uп от первого до 255 разряда, составляющая период кадра 20 мс. Коды с блоков 71, 76, 81 синхронно и параллельно выдаются в дешифраторы 119 блоков 72, 77, 82 /фиг.6/. Сигналы с дешифраторов 119 соответственно величинам кодов открывают соответствующие ключи в блоках 119. На сигнальные входы ключей блока 119 последовательно с 255 разрядов СРИ 121 поступают сигналы, которые проходят открытые ключи и поступают на вход выходного ключа 120. Каждый импульс открывает выходной ключ на 78 мкс, и соответствующий светодиод в СД-экране запитывается на это время и излучает световой импульс длительностью 78 мкс. Импульс с разряда СРИ 121, пройдя открытый ключ в блоке 119, поступает и на его второй управляющий вход и закрывает ключ. Длительность единичного светового импульса определяется: , где 20 мс - длительность кадра 20000 мкс, 255 - разрешение 8-разрядного кода, число разрядов в СРИ 121.

Светодиод на экране 83 соответственно величине кода за период кадра запитывается столько раз по 78 мкс, сколько было открыто ключей в блоке 119 ключей. Чем больше код, тем больше световых импульсов выдаст светодиод в периоде кадра. Пример распределения световых импульсов за период кадра соответственно величинам кодов приводится в таблице 1.

| Таблица 1 | |||

| Код на входе дешифратора118 | Распределение световых импульсов в периоде кадра | Число импульсов за период кадра | |

| 00… | 01 | 1 | |

| 00… | 10 | 2 | |

| 00… | 11 | 3 | |

| 00… | 100 | 4 | |

| • | • | • | |

| • | • | • | |

| • | • | • | |

| 0 - отсутствие светового импульса, | |||

| 1, 2, 3…255 - номера следования световых импульсов. |

Следование световых импульсов в периоде кадра через равные интервалы соответствует природному восприятию зрением яркости и наилучшей достоверности в цветопередаче изображения. В блоках 71, 76, 81 за предшествующий период кадра сосредотачиваются коды цветовых сигналов кадра. Импульс СИС 25 Гц с блока 93, представляющий начало периода правого кадра стереопары, открывает ключ 94, пропускающий импульсы 50 Гц с шестого выхода синтезатора 89 частот. Первый импульс с ключа 94 соответствует началу периода правого кадра, второй импульс с ключа 94 соответствует началу периода левого кадра. Первый импульс с ключа 94 запускает в работу накопители 71, 76, 81, которые по окончании правого кадра выдают синхронно и параллельно все коды кадра в блоки 72, 77, 82, выполняющие импульсное запитывание соответствующих светодиодов СД-экрана 83, на экране цветное изображение правого кадра. С приходом второго импульса с ключа 94 в блоки 71, 76, 81 идет процесс накопления ими кодов левого кадра стереопары. При втором импульсе с ключа 94 триггер 95 выдает со второго выхода импульс в ИК-передатчик 84, излучение которого принимается ИК-приемником 86, который выдает управляющий сигнал в ЖК-ячейки левого стекла очков, затемняя его на 20 мс, затем схема ИК-приемника 86 сама выдает второй сигнал в ЖК-ячейки правого стекла, затемняя его на 20 мс. В результате каждый глаз видит свой кадр. Блок 88 выделения ССИ и блок 93 выделения СИС идентичны, каждый включает /фиг.17/ 4-разрядный счетчик 125 импульсов, дешифратор 126, элемент НЕ 127 и два диода. Информационным входом 1 блока 88 /93/ является счетный вход Uсч счетчика 125 импульсов, управляющим входом 2 является вход первого диода Д1, подключенный к управляющему входу счетчика 125. Первый вход блока 88 подключен к выходу первого формирователя 64 импульсов /фиг.6/, второй вход через диод Д1 подключен к выходу второго формирователя 65 импульсов. Первый выход блока 93 подключен к выходу второго формирователя 65 импульсов, а второй /управляющий/ вход через диод Д1 подключен к выходу первого формирователя 64 импульсов. Счетчик 125 ведет счет 14 импульсов /1110/, и три его старших разряда подключены к трем входам дешифратора 126, выход которого является выходом блока 88 /93/ и через второй диод Д2 объединяется с выходом элемента НЕ 127, который подключен после диода Д1 к управляющему входу Uо счетчика 125. Код ССИ поступает с блока 64 на первый вход блока 88, при этом с блока 65 на управляющий вход 2 счетчика 125 импульсов нет. Код СИС поступает на вход 1 блока 93 с блока 65, при этом с блока 64 на управляющий вход 2 импульсов нет. Работают блоки 88, 93 идентично /фиг.17/. С поступлением кода ССИ на счетный вход счетчик 125 ведет счет 14 импульсов подряд, в счетчике формируется код 1110, выходные сигналы со счетчика дешифрируются дешифратором, и с блока 88 /93/ появляется импульс ССИ /СИС/. Начиная со второго кода строки, с блока 65 пойдут коды на управляющий вход счетчика.

С приходом каждого импульса кода счетчик будет обнуляться и не достигнет счета 14 /1110/. Параллельно и на счетный вход идут импульсы кода с блока 64, при каждом нуле в коде элемент НЕ 127 выдает сигнал U0 и обнуляет счетчик. В дополнение с выхода дешифратора 126 сигнал ССИ через второй диод Д2 поступает на управляющий вход счетчика 125 и тоже обнуляет счетчик 125. Схема блоков 88, 93 исключает появление на выходе ложного сигнала ССИ, СИС. Каждый выпускаемый сейчас телевизор оснащается пультом дистанционного управления /ПДУ/. В предлагаемой системе также вводится ПДУ 98 с уже существующей в нем схемой, которая содержит и коды телевизионных каналов. Блок 99 учета времени приема телевизионных каналов /блок учета ВПТК/ включает /фиг.19/ счетчик 128 секунд, вход которого является информационным входом блока 99, и первый дешифратор 129, последовательно соединенные фотоприемник 130, вход которого является управляющим входом блока 99 и оптически соединен с излучающим выходом ПДУ 98, и второй дешифратор 131, включает каналы по числу принимаемых телевизионных каналов, каждый из которых включает последовательно соединенные ключ 132, счетчик 133 минут, третий дешифратор 134 и счетчик 135 часов, и включает постоянное запоминающее устройство /ПЗУ/ 136, в которое при изготовлении телевизора вводится его код, СРИ 137, USB-порт 138, модуль 139 флэш-памяти, формирователь 140 импульса, на вход которого при нажатии кнопки включателя 141 поступает импульс 1 Гц, и генератор 142 тактовых импульсов, обеспечивающий счетчики 128, 133, 135 соответствующими тактовыми импульми. Кнопка 141 выводится на лицевую сторону корпуса телевизора. Управляющие входы ключей 132 подключены к соответствующим выходам во втором дешифраторе 131, сигнальные входы ключей объединены и подключены к выходу первого дешифратора 129, выход которого подключен к входу счетчика 128. В каждом канале выход дешифратора 134 подключен к управляющему входу своего счетчика 133 минут. Выходы СРИ 137 подключены: первый - к управляющему входу блока 136 и остальные - последовательно к управляющим входам счетчиков 135 часов. Выходы блока 136 и счетчиков 135 объединены и через USB-порт 138 подключены к входу модуля 139 флэш-памяти. Счетчики 128, 133 шестиразрядные. На вход счетчика 128 поступает с девятого выхода синтезатора 89 частот частота 1 Гц. При подсчете 60 секунд с дешифратора 129 выдается импульс минуты, поступающий счетным импульсом параллельно на сигнальные входы всех ключей 132, он же обнуляет счетчик 128. Для просмотра передачи в ПДУ 98 нажимается кнопка нужного канала, код которого принимается фотоприемником 130 и поступает в дешифратор 131, сигнал с соответствующего выхода которого открывает ключ канала. Сигнал Uот держит ключ в открытом состоянии до переключения на другой канал. Ключ 132 пропускает импульсы минут в счетчик 133 часов своего канала, ведущий счет 60 минут. При счете 60 /111100/ дешифратор 134 выдает импульс часа в свой счетчик 135 часов и обнуляет счетчик 133. Счетчики 135 часов являются 16-разрядными постоянными запоминающими устройствами. Число 16 разрядов в них принято для накопления каждым счетчиком 135 наработки в 65520 часов, которая при работе телевизора по 12 часов в сутки обеспечивает учет работы телевизора в течение 16 лет. Перед выдачей наработки каналов телевизионного приемника в разъем USB-порта в корпусе телевизора вставляется энергонезависимый модуль 139 флэш-памяти [8, с.86, 9, с.4 цветной вставки]. Для выдачи наработки каналов телевизора на лицевой части корпуса телевизора нажимается кнопка включателя 141, формирователь 140 импульса выдает импульс соответствующей амплитуды и длительности как сигнал запуска Uп в работу СРИ 137. СРИ имеет разрядов по числу счетчиков 135, выходы этих разрядов подключены, начиная с блока 136, к управляющим входам блока 136 и регистров 135. Частота выдачи содержимого из блока 136 и счетчиков 135 100 Гц. По окончании выдачи модуль 139 флэш-памяти вынимается из порта 138 USВ и представляется в организацию по приему оплаты. Работник этой организации при помощи служебного компьютера снимает данные с модуля флэш-памяти и представляет пользователю телевизора распечатку квитанции для оплаты, в которой наработка представлена по каналам в часах, тариф оплаты каждого канала и подведена общая сумма за все каналы. Поканальная оплата за просмотр выявит настоящую потребность людей в темах телепередач.

ФЭП 1 первой матрицей ПЗИ 3 формирует три видеосигнала правого кадра. На каждый их трех слоев матрицы ПЗИ 3 с ключа 19 поступают импульсы 50 кГц частоты строк для считывания сигналов пикселов по вертикали /вход 1 матрицы/. На вторые входы матрицы с ключа 21 поступают импульсы 40 МГц для считывания зарядов по горизонтали [2, с.832]. Сигналы с трех слоев матрицы поступают в предварительные усилители 4, 5, 6, с выходов которых они поступают в АЦП 9, 10, 11, с выходов которых 8-разрядные коды цветовых сигналов с дискретизацией 40 МГц поступают на входы кодеров 12-14. Синхронизация считывания сигналов с матрицы ПЗИ 3 с началом периода правого кадра производится открытием ключа 18 передним фронтом синхроимпульса стереопары 25 Гц /СИС/. Ключ 18 пропускает импульсы 50 кГц, первый из них является импульсом правого кадра, и с первого выхода триггера 23 открывает на 20 мс ключи 19, 21, второй является импульсом левого кадра и открывает со второго выхода триггера 23 ключи 20, 22, пропускающие на первый и второй входы второй матрицы ПЗИ 8 импульсы соответственно 50 кГц и 40 МГц для считывания с нее зарядов пикселов левого кадра. Сигналы с трех слоев ПЗИ 8 поступают на входы тех же предварительных усилителей 4-6. Синтезатор 17 частот выдает: с первого выхода - импульсы 25 Гц на управляющий вход ключа 18, на вход СРИ 25 и на четвертый управляющий вход блока 15, со второго - импульсы 50 кГц на сигнальные входы ключей 19 и 20, на третий управляющий вход блока 15 и на вторые управляющие входы АЦП 26, 27, с третьего выхода - импульсы Uд дискретизации 40 МГц в АЦП 9-11, с четвертого - импульсы 50 Гц частоты кадров на сигнальный вход первого ключа 18, с пятого - импульсы Uвыд 10 МГц с кодеров 12-14 и на первые управляющие входы формирователя 15 кодов и АЦП 26, 27, с шестого выхода - тактовые импульсы 140 МГц на второй управляющий вход блока 15, с седьмого - импульсы 100 кГц дискретизации кодов звука на третьи управляющие входы АЦП 26, 27, с восьмого - синусоидальные колебания несущей частоты 2100 МГц со стабильностью 10-7 в передатчик 28 радиосигналов.

Работа кодеров 12-14, фиг.3.

Коды поступают на 1-8 входы регистра 32, на первые входы схемы 33 сравнения и на входы блока 36 элементов задержек. Исходное состояние ключей в блоке 37 открытое. Код в блоке 36 задерживается на время сравнения /18 нс/ и поступает через открытые ключи блока 37 на 1-8 входы буферного накопителя 38 кодов кадра, емкостью 200×103 9-разрядных кодов. Схема 33 сравнения выполняет сравнение по величине каждого предыдущего и последующего кодов для выявления их равенства или неравенства. При следовании неравных кодов они проходят через блок 36, открытые ключи блока 37 и поступают на 1-8 входы буферного накопителя 38 кодов. Выдача кодов из блока 38 выполняется сигналами Uвыд 10 МГц с выхода 2 блока 17. Поступление кодов в блок 38 при следовании неравных кодов идет с частотой 40 МГц. В общем потоке кодов имеется большое число равных по величине кодов, идущих последовательно друг за другом. За счет равных кодов, идущих друг за другом, кодер и выполняет сжатие потока кодов. Коэффициент сжатия плавающий от 1 до 255, общий коэффициент сжатия потока кадра принимается не менее 4, поэтому частота выдачи с блока 38 принимается 10 МГц . При коэффициенте сжатия выше 4 частота 10 МГц выдачи будет тем более удовлетворять. Схема 33 сравнения выполняет сравнение кодов и представлена двумя микросхемами 530СП1 с временем сравнения 18 нс [10, с.279]. При неравенстве кодов А>В появляется сигнал на выходе 2 блока 33 /в микросхеме выход 5 [10, с.272, рис.2.190], при равенстве кодов А=В - сигнал с выхода 1 /в микросхеме выход 7/. При равенстве кодов сигнал с выхода 1 блока 33 закрывает ключи в блоке 37, поступает счетным импульсом в счетчик 34 импульсов и, как сигнал Uвыд, на первый управляющий вход регистра 32. Счетчик 34 8-разрядный, максимальный код в нем 255 /11111111/, отсюда и максимальный коэффициент сжатия 255. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [10, c.428]. При появлении неравных кодов со схемы 33 следует сигнал с выхода 2 или 3 /А<В/, которые объединены, сигнал с них используется для выдачи кода числа равных кодов из счетчика 34 импульсов через диоды на входы блока 38 и для заполнения в блоке 38 девятого разряда, с которого сигнал используется для опознания по нему кода числа равных кодов при декодировании. Этот же сигнал открывает ключи в блоке 37 /вход 1/ и обнуляет регистр 32. Выданный перед этим с блока 38 код является первым кодом последовательности, диаграмма 1, фиг.4, они помечены крестиками.

Коды, равные по величине и подсчитанные счетчиком 34, исключаются из потока. Емкость буферного накопителя 38 составляет 200×103 9-разрядных кодов для обеспечения темпа следования кодов с частотой 10 МГц. При следовании подряд кодов, разных по величине более 255, в работу вступает дешифратор 35. При коде 11111111 дешифратор 35 выдает сигнал, который одновременно открывает ключи в блоке 37, обнуляет регистр 32, сигналом Uвыд выдает код из счетчика 34 /вход 1/ и обнуляет счетчик 34 /вход 2/, а в 9-й разряд блока 38 поступает сигнал опознания числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы 33 сравнения, которая обеспечивает до 40 Мбайт/с и удовлетворяет частоте следования кодов на входе кодера 40 МГц /фиг.3/. С выходов кодеров 12-14 9-разрядные коды в параллельном виде поступают на первый и второй информационные входы блока 15 /фиг.1/. На первый информационный вход блока 15 поступают с первого по девятый разряды кодов с кодера 12 и с первого по четвертый разряды кода с кодера 13, на второй информационный вход блока 15 поступают с пятого по девятый разряды кодов с кодера 13 и с первого по девятый разряды кодов с кодера 14. Первым кодом в первой строке правого кадра идет 14-разрядный код СИС /фиг.2/ на шестой информационный вход блока 15. Начиная со второй строки, первым кодом в каждой строке идет код ССИ 14-разрядный с СРИ 24 на пятый информационный вход блока 15. В сжатом потоке кодов со второго по 198 идут коды цветовых сигналов, затем два кода 199 и 200 звука 3в1 и 3в2. 9-разрядный код сигнала R и 1-4 разряды сигнала В составляют суммарный код, поступающий на первый информационный вход блока 15, 1-9 разряды сигнала G и 5-9 разряды кодов сигнала В составляют суммарный код, поступающий на второй информационный вход блока 15. На выходе блока 15 единицы в суммарном коде сигнала R и 1-4 разрядов сигнала В представляются положительными полусинусоидами моночастоты 140 МГц, а единицы в суммарном коде сигнала G и 5-9 разрядов В представляются отрицательными полусинусоидами той же частоты.

Работа формирователя 15 кодов, фиг.5.

Временные диаграммы работы на фиг.18. Блок 15 преобразует параллельные коды в последовательные и заменяет в них представление единиц с импульсов на положительные полусинусоиды моночастоты 140 МГц в 1-9 разрядах кодов R и 1-4 разрядах кодов В и на отрицательные полусинусоиды в 1-9 разрядах кодов G и 5-9 разрядах кодов В. На первый информационный вход блока 15 на первые 13 входов элементов И блока 39 поступают параллельно и синхронно разряды кодов R с кодера 12 и 1-4 разряды кодов В с кодера 13. На второй информационный вход блока 15 на первые входы 14 элементов И блока 44 поступают 1-9 разряды кодов сигнала G и 5-9 разряды кодов В с кодеров соответственно 14 и 13. На третий информационный вход в блок 49 поступают 14-