Дифференциальный усилитель с малым напряжением питания

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)) при низковольтном питании. Технический результат: расширение диапазона изменения входных синфазных сигналов. Дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входные транзисторы (Т), базы которых подключены к первому (3) и второму (4) входам ДУ, выходное токовое зеркало (ТЗ) (5), имеющее токовый вход (6), токовый выход (7), первый (8) и второй (9) потенциальные входы, первый (10), второй (11) и третий (12) токостабилизирующие двухполюсники (ТД), причем первый (8) и второй (9) потенциальные входы ТЗ (5) связаны с шиной (13) первого источника питания (ИП) через первый (10) и второй (11) ТД, токовый вход (6) ТЗ (5) связан с шиной (14) второго ИП через третий (12) ТД, а выход (15) ДУ соединен с токовым выходом (7) ТЗ (5). Эмиттеры первого (1) и второго (2) входных Т соединены с соответствующими первым (8) и вторым (9) потенциальными входами ТЗ (5) через первую (16) и вторую (17) цепи согласования потенциалов. 6 з.п. ф-лы, 19 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)) при низковольтном питании.

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (КДУ) на n-p-n и p-n-p транзисторах, которые стали основой более чем 20 серийных ОУ, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 50 патентов в различных странах. Предлагаемое изобретение относится к данному подклассу устройств.

Одной из модификаций «перегнутых» каскодных дифференциальных усилителей (КДУ) является схема фиг.1, представленная в публикациях [1-13]. Она используется в ОУ ряда зарубежных фирм (НА2539, ОР-90, ОР-42).

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии SGB25VD, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы Х диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технология SGB25VD накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы

(Uкэ.max=2,9÷3,0 В). Создание IP блоков для SiGe технологии SGB25VD является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем. Предлагаемое изобретение относится к данному направлению развития микроэлектроники.

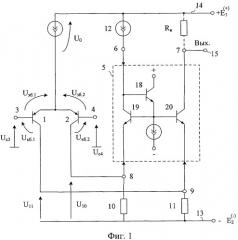

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №6.542.030, содержащий первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 и второму 4 входам дифференциального усилителя, выходное токовое зеркало 5, имеющее токовый вход 6, токовый выход 7, первый 8 и второй 9 потенциальные входы, первый 10, второй 11 и третий 12 токостабилизирующие двухполюсники, причем первый 8 и второй 9 потенциальные входы выходного токового зеркала 5 связаны с шиной 13 первого источника питания через первый 10 и второй 11 токостабилизирующие двухполюсники, токовый вход 6 и токовый выход 7 выходного токового зеркала 5 связаны со второй 14 шиной источника питания через третий 12 токостабилизирующий двухполюсник, а выход 15 дифференциального усилителя соединен с токовым выходом 7 выходного токового зеркала 5.

Существенный недостаток известного дифференциального усилителя (ДУ) состоит в том, что он выполнен на транзисторах разного типа проводимости, что не позволяет использовать перспективные SiGe технологические процессы (SGeB25VD) для изготовления аналоговых микросхем СВЧ-диапазона. Кроме этого известная схема КДУ из-за особенностей архитектуры имеет при низковольтном питании (Е(+), Е(-)) узкий диапазон изменения входных синфазных сигналов и при малых Е(+)=Е(-) оказывается неработоспособной.

Основная цель предлагаемого изобретения состоит в расширении диапазона изменения входных синфазных сигналов ДУ, а также создании условий, при которых все элементы схемы ДУ могут быть реализованы в рамках технологического процесса SGB25VD для построения на его основе СВЧ-интегральных устройств 1÷25 ГГц при напряжениях питания более 1,5 В.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 и второму 4 входам дифференциального усилителя, выходное токовое зеркало 5, имеющее токовый вход 6, токовый выход 7, первый 8 и второй 9 потенциальные входы, первый 10, второй 11 и третий 12 токостабилизирующие двухполюсники, причем первый 8 и второй 9 потенциальные входы выходного токового зеркала 5 связаны с шиной 13 первого источника питания через первый 10 и второй 11 токостабилизирующие двухполюсники, токовый вход 6 выходного токового зеркала 5 связан со второй 14 шиной источника питания через третий 12 токостабилизирующий двухполюсник, а выход 15 дифференциального усилителя соединен с токовым выходом 7 выходного токового зеркала 5, предусмотрены новые элементы и связи - эмиттеры первого 1 и второго 2 входных транзисторов соединены с соответствующими первым 8 и вторым 9 потенциальными входами выходного токового зеркала 5 через первую 16 и вторую 17 цепи согласования потенциалов.

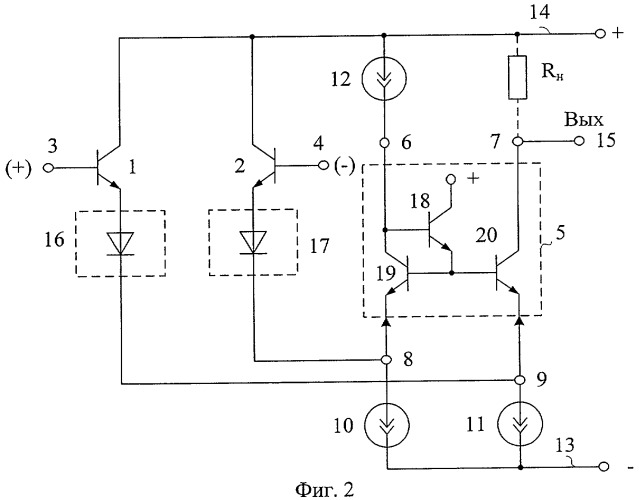

Схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения показана на чертеже фиг.2.

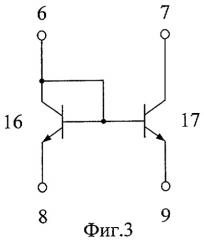

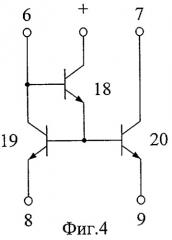

На чертеже фиг.3-фиг.6 показаны частные варианты построения выходного токового зеркала 5. Схема фиг.3 применена в ДУ с архитектурой фиг.1 в патентах США №№5.734.296, 4.293.824, 6.542.030, 5.734.296, 5.422.600, 6.456.163; фиг.4 - в патентах №№5.420.540, 4.293.824; фиг.5 - в патенте №5.952.882; фиг.6 - в патенте №6.617.466.

На чертеже фиг.7 (п.3, п.4 формулы изобретения) показана схема ДУ фиг.2 для случая, когда в качестве цепей согласования 16 и 17 используются p-n переходы.

На чертеже фиг.8 показана схема заявляемого устройства в соответствии с п.5 формулы изобретения и выполнение цепей согласования 16 и 17 в виде резисторов.

На чертеже фиг.9 представлен ДУ, соответствующий п.6 формулы изобретения.

На чертеже фиг.10 представлена схема ДУ фиг.2 в среде компьютерного моделирования Cadance на моделях интегральных SiGe СВЧ-транзисторов IHP. Результаты компьютерного моделирования данной схемы - зависимость коэффициента усиления по напряжению Ку и коэффициента ослабления входных синфазных сигналов Кос.сф - приведены на чертежах фиг.11 и фиг.12.

На чертеже фиг.13, в соответствии с п.3 и п.7 формулы изобретения база и коллектор входного транзистора 2 соединены со входом 4, а также с выходом 31 буферного усилителя, выполненного на биполярном транзисторе 32. В этой схеме статический режим транзистора 32 устанавливается как разность между токами источников опорного тока 12 и 10. Аналогично статический режим транзистора 1 определяется как разность токов двухполюсника 29 и 11.

На чертеже фиг.14 показана схема ДУ фиг.13 в среде компьютерного моделирования Cadance на моделях интегральных SiGe СВЧ-транзисторов IHP. При этом в схеме использовались идеальные модели двухполюсников 10, 11, 12 и 29.

На чертежах фиг.15 показана схема ДУ фиг.13 с использованием реальных двухполюсников 10, 11, 12, 29, реализованных на полевых транзисторах техпроцесса SGB25VD. При этом на схеме фиг.15б показаны координаты статического режима активных элементов схемы фиг.15а.

На чертеже фиг.16 представлены зависимость петлевого усиления схемы фиг.15 от частоты, а также фазовый сдвиг по петле обратной связи. Из фиг.16 следует, что частота единичного усиления схемы фиг.15 равна 9,1 ГГц.

На чертеже фиг.17 показана амплитудно-частотная характеристика коэффициента усиления по напряжению замкнутого усилителя фиг.15 при 100% обратной связи. Из фиг.17 следует, что верхняя граничная частота схемы фиг.15 по уровню -3 дБ - 12 ГГц.

На чертеже фиг.18 показан переходный процесс в усилителе фиг.15 при подаче на его вход импульсного сигнала. Из чертежа фиг.18 можно найти, что максимальная скорость нарастания выходного напряжения в усилителе фиг.15 более 4000 В/мкс.

На чертеже фиг.19 показан выходной uвых синусоидальный сигнал в усилителе фиг.15 в зависимости от амплитуды входного напряжения uвх при 100% обратной связи. Из чертежа фиг.19 следует, что усилитель фиг.15 имеет максимальное выходное напряжение (при напряжении питания ±1,5 В) не менее чем 0,6 В.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 и второму 4 входам дифференциального усилителя, выходное токовое зеркало 5, имеющее токовый вход 6, токовый выход 7, первый 8 и второй 9 потенциальные входы, первый 10, второй 11 и третий 12 токостабилизирующие двухполюсники, причем первый 8 и второй 9 потенциальные входы выходного токового зеркала 5 связаны с шиной 13 первого источника питания через первый 10 и второй 11 токостабилизирующие двухполюсники, токовый вход 6 выходного токового зеркала 5 связан со второй 14 шиной источника питания через третий 12 токостабилизирующий двухполюсник, а выход 15 дифференциального усилителя соединен с токовым выходом 7 выходного токового зеркала 5. Эмиттеры первого 1 и второго 2 входных транзисторов соединены с соответствующими первым 8 и вторым 9 потенциальными входами выходного токового зеркала 5 через первую 16 и вторую 17 цепи согласования потенциалов.

На чертеже фиг.2, в соответствии с п.2 формулы изобретения, коллектор первого 1 и второго 2 входных транзисторов соединены с шиной 14 второго источника питания.

Показанные на чертеже фиг.3-фиг.6 частные случаи выполнения выходного токового зеркала 5 содержат элементы 16-27.

На чертеже фиг.7 в соответствии с п.3 и п.4 формулы изобретения коллектор второго 2 входного транзистора подключен ко второму входу 4 дифференциального усилителя (п.3), а коллектор первого 1 входного транзистора соединен с первым 3 входом дифференциального усилителя (п.4).

На чертеже фиг.8 показан ДУ, соответствующий п.5 формулы изобретения, в котором в качестве двухполюсников 16 и 17 используются резисторы, а между эмиттерами входных транзисторов 1 и 2 включен двухполюсник 28 (резистор или два параллельно-встречно включенных p-n перехода, корректирующая емкость и т.д.). При этом в схеме используется в качестве активной нагрузки источник опорного тока 29.

На чертеже фиг.9, соответствующей п.6 формулы изобретения, к первому 3 и второму 4 входам дифференциального усилителя подключены входы вспомогательного дифференциального усилителя, причем выход дифференциального усилителя 7 соединен с выходом 7* вспомогательного дифференциального усилителя, а каждый из транзисторов вспомогательного дифференциального усилителя имеет тип проводимости, противоположный типу проводимости соответствующего транзистора дифференциального усилителя по п.1 формулы изобретения. Транзисторы вспомогательного дифференциального усилителя, соответствующие по схеме транзисторам дифференциального усилителя по п.1 формулы изобретения, обозначены знаком (*). При этом в схему фиг.9 введен буферный усилитель 30, имеющий выход 31.

На чертеже фиг.13, в соответствии с п.7 формулы изобретения, база и коллектор входного транзистора 2 соединены со входом 4, а также с выходом 31 буферного усилителя 30, выполненного на биполярном транзисторе 32. В этой схеме статический режим транзистора 32 устанавливается как разность между источниками опорного тока 12 и 10. Аналогично статический режим транзистора 1 определяется как разность токов двухполюсника 29 и 11.

Рассмотрим работу известного (фиг.1) и заявляемого (фиг.2) ДУ на примере сравнительного анализа схем фиг.1 и фиг.2.

В соответствии со вторым законом Кирхгофа можно записать следующее уравнение для ДУ-прототипа фиг.1:

где U10=U11=const - статическое напряжение на двухполюсниках 10 и 11;

Uкб.1=Uкб.2=f(Uc) - напряжение коллектор-база транзисторов 1 и 2;

Uc=Uc3=Uc4 - входное синфазное напряжение ДУ;

Uэб.1=Uэб.2≈0,7 В - напряжение эмиттер-база транзисторов 1 и 2;

U0=φ(Uc) - напряжение на источнике опорного тока в эмиттерной цепи транзисторов 1 и 2.

При изменении входного синфазного сигнала Uс=Uс3=Uс4 изменяются напряжения

Uкб.1=Uкб.2 и U0, причем их приращения

Максимальное положительное приращение Uc определяется минимально возможным значением напряжения на источнике опорного тока U0min:

При реализации источника опорного тока на биполярных транзисторах выполняется неравенство U0min≥Uэб≈0,7 В. Поэтому

Максимальное отрицательное приращение синфазного сигнала зависит от статического напряжения коллектор-база транзисторов 1 и 2

Поэтому максимально допустимый диапазон изменения входного синфазного напряжения ДУ-прототипа, при котором его элементы работают в линейном режиме:

Для обеспечения управляемости выходным токовым зеркалом 5 необходимо, чтобы U10=U11>>φт≈25 мВ, где φт - температурный потенциал. Выберем для определенности U10=U11=250 мВ. Тогда в схеме фиг.1

В предлагаемом усилителе (например, фиг.3) более широкий диапазон изменения входного синфазного напряжения реализуется, если при прочих равных условиях (построении двухполюсников 10 и 11 на транзисторах с U0min=0,7 B) напряжение на цепях согласования потенциалов 16 и 17 (U16=U17) меньше, чем напряжение U10=U11=250 мВ в схеме фиг.1:

или

В схеме фиг.2 величина U17 может принимать нулевое значение без потери стабильности, а в схеме фиг.1 - нет. Таким образом, предлагаемое устройство имеет более широкий диапазон входных синфазных сигналов и может быть реализовано на n-p-n транзисторах с предельным напряжением коллектор-эмиттер Uкэ.max=2,9 В

(Е(+)=E(-)=1,5 В).

Работоспособность предлагаемого устройства при низковольтном питании подтверждается компьютерным моделированием в средах PSpice и Cadance на моделях интегральных СВЧ-транзисторов IHP, имеющих предельное напряжение коллектор-эмиттер 2,9 В.

Особенность схемы ДУ фиг.7 - работа входных транзисторов 1 и/или 2 в диодном режиме. Это позволяет иметь малое входное дифференциальное сопротивление для дифференциального сигнала, что бывает важным для согласования входных цепей в СВЧ-диапазоне.

Пример практического включения ДУ фиг.7 в схеме ВЧ повторителя напряжения приведен на чертеже фиг.13.

Замечательная особенность схемы фиг.9 - высокая симметрия статических режимов, а также улучшенные динамические параметры на переменном токе. Ее недостаток - наличие n-p-n и p-n-p транзисторов, что требует применения более дорогостоящих технологических процессов, например SG25H2. Следует заметить, что предлагаемое схемотехнические решение фиг.9 ДУ класса «dual-input-stage» более симметрично, чем запатентованная фирмой Analog Devices схема усилителя (патент №4.649.352, патентная заявка 2005/0127999, патент №6.420,931).

Таким образом, предлагаемое схемотехническое решение позволяет использовать однотипные SiGe-транзисторы с относительно низким напряжением питания в структуре не только различных аналоговых устройств, но и СФ блоков систем на кристалле. Этот важный результат расширяет область практического использования SGB25VD SiGe технологии и, следовательно, повышает технико-экономические показатели микроэлектронных изделий. Так, например, создание новой (под указанную технологию) схемотехники широкодиапазонных операционных усилителей позволит не только повысить качественные показатели СВЧ-фильтров, квадратурных модуляторов, демодуляторов и других устройств нового поколения, образующих СФ блоки СВЧ РЭА, так и создать новую номенклатуру ИС более широкого функционального применения.

Литература

1. Патент США №4.600.893

2. Патент США №6.456.162

3. Патент США №6.501.333

4. Патент США №6.542.030

5. Патент США №4.293.824

6. Патент США №5.734.296

7. Патент США №5.420.540

8. Патент США №5.523.718

9. Патент США №4.644.295

10. Патент США №5.422.600

11. Патент США №6.456.163

12. Патент США №5.952.882

13. Патент США №6.617.466

1. Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены к первому (3) и второму (4) входам дифференциального усилителя, выходное токовое зеркало (5), имеющее токовый вход (6), токовый выход (7), первый (8) и второй (9) потенциальные входы, первый (10), второй (11) и третий (12) токостабилизирующие двухполюсники, причем первый (8) и второй (9) потенциальные входы выходного токового зеркала (5) связаны с шиной (13) первого источника питания через первый (10) и второй (11) токостабилизирующие двухполюсники, токовый вход (6) выходного токового зеркала (5) связан с шиной (14) второго источника питания через третий (12) токостабилизирующий двухполюсник, а выход (15) дифференциального усилителя соединен с токовым выходом (7) выходного токового зеркала (5), отличающийся тем, что эмиттеры первого (1) и второго (2) входных транзисторов соединены с соответствующими первым (8) и вторым (9) потенциальными входами выходного токового зеркала (5) через первую (16) и вторую (17) цепи согласования потенциалов.

2. Устройство по п.1, отличающееся тем, что коллектор первого (1) и второго (2) входных транзисторов соединены с шиной (14) второго источника питания.

3. Устройство по п.1, отличающееся тем, что коллектор второго (2) входного транзистора подключен ко второму входу (4) дифференциального усилителя, а коллектор первого (1) входного транзистора соединен с шиной (14) второго источника питания.

4. Устройство по п.1, отличающееся тем, что коллектор первого (1) входного транзистора соединен с первым (3) входом дифференциального усилителя, а коллектор второго (2) входного транзистора соединен с шиной (14) второго источника питания.

5. Устройство по п.1, отличающееся тем, что между эмиттерами входных транзисторов (1) и (2) включен вспомогательный двухполюсник (28).

6. Устройство по п.1, отличающееся тем, что к первому (3) и второму (4) входам дифференциального усилителя подключены входы вспомогательного дифференциального усилителя, причем выход дифференциального усилителя (7) соединен с выходом (7*) вспомогательного дифференциального усилителя, а каждый из транзисторов вспомогательного дифференциального усилителя имеет тип проводимости, противоположный типу проводимости соответствующего транзистора дифференциального усилителя по п.1 формулы изобретения.

7. Устройство по п.3, отличающееся тем, что второй (4) вход дифференциального усилителя связан с выходом (31) буферного усилителя, вход которого соединен с выходом (15) дифференциального усилителя.