Управляемый двухкаскадный дифференциальный усилитель с отрицательной обратной связью по синфазному сигналу

Иллюстрации

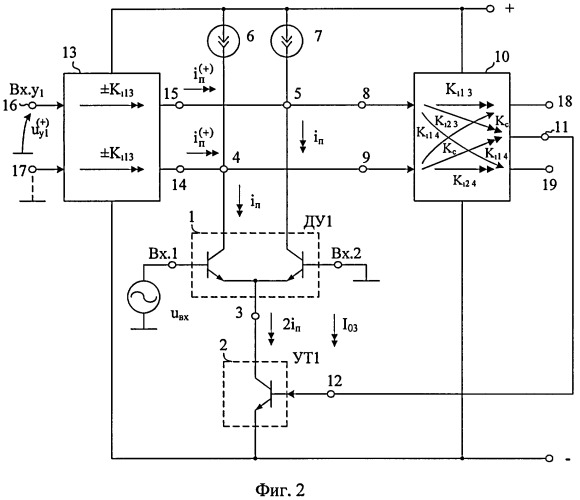

Показать всеПредлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники. Технический результат: уменьшение напряжения питания при сохранении функции электронного управления. Дифференциальный усилитель (ДУ) содержит входной параллельно-балансный каскад (1) с управляемым источником тока (УИТ) (2) в общей эмиттерной цепи (3), первый (4) и второй (5) токовые выходы которого связаны с первым (6) и вторым (7) двухполюсниками нагрузки и соответствующими первым (8) и вторым (9) входами выходного дифференциального каскада (ДК) (10), причем выход (11) для синфазного сигнала ДК (10) подключен к управляющему входу (12) УИТ (2) в общей эмиттерной цепи (3). В схему введен преобразователь «управляющее напряжение-ток» (13), имеющий первый (14) и второй (15) синфазные выходы, связанные с соответствующими первым (4) и вторым (5) токовыми выходами входного параллельно-балансного каскада (1). 6 з.п. ф-лы, 17 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники.

В настоящее время в аналоговой микросхемотехнике в составе управляемых усилителей, систем электронной регулировки усиления широкое применение находят схемы на основе дифференциальных каскадов с изменяющимся статическим режимом. Такая структура стала основой построения практически всех известных в настоящее время прецизионных управляемых усилителей и аналоговых перемножителей сигналов. В этой связи задача улучшения параметров этого функционального узла относится к числу достаточно актуальных задач современной микроэлектроники.

В цифровых интегральных микросхемах результатом увеличения скорости обработки информации стали тенденции постоянного уменьшения напряжения питания, что является «анафемой» в аналоговом проектировании с высокими характеристиками. При технологических нормах 350 нм (напряжение питания 3,3 В) по-прежнему достаточно схемотехнических возможностей для аналоговых проектирований с высокими характеристиками, хотя наличие 5 В питания было бы предпочтительнее. При нормах 180 нм (1,8 В) процесс усложняется и статические характеристики аналоговых устройств страдают. При 90÷130 нм технологии необходимо развитие новых подходов к проектированию микросхем, ориентированных на обеспечение работоспособности при еще более низковольтном питании.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм начинают использовать технологическое оборудование для SiGe-технологий SGB25VD и SGB25H2, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы Х диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технологии SGB25VD и SGB25H2 накладывают дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в относительно низковольтных режимах работы транзисторов. Создание IP-блоков для SiGe-технологий SGB25VD и SGB25H2 является (наряду с их освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем.

Существуют схемотехнические методы, позволяющие использовать однотипные транзисторы с относительно низким напряжением их питания в структуре не только различных узлов и устройств, но и СФ-блоков систем на кристалле. Этот важнейший для указанной проблемы теоретический результат позволяет в перспективе расширить область практического использования техпроцессов SGB25VD и SGB25H2 SiGe и, следовательно, повысить технико-экономические показатели микроэлектронных изделий. Так, например, создание специальной под указанные технологии схемотехники управляемых усилителей позволит не только повысить качественные показатели управляемых СВЧ-фильтров, квадратурных модуляторов и демодуляторов и других устройств нового поколения, образующих СФ-блоки СВЧ РЭА специального назначения, так и создать принципиально новую номенклатуру ИС более широкого функционального применения.

Таким образом, приведенный выше анализ тенденций в микроэлектронике показывает, что последние несколько лет источники питания с напряжением 5 В вытесняются более низковольтными. Требования к уменьшению рассеиваемой мощности и уменьшению числа батарей в таких приложениях, как беспроводные устройства связи и персональные компьютеры, уже привели к снижению напряжения питания в цифровых схемах до уровня 1,5 В. Эта тенденция, как отмечалось выше, реализована в современных SiGe-транзисторах, которые сконструированы так, чтобы обеспечить максимальную частоту среза (f1) в компромиссе с напряжением пробоя (Uпp). Для кремниевых транзисторов существует следующее фундаментальное ограничение: f1×Uпp≈const, т.е. малые размеры транзисторов, обеспечивающие высокие значения f1 (до 200 ГТц), привели к снижению напряжения питания микросхем до 1,2÷1,5 В.

Уменьшение напряжения питания (Еп) в биполярных схемах приводит к появлению новых проблем и некоторые из них становятся особенно важными при напряжении питания менее 2 В. Принципиальная сложность уменьшения напряжения Еп состоит в том, что биполярный транзистор имеет фиксированное напряжение база-эмиттер Uбэ, которое не уменьшается линейно с уменьшением технологических норм, так как

где φт=kT/q, Iк - ток коллектора, и Is - обратный ток эмиттерного р-n перехода. При этом параметры транзистора и уровни тока оказывают слабое влияние на напряжение Uбэ. На практике плотность тока в биполярном транзисторе (Iк/Is), изменяя свое значение, также слабо влияет на напряжение Uбэ. Если в используемой технологии Uбэ=0,7÷0,8 В, то использование 1,5 В источника питания приводит к тому, что между «землей» и шиной Еп не может быть включено больше чем один р-n переход.

Учитывая вышесказанное, а также численные значения напряжения Uбэ≈700÷800 мВ, можно сделать вывод о том, что при напряжении питания 1,5 В запрещается использовать многоярусные дифференциальные пары или классические каскадные конфигурации (архитектуры).

Таким образом, отсутствие возможности масштабирования напряжения на переходе база-эмиттер обостряет проблему дальнейшего масштабирования напряжения питания схем управляемых усилителей на биполярных транзисторах.

В современной электронике известны схемы классических дифференциальных усилителей (ДУ) [1-14] с отрицательной обратной связью по синфазному сигналу, которые стали основой многих серийных аналоговых микросхем первого и второго поколения. В последние годы ДУ данного класса стали снова активно применяться в структуре СВЧ-устройств [1, 2, 3], реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1) В, которое характерно для высокочастотных транзисторов с предельными частотами 120÷200 ГГц.

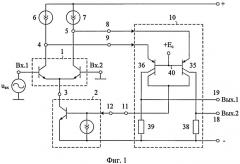

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель на основе «перегнутого» каскада, описанный в патенте РФ №2319291, содержащий входной параллельно-балансный каскад 1 с управляемым источником тока 2 в общей эмиттерной цепи 3, первый 4 и второй 5 токовые выходы которого связаны с первым 6 и вторым 7 двухполюсниками нагрузки и соответствующими первым 8 и вторым 9 входами выходного дифференциального каскада 10, причем выход 11 для синфазного сигнала выходного дифференциального каскада 10 подключен к управляющему входу 12 управляемого источника тока 2 в общей эмиттерной цепи 3. Аналогичную архитектуру, но с иными типами выходного дифференциального каскада 10 имеют другие ближайшие аналоги [1, 3÷14].

Существенный недостаток известного ДУ состоит в том, что он не имеет специального входа «У» для электронного управления коэффициентом усиления по напряжению. Это существенно сужает область его использования, не позволяет реализовывать на его основе адаптивные функциональные узлы систем на кристалле, например СВЧ-операционные усилители с парафазным выходом, у которых петлевое усиление изменяется по заданному алгоритму в зависимости от свойств источников сигнала и цепей обратных связей (см., например, патент РФ №2307393 «Способ управления коэффициентом передачи решающего усилителя с глубокой отрицательной обратной связью»).

Основная цель предлагаемого изобретения состоит в создании условий для электронного управления коэффициентом усиления по напряжению ДУ. Реализация этой цели позволяет выполнять на базе заявляемого устройства не только широкополосные ВЧ- и СВЧ-усилители с регулируемыми параметрами, но создавать на его основе более сложные функциональные узлы, например аналоговые перемножители сигналов.

Дополнительная цель - создание архитектуры ДУ с малым напряжением питания при сохранении функции электронного управления его коэффициентом усиления по напряжению, а также обеспечения возможности практической реализации устройств по SiGe-технологии.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1 с управляемым источником тока 2 в общей эмиттерной цепи 3, первый 4 и второй 5 токовые выходы которого связаны с первым 6 и вторым 7 двухполюсниками нагрузки и соответствующими первым 8 и вторым 9 входами выходного дифференциального каскада 10, причем выход 11 для синфазного сигнала выходного дифференциального каскада 10 подключен к управляющему входу 12 управляемого источника тока 2 в общей эмиттерной цепи 3, предусмотрены новые элементы и связи - в схему введен преобразователь «управляющее напряжение-ток» 13, имеющий первый 14 и второй 15 синфазные выходы, связанные с соответствующими первым 4 и вторым 5 токовыми выходами входного параллельно-балансного каскада 1.

Здесь и далее под синфазными выходами 14 и 15 понимаются выходные узлы преобразователя «управляющее напряжение-ток» 13, у которых выходные токи изменяются одинаково (на одну и ту же величину) при изменении управляющего напряжения Uy.

Схема заявляемого устройства, соответствующего п.1 формулы изобретения, показана на чертеже фиг.2.

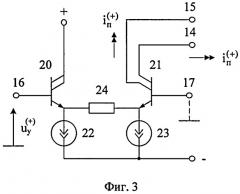

На чертеже фиг.3 показана схема заявляемого устройства в соответствии с п.2 формулы изобретения.

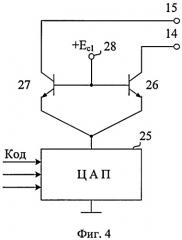

На чертеже фиг.4 показана схема предлагаемого ДУ по п.3 формулы изобретения.

На чертеже фиг.5 показана схема предлагаемого устройства по п.4 формулы изобретения.

Таким образом, чертежи фиг.3, фиг.4 и фиг.5 характеризуют различные модификации и варианты построения преобразователя 13.

На чертеже фиг.6 показана схема предлагаемого устройства по п.5 формулы изобретения.

На чертеже фиг.7 показана схема предлагаемого устройства по п.6 формулы изобретения.

На чертеже фиг.8 показана схема предлагаемого устройства по п.7 формулы изобретения.

Таким образом, чертежи фиг.6, фиг.7 и фиг.8 характеризуют различные варианты построения выходного дифференциального каскада 10.

На чертеже фиг.9 показана схема предлагаемого устройства по п.2 и п.6 формулы изобретения.

На чертеже фиг.10 показана схема предлагаемого устройства по п.2 и п.5 формулы изобретения.

На чертеже фиг.11 показана схема предлагаемого устройства по п.4 и п.5 формулы изобретения.

На чертеже фиг.12 показана схема предлагаемого устройства по п.3 и п.6 формулы изобретения.

На чертеже фиг.13 показана схема предлагаемого устройства по п.2 и п.7 формулы изобретения.

На чертеже фиг.14 представлена схема ДУ, соответствующая п.2 и п.7 формулы изобретения, для случая, когда управляющий источник тока 2 реализован на основе неинвертирующего каскада с общим коллектором.

Таким образом, чертежи фиг.9, фиг.11, фиг.12, фиг.13 и фиг.14 показывают возможные сочетания в ДУ фиг.2 узлов 13 и 10, рассмотренных на чертежах фиг.3 - фиг.8 (п.2-п.7 формулы изобретения).

На чертеже фиг.15 показана схема заявляемого ДУ фиг.10 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», соответствующая п.2 и п.7 формулы изобретения.

На чертеже фиг.16 показана частотная зависимость коэффициента усиления по напряжению Ku при разных значениях управляющего напряжения Uy=-0,5÷+0,5 В.

На чертеже фиг.17 представлена зависимость коэффициента усиления Кu ДУ фиг.15 от управляющего напряжения Uy в диапазоне средних частот. Этот график показывает, что при выбранных сопротивлениях нагрузки 38 и 39 (R38=R39=2 кОм) коэффициент Ku изменяется более чем в 40 раз. При этом максимальное значение Ku может быть увеличено путем использования в качестве нагрузки токовых зеркал.

Дифференциальный усилитель фиг.2 содержит входной параллельно-балансный каскад 1 с управляемым источником тока 2 в общей эмиттерной цепи 3, первый 4 и второй 5 токовые выходы которого связаны с первым 6 и вторым 7 двухполюсниками нагрузки и соответствующими первым 8 и вторым 9 входами выходного дифференциального каскада 10, причем выход 11 для синфазного сигнала выходного дифференциального каскада 10 подключен к управляющему входу 12 управляемого источника тока 2 в общей эмиттерной цепи 3. В схему введен преобразователь «управляющее напряжение-ток» 13, имеющий первый 14 и второй 15 синфазные выходы, связанные с соответствующими первым 4 и вторым 5 токовыми выходами входного параллельно-балансного каскада 1.

В заявляемом устройстве, соответствующем п.2 формулы изобретения (фиг.3), преобразователь «управляющее напряжение-ток» 13 содержит первый 20 и второй 21 составные транзисторы, эмиттеры которых соединены с первым 22 и вторым 23 вспомогательными источниками опорного тока через масштабирующий резистор 24, базы - подключены к соответствующим первому 16 и второму 17 входам преобразователя «управляющее напряжение-ток», причем первый 20 и второй 21 составные транзисторы выполнены по схеме с двумя коллекторами, коллекторы второго составного транзистора 21 являются первым 14 и вторым 15 синфазными выходами преобразователя «управляющее напряжение-ток» 13.

В ДУ, соответствующем п.3 формулы изобретения (фиг.4), преобразователь «управляющее напряжение-ток» 13 содержит цифроаналоговый преобразователь 25, токовый выход которого подключен к первому 26 и второму 27 вспомогательным транзисторам, причем базы первого 26 и второго 27 вспомогательных транзисторов объединены и подключены к источнику напряжения смещения 28, а коллекторы первого 26 и второго 27 вспомогательных транзисторов являются первым 14 и вторым 15 синфазными выходами преобразователя «управляющее напряжение-ток» 13.

В ДУ, соответствующем п.4 формулы изобретения (фиг.5), преобразователь «управляющее напряжение-ток» 13 содержит первый 29 и второй 30 входные транзисторы, эмиттеры которых соединены с первым 31 и вторым 32 токостабилизирующими двухполюсниками и через первый 33 и второй 34 масштабирующие резисторы соединены соответственно с первым 14 и вторым 15 синфазными выходами преобразователя «управляющее напряжение-ток» 13.

В заявляемом устройстве, соответствующем п.5 формулы изобретения (фиг.6), выходной дифференциальный каскад 10 содержит первый 35 и второй 36 двухколлекторные составные транзисторы, эмиттеры которых являются первым 8 и вторым 9 входами выходного дифференциального каскада 10, первая группа коллекторов двухколлекторных составных транзисторов 35 и 36 соединена с токостабилизирующим двухполюсником 37 и является выходом 11 для синфазного сигнала выходного дифференциального каскада 10, а вторая группа коллекторов двухколлекторных составных транзисторов 35 и 36 соединена с выходами 18 и 19 двухкаскадного дифференциального усилителя и резисторами нагрузки 38 и 39, причем базы двухколлекторных составных транзисторов 35 и 36 объединены и подключены к источнику напряжения смещения 40.

В заявляемом устройстве, соответствующем п.6 формулы изобретения (фиг.7), выходной дифференциальный каскад 10 содержит первый 41 и второй 42 входные транзисторы, эмиттеры которых подключены к первому 18 и второму 19 выходам двухкаскадного дифференциального усилителя 10 и через первый 43 и второй 44 согласующие резисторы соединены с источником опорного тока 45 и выходом 11 для синфазного сигнала выходного дифференциального каскада 10, а соответствующие базы являются первым 8 и вторым 9 входами выходного дифференциального каскада 10.

В ДУ, соответствующем п.7 формулы изобретения (фиг.8), выходной дифференциальный каскад 10 содержит первый 46 и второй 47 входные двухколлекторные составные транзисторы, базы которых являются первым 8 и вторым 9 входами выходного дифференциального каскада 10, эмиттеры - подключены к шине источника питания, первая группа коллекторов входных двухколлекторных составных транзисторов 46 и 47 является выходом 11 для синфазного сигнала выходного дифференциального каскада 10, а вторая группа коллекторов входных двухколлекторных составных транзисторов 46 и 47 соединена с выходами 18 и 19 двухкаскадного дифференциального усилителя 10 и двухполюсниками нагрузки 48 и 49, причем базы первого 46 и второго 47 входных двухколлекторных составных транзисторов являются первым 8 и вторым 9 входами выходного дифференциального каскада 10.

Схемы заявляемого устройства, представленные на чертеже фиг.9 - фиг.13, включают в себя различные сочетания выходных дифференциальных каскадов 10 (фиг.6, фиг.8) и преобразователей управляющего напряжения 13 (фиг.3 - фиг.5). По существу эти схемы поясняют особенности построения двухкаскадных дифференциальных усилителей с отрицательной обратной связью по синфазному сигналу при различных построениях его функциональных узлов 10 и 13.

В схеме фиг.14 нагрузка выходного каскада 10 реализована в частном случае на базе резисторов 48 и 49, а управляемый источник опорного тока 2 содержит р-n-р транзистор 50 и двухполюсник 51.

Рассмотрим работу ДУ фиг.2.

В статическом режиме сумма токов в узлах 5 и 4 равняется нулю. Это обеспечивается отрицательной обратной связью по синфазному сигналу, которая вводится через выходной каскад 10, на вход 12 управляемого источника опорного тока 2. При этом дифференциальный коэффициент усиления по напряжению первого каскада ДУ фиг.2 определяется отношением:

где Rн.экв - эквивалентное сопротивление в узлах 5 и 4, зависящее от внутреннего сопротивления двухполюсников 6 и 7, входного сопротивления выходного каскада 10, выходного сопротивления преобразователя 13 и выходного сопротивления транзисторов ДУ 1;

I03 - статический ток, протекающий в общей эмиттерной цепи 3;

φт≈25 мВ - температурный потенциал.

Если второй каскад 10 имеет единичное усиление по напряжению (как, например, в схеме фиг.9), то общий коэффициент усиления ДУ фиг.2 будет равен Ку входного каскада: Ku≈Ку. В ином случае Ku=Ку10, где Ку10 - коэффициент передачи напряжения выходного каскада 10.

При изменении напряжения Uy на входах 16 и 17 преобразователя 13 его выходные токи получают следующие приращения

где S15=S14=Sy - крутизна преобразования в выходные токи .

В результате в узлах 5 и 4 в первый момент нарушается баланс токов. Однако благодаря отрицательной обратной связи этот баланс снова устанавливается за счет изменения суммарного тока I03 в общей эмиттерной цепи 3 ДУ1. Так, если направления токов соответствуют чертежу фиг.2, то это приводит (для обеспечения баланса токов) к увеличению тока i3 общей эмиттерной цепи 3 на величину 2iп. В результате суммарный ток ДУ1 по цепи 3 увеличивается, что в соответствии с (1) дает увеличение Ku.

Если направления токов изменяются на противоположные, то ток I03 уменьшается, что приводит к уменьшению Ku.

Следует заметить, что благодаря новой архитектуре ДУ фиг.2 статические потенциалы точек подключения 5 и 4 преобразователя 13 оказываются выше потенциала общей эмиттерной цепи. Это позволяет обеспечить работу ДУ при малых , избежать двухъярусного включения транзисторов.

В частном случае (фиг.3) формирование синфазных токов , пропорциональных , обеспечивается дифференциальным каскадом на транзисторах 20 и 21. При этом крутизна Sy≈R-1 24, где R24 - сопротивление резистора 24.

В схеме фиг.4 управление приращениями токов () создает АЦП 25. Возможны также другие варианты формирования синфазных токов (фиг.5).

Конкретная архитектура выходного дифференциального каскада 10 (фиг.6 - фиг.8) практически не изменяет работу заявляемого ДУ, хотя и оказывает существенное влияние на параметры схемы.

Следует обратить внимание на следующие достоинства частных вариантов ДУ, показанных на чертежах фиг.9, фиг.10, фиг.11, фиг.12, фиг.13, фиг.14.

Схема фиг.9 реализована на однотипных биполярных транзисторах, что позволяет использовать для ее изготовления наиболее дешевый техпроцесс SGB25VD. Коэффициент усиления по напряжению ДУ фиг.9 определяется двухполюсниками 6 и 7 и может достигать значений 40÷60 дБ. При рациональном построении выходной цепи выходного каскада 10 схема может иметь расширенный (на 0,6 В) диапазон изменения выходного напряжения (положительное решение о выдаче патента по заявке 2007145339/09 (049670)).

ДУ фиг.9 работоспособен при напряжениях питания ±1,5 В. Входное ux и управляющее Uy напряжения привязаны к общей шине питания, что также является существенным достоинством схемы.

Схема ДУ фиг.10 реализуется по техпроцессу SGB25H2, а также техпроцессу SGB25VD при использовании полевых транзисторов в выходном каскаде 10. Существенное достоинство - наиболее широкий диапазон изменения выходного дифференциального напряжения

,

где U6.7 - статическое напряжение на двухполюсниках 6 и 7. При их выполнении в виде резисторов можно получить U6.7=80÷100 мВ.

Таким образом, при для схемы фиг.7 максимальная амплитуда выходного синусоидального напряжения может достигать величины 2,2 В. Это существенная особенность данной схемы.

Схема фиг.11 реализуется по комплементарному техпроцессу SGB25H2. На основе транзисторов 29 и 30 можно реализовать не только цепи управления усилением, но и параллельные ВЧ-каналы передачи сигнала uвx. Для этого необходимо соответствующее подключение входа 17 ко входу «Вх.1» и входа 16 ко входу «Вх.2».

ДУ фиг.13 имеет цифровое управление усилением. Благодаря транзисторам 26 и 27 обеспечивается высокая широкополосность схемы по входам «Вх.1» и «Вх.2». ДУ фиг.12 имеет такие же особенности работы и достоинства, что и схема фиг.9. ДУ фиг.13 имеет выходной каскад с rail-to-rail выходом, который обеспечивает изменение напряжений на выходах 17 и 18 от шины питания до шины питания .

Схема фиг.14 в сравнении с фиг.13 имеет более стабильный (во всем диапазоне управления) по входу «У» статический ток выходных транзисторов.

Результаты компьютерного моделирования фиг.16, фиг.17 показывают, что предлагаемый ДУ характеризуется более высокими качественными и количественными параметрами и может использоваться в устройствах с перестраиваемыми характеристиками.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Budyakov A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007. - С.106-110.

2. S.P.Voinigescu, et al., "Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth", IEEE CSICS, Techn. Digest, pp.283-286, Nov. 2005, фиг.2.

3. S.P.Voinigescu, et al., "SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz", IEEE BCTM, pp.1-8, Oct. 2006.

4. Патент США №4.274.394, фиг.2.

5. Патент США №3.619.797.

6. Патент США №3.622.902.

7. Патент США №3.440.554.

8. А. св. СССР №299013.

9. Патент Англии №1.175.329, Н3Т.

10. Патент США №3.304.512.

11. Патент США №4.371.93.

12. А.св. СССР №421105.

13. А.св. СССР №764100.

14. А.св. СССР №669471.

1. Управляемый двухкаскадный дифференциальный усилитель с отрицательной обратной связью по синфазному сигналу, содержащий входной параллельно-балансный каскад (1) с управляемым источником тока (2) в общей эмиттерной цепи (3), первый (4) и второй (5) токовые выходы которого связаны с первым (6) и вторым (7) двухполюсниками нагрузки и соответствующими первым (8) и вторым (9) входами выходного дифференциального каскада (10), причем выход (11) для синфазного сигнала выходного дифференциального каскада (10) подключен к управляющему входу (12) управляемого источника тока (2) в общей эмиттерной цепи (3), отличающийся тем, что в схему введен преобразователь «управляющее напряжение-ток» (13), имеющий первый (14) и второй (15) синфазные выходы, связанные с соответствующими первым (4) и вторым (5) токовыми выходами входного параллельно-балансного каскада (1).

2. Устройство по п.1, отличающееся тем, что преобразователь «управляющее напряжение-ток» (13) содержит первый (20) и второй (21) составные транзисторы, эмиттеры которых соединены с первым (22) и вторым (23) вспомогательными источниками опорного тока через масштабирующий резистор (24), базы подключены к соответствующим первому (16) и второму (17) входам преобразователя «управляющее напряжение-ток», причем первый (20) и второй (21) составные транзисторы выполнены по схеме с двумя коллекторами, коллекторы второго составного транзистора (21) являются первым (14) и вторым (15) синфазными выходами преобразователя «управляющее напряжение-ток» (13).

3. Устройство по п.1, отличающееся тем, что преобразователь «управляющее напряжение-ток» (13) содержит цифроаналоговый преобразователь (25), токовый выход которого подключен к первому (26) и второму (27) вспомогательным транзисторам, причем базы первого (26) и второго (27) вспомогательных транзисторов объединены и подключены к источнику напряжения смещения (28), а коллекторы первого (26) и второго (27) вспомогательных транзисторов являются первым (14) и вторым (15) синфазными выходами преобразователя «управляющее напряжение-ток» (13).

4. Устройство по п.1, отличающееся тем, что преобразователь «управляющее напряжение-ток» (13) содержит первый (29) и второй (30) входные транзисторы, эмиттеры которых соединены с первым (31) и вторым (32) токостабилизирующими двухполюсниками и через первый (33) и второй (34) масштабирующие резисторы соединены соответственно с первым (14) и вторым (15) синфазными выходами преобразователя «управляющее напряжение-ток» (13).

5. Устройство по п.1, отличающееся тем, что выходной дифференциальный каскад (10) содержит первый (35) и второй (36) двухколлекторные составные транзисторы, эмиттеры которых являются первым (8) и вторым (9) входами выходного дифференциального каскада (10), первая группа коллекторов двухколлекторных составных транзисторов (35) и (36) соединена с токостабилизирующим двухполюсником (37) и является выходом (11) для синфазного сигнала выходного дифференциального каскада (10), а вторая группа коллекторов двухколлекторных составных транзисторов (35) и (36) соединена с выходами (18) и (19) двухкаскадного дифференциального усилителя и резисторами нагрузки (38) и (39), причем базы двухколлекторных составных транзисторов (35) и (36) объединены и подключены к источнику напряжения смещения (40).

6. Устройство по п.1, отличающееся тем, что выходной дифференциальный каскад (10) содержит первый (41) и второй (42) входные транзисторы, эмиттеры которых подключены к первому (18) и второму (19) выходам двухкаскадного дифференциального усилителя (10) и через первый (43) и второй (44) согласующие резисторы соединены с источником опорного тока (45) и выходом (11) для синфазного сигнала выходного дифференциального каскада (10), а соответствующие базы являются первым (8) и вторым (9) входами выходного дифференциального каскада (10).

7. Устройство по п.1, отличающееся тем, что выходной дифференциальный каскад (10) содержит первый (46) и второй (47) входные двухколлекторные составные транзисторы, базы которых являются первым (8) и вторым (9) входами выходного дифференциального каскада (10), эмиттеры подключены к шине источника питания, первая группа коллекторов входных двухколлекторных составных транзисторов (46) и (47) является выходом (11) для синфазного сигнала выходного дифференциального каскада (10), а вторая группа коллекторов входных двухколлекторных составных транзисторов (46) и (47) соединена с выходами (18) и (19) двухкаскадного дифференциального усилителя (10) и двухполюсниками нагрузки (48) и (49), причем базы первого (46) и второго (47) входных двухколлекторных составных транзисторов являются первым (8) и вторым (9) входами выходного дифференциального каскада (10).