Устройство задержки импульсов

Иллюстрации

Показать всеИзобретение относится к импульсной технике и может быть использовано в радиолокации, радионавигации, в измерительной и вычислительной технике, в частности для имитации импульсных сигналов, отраженных от движущихся объектов. Достигаемым техническим результатом является расширение функциональных возможностей устройства за счет обеспечения имитации импульсов уводящей помехи и плавности изменения величин задержек импульсов цели и уводящей помехи. Устройство задержки импульсов содержит генератор тактовых импульсов, счетчик времени, формирователь одиночного импульса по переднему фронту импульса и формирователь одиночного импульса по заднему фронту импульса, три элемента ИЛИ, четыре элемента И, шину управления, два сумматора, два оперативных запоминающих устройства, два компаратора, два D-триггера, два делителя частоты с переменным коэффициентом деления, два регистра, устройство регулировки амплитуды импульсов и аналоговый сумматор. 1 ил.

Реферат

Изобретение относится к импульсной технике и может быть использовано в радиолокации, радионавигации, в измерительной и вычислительной технике, в частности для имитации импульсных сигналов, отраженных от движущихся объектов.

Известна цифровая регулируемая линия задержки, содержащая генератор тактовых импульсов (ГТИ), делитель частоты с переменным коэффициентом деления (ДПКД), оперативное запоминающее устройство (ОЗУ), шину управления, информационные вход и выход [авт. св. №2108659, C1 Н03Н 9/30, 9/38, 08.06.93].

Данное устройство позволяет управлять величиной задержки. Недостатком устройства является то, что изменение величины задержки может осуществляться только в начале каждого цикла работы устройства, длительность которого равна величине задержки, что приводит к искажению задержанного сигнала при непрерывно меняющейся задержке и не обеспечивает непрерывности выходного сигнала: при уменьшении задержки происходит выпадение части сигнала, длительность которого равна величине изменения задержки, при увеличении задержки - добавление сигнала с неопределенным значением. Это ограничивает функциональные возможности устройства, в частности, оно не позволяет имитировать с достаточной точностью импульсные сигналы, отраженные от движущейся цели и не обеспечивает имитацию импульсных сигналов уводящей помехи.

Известно также устройство задержки импульсов, выбранное в качестве прототипа, содержащее генератор тактовых импульсов (ГТИ), счетчик времени, вход которого соединен с первым выходом ГТИ, формирователь одиночного импульса по переднему фронту импульса (ФОПФ) и формирователь одиночного импульса по заднему фронту импульса (ФОЗФ), первые входы которых объединены и являются информационным входом устройства, а вторые входы подключены к первому выходу ГТИ, первый элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами ФОПФ и ФОЗП, шину управления, сумматор, первая группа входов которого подключена к шине управления, оперативное запоминающее устройство (ОЗУ), N разрядов шины входных данных которого соединены с группой выходов сумматора, (N+1) разряд шины входных данных ОЗУ соединен с выходом ФОПФ, вход записи (wr) ОЗУ соединен с выходом первого элемента ИЛИ, а входы синхронизации записи (wrclock) и чтения (rdclock) ОЗУ подключены соответственно к первому и второму выходам ГТИ, компаратор, первая группа входов которого объединена со второй группой входов сумматора и соединена с информационными выходами счетчика времени, а вторая группа входов компаратора соединена с N разрядами шины выходных данных ОЗУ, первый элемент И, первый вход которого подключен к выходу признака пустой памяти (empty) ОЗУ, второй вход - к выходу первого элемента ИЛИ, второй элемент ИЛИ, первый вход которого соединен с выходом первого элемента И, а выход - со входом чтения (rd) ОЗУ, второй элемент И, первый вход которого соединен с выходом компаратора и со вторым входом второго элемента ИЛИ, а второй вход - с первым выходом ГТИ, и D-триггер, информационный вход которого подключен к (N+1) разряду шины выходных данных ОЗУ, вход синхронизации - к выходу второго элемента И, а выход D-триггера является информационным выходом устройства [авт. св. №2269866, С2 Н03Н 9/30, Н03К 5/14, 29.03.04].

Данное устройство обеспечивает формирование задержанного сигнала с непрерывно меняющейся величиной задержки. Однако для обеспечения плавности изменения величины задержки при больших скоростях ее изменения на шину управления от управляющей ЭВМ необходимо передавать величину задержки с достаточно высокой частотой, что не всегда возможно. Так, например, при имитации импульсных сигналов, отраженных от движущейся цели, максимальная скорость изменения величины задержки может составлять 20 мкс/с, что соответствует скорости цели, равной 6000 м/с. При этом для обеспечения плавности изменения величины задержки дискретность ее изменения не должна превышать 0,02 мкс, что выполнимо при передаче величины задержки на шину управления от управляющей ЭВМ с частотой не менее 20/0,02=1000 Гц. Реально же частота обмена управляющей ЭВМ с контрольно-измерительной аппаратурой, имитирующей импульсные сигналы, отраженные от движущейся цели, не превышает 100 Гц, что на порядок увеличивает дискретность изменения величины задержки и не обеспечивает имитации реальных импульсов, отраженных от движущейся цели. Кроме того, данное устройство не обеспечивает имитацию импульсных сигналов уводящей помехи.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения имитации импульсов уводящей помехи и плавности изменения величин задержек импульсов цели и уводящей помехи.

Указанная цель достигается за счет того, что в устройство задержки импульсов, содержащее генератор тактовых импульсов (ГТИ), счетчик времени, вход которого соединен с первым выходом ГТИ, формирователь одиночного импульса по переднему фронту импульса (ФОПФ) и формирователь одиночного импульса по заднему фронту импульса (ФОЗФ), первые входы которых объединены и являются информационным входом устройства, а вторые входы подключены к первому выходу ГТИ, первый элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами ФОПФ и ФОЗФ, шину управления, первый сумматор, первая группа входов которого соединена с информационными выходами счетчика времени, первое оперативное запоминающее устройство (ОЗУ), N разрядов шины входных данных которого соединены с группой выходов первого сумматора, (N+1) разряд шины входных данных первого ОЗУ соединен с выходом ФОПФ, вход записи (wr) первого ОЗУ соединен с выходом первого элемента ИЛИ, а входы синхронизации записи (wrclock) и чтения (rdclock) подключены соответственно к первому и второму выходам ГТИ, первый компаратор, первая группа входов которого соединена с информационными выходами счетчика времени, а вторая группа - с N разрядами шины выходных данных первого ОЗУ, первый элемент И, первый вход которого подключен к выходу признака пустой памяти (empty) первого ОЗУ, второй вход - к выходу первого элемента ИЛИ, второй элемент ИЛИ, первый вход которого соединен с выходом первого элемента И, а выход - со входом чтения (rd) первого ОЗУ, второй элемент И, первый вход которого соединен с выходом первого компаратора и со вторым входом второго элемента ИЛИ, а второй вход - с первым выходом ГТИ, и первый D-триггер, информационный вход которого подключен к (N+1) разряду шины выходных данных первого ОЗУ, а вход синхронизации - к выходу второго элемента И, введены второй сумматор, первая группа входов которого соединена с информационными выходами счетчика времени, второе ОЗУ, N разрядов шины входных данных которого соединены с группой выходов второго сумматора, (N+1) разряд шины входных данных и входы wr, wrclock, rdclock второго ОЗУ объединены с соответствующими входами первого ОЗУ, второй компаратор, первая группа входов которого соединена с информационными выходами счетчика времени, а вторая группа - с N разрядами шины выходных данных второго ОЗУ, третий элемент И, первый вход которого подключен к выходу empty второго ОЗУ, а второй вход - к выходу первого элемента ИЛИ, третий элемент ИЛИ, первый вход которого соединен с выходом третьего элемента И, а выход - со входом rd второго ОЗУ, четвертый элемент И, первый вход которого соединен с выходом второго компаратора и со вторым входом третьего элемента ИЛИ, а второй вход - с первым выходом ГТИ, второй D-триггер, информационный вход которого подключен к (N+1) разряду шины выходных данных второго ОЗУ, а вход синхронизации - к выходу четвертого элемента И, первый и второй делители частоты с переменным коэффициентом деления (ДПКД), тактовые входы которых подключены к первому выходу ГТИ, а группы входов управления - к шине управления, первый и второй регистры, счетные входы которых подключены соответственно к выходам первого и второго ДПКД, группы входов управления и записи - к шине управления, а группы выходов регистров подключены соответственно к вторым группам входов первого и второго сумматоров, устройство регулировки амплитуды импульсов, вход которого подключен к выходу второго D-триггера, а группа входов управления - к шине управления, и аналоговый сумматор, первый вход которого соединен с выходом первого D-триггера, второй вход - с выходом устройства регулировки амплитуды импульсов, а выход аналогового сумматора является информационным выходом устройства.

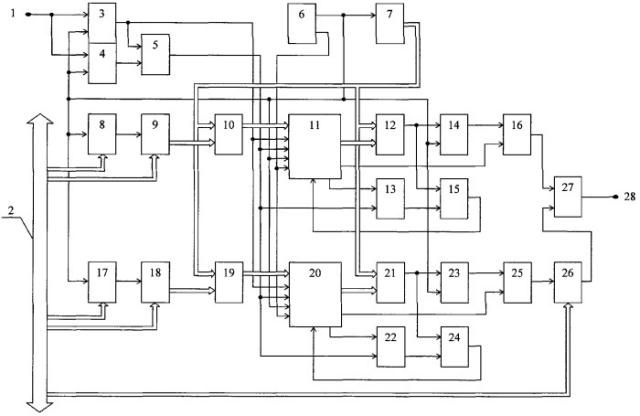

На чертеже приведена блок-схема устройства задержки импульсов, в которое входят:

1 - информационный вход;

2 - шина управления;

3 - формирователь одиночного импульса по переднему фронту импульса (ФОПФ);

4 - формирователь одиночного импульса по заднему фронту импульса (ФОЗФ);

5 - первый элемент ИЛИ;

6 - генератор тактовых импульсов (ГТИ);

7 - счетчик времени;

8 - первый делитель частоты с переменным коэффициентом деления (ДПКД);

9 - первый регистр;

10 - первый сумматор;

11 - первое оперативное запоминающее устройство (ОЗУ);

12 - первый компаратор;

13, 14 - первый и второй элементы И;

15 - второй элемент ИЛИ;

16 - первый D-триггер;

17 - второй делитель частоты с переменным коэффициентом деления (ДПКД);

18 - второй регистр;

19 - второй сумматор;

20 - второе оперативное запоминающее устройство (ОЗУ);

21 - второй компаратор;

22, 23 - третий и четвертый элементы И;

24 - третий элемент ИЛИ;

25 - второй D-триггер;

26 - устройство регулировки амплитуды импульсов;

27 - аналоговый сумматор;

28 - информационный выход.

Первые входы ФОПФ 3 и ФОЗФ 4 объединены и являются информационным входом 1 устройства. Вторые входы ФОПФ 3 и ФОЗФ 4 объединены с тактовыми входами ДПКД 8, 17, входами wrclock ОЗУ 11, 20, со вторыми входами элементов И 14, 23, со входом счетчика времени 7 и подключены к первому выходу ГТИ 6, второй выход которого соединен со входами rdclock ОЗУ 11, 20. Выход ФОПФ 3 соединен с первым входом элемента ИЛИ 5 и с (N+1) разрядами шин входных данных ОЗУ 11, 20. Выход ФОЗФ 4 соединен со вторым входом элемента ИЛИ 5, выход которого подключен ко входам wr ОЗУ 11, 20 и ко вторым входам элементов И 13, 22. Первые группы входов сумматоров 10, 19 и компараторов 12, 21 объединены и подключены к информационным выходам счетчика времени 7. Группы входов управления ДПКД 8, 17, группы входов управления и записи регистров 9, 18 и группа входов управления устройства регулировки амплитуды импульсов 26 подключены к шине управления 2. Выход ДПКД 8 соединен с счетным входом регистра 9, группа выходов которого подключена ко второй группе входов сумматора 10. Выход ДПКД 17 соединен с счетным входом регистра 18, группа выходов которого подключена ко второй группе входов сумматора 19. Группы выходов сумматоров 10, 19 соединены соответственно с N разрядами шин входных данных ОЗУ 11, 20. Первые входы элементов И 13, 22 соединены соответственно с выходами empty ОЗУ 11, 20, а выходы элементов И 13, 22 соединены соответственно с первыми входами элементов ИЛИ 15, 24. Группы N разрядов шин выходных данных ОЗУ 11, 20 соединены соответственно со вторыми группами входов компараторов 12, 21. Выход компаратора 12 соединен с первым входом элемента И 14 и со вторым входом элемента ИЛИ 15, выход которого подключен ко входу rd ОЗУ 11. Выход компаратора 21 соединен с первым входом элемента И 23 и со вторым входом элемента ИЛИ 24, выход которого подключен ко входу rd ОЗУ 20. Входы синхронизации D-триггеров 16, 25 подключены соответственно к выходам элементов И 14, 23, а информационные входы - соответственно к (N+1) разрядам шин выходных данных ОЗУ 11, 20. Выход D-триггера 16 соединен с первым входом аналогового сумматора 27, второй вход которого подключен к выходу устройства регулировки амплитуды импульсов 26, вход которого соединен с выходом D-триггера 25. Выход аналогового сумматора 27 является информационным выходом 28 устройства.

ГТИ 6 имеет два выхода, на которых вырабатываются тактовые импульсы, сдвинутые на 1/2 периода относительно друг друга. Это необходимо для разделения во времени процессов записи и чтения ОЗУ 11, 20. Частота ГТИ 6 определяет точность формирования задержанного сигнала.

Счетчик времени 7 формирует код текущего времени с ценой младшего разряда, равной периоду тактовых импульсов ТГТИ. Полное время пересчета счетчика времени 7 должно быть не менее максимального времени задержки ТЗАД, то есть число разрядов N счетчика времени 7 должно определяться следующей формулой:

Такое же число разрядов N должны иметь регистры 9, 18, сумматоры 10, 19 и компараторы 12, 21. ОЗУ 11, 20 должны иметь на один разряд больше (N+1).

В качестве ОЗУ 11, 20 применена память типа FIFO, имеющая раздельные шины входных и выходных данных, причем, выходная шина данных должна быть регистровой, раздельные входы записи/чтения (wr/rd) и синхронизации записи/чтения (wrclock/rdclock) и выход признака пустой памяти (empty).

Регистры 9, 18 имеют счетные входы и группы входов управления и записи, по которым передаются команды направления счета (прямой/обратный) и значения начальной задержки.

Устройство регулировки амплитуды импульсов 26, в качестве которого использован умножающий ЦАП, обеспечивает установку амплитуды импульсов двоичным кодом, поступающим на группу входов управления с шины управления 2.

Устройство работает следующим образом. Входные импульсы с информационного входа 1 поступают на первые входы ФОПФ 3 и ФОЗФ 4, которые формируют одиночные импульсы по переднему и заднему фронтам входных импульсов, привязанные к импульсам первого выхода ГТИ 6 и имеющие длительность ТГТИ. Эти импульсы через элемент ИЛИ 5 поступают на входы wr ОЗУ 11 и 20, в результате, в моменты их поступления в ОЗУ 11 и 20 будут записываться данные, поступающие в шины входных данных ОЗУ 11 и 20. В N разрядов шин входных данных ОЗУ 11 и 20 поступает информация соответственно с выходов сумматоров 10 и 19, которые суммирует код текущего времени, поступающий с счетчика времени 7, и коды величин текущих задержек, поступающих соответственно с регистров 9 и 18, причем, с регистра 9 поступает код величины текущей задержки импульсов цели, а с регистра 18 - код величины текущей задержки импульсов уводящей помехи. В (N+1) разряды шин входных данных ОЗУ 11 и 20 записывается сигнал с выхода ФОПФ 3. Этот разряд служит признаком фронта входного импульса: при переднем фронте входного импульса в (N+1) разряды шин входных данных ОЗУ 11 и 20 записывается "1", при заднем - "0". Таким образом, в моменты поступления фронтов входных импульсов последовательно в ячейки ОЗУ 11 и 20 будут записываться коды текущего времени, увеличенные соответственно на величину текущей задержки импульсов цели (в ОЗУ 11) и на величину текущей задержки импульсов уводящей помехи (в ОЗУ 20), и признак фронта. Считанные по шинам выходных данных ОЗУ 11 и 20 N разрядов поступают соответственно на вторые группы входов компараторов 12 и 21, на первые группы входов которых поступает код текущего времени с счетчика времени 7. В момент равенства кода текущего времени и кода времени, считанного из ОЗУ 11 или 20, на выходе соответствующего компаратора 12 или 21 формируется единичный сигнал, который через соответствующий элемент И 14 или 23, синхронизирующий этот сигнал с импульсами первого выхода ГТИ 6, поступает соответственно на вход синхронизации D-триггера 16 или 25, на информационные входы которых поступают соответственно сигналы признаков фронта с (N+1) разрядов шин выходных данных ОЗУ 11, 20. Если сигнал признака фронта равен "1", то соответствующий D-триггер 16 или 25 переключится в "1" и сформируется передний фронт выходного импульса, иначе D-триггер 16 или 25 переключится в "0" и сформируется задний фронт выходного импульса. Сигналы с выходов компараторов 12, 21 одновременно поступают через соответствующие элементы ИЛИ 15, 24 на входы rd ОЗУ 11, 20 для считывания следующей ячейки соответствующего ОЗУ. Если память ОЗУ 11 или 20 пустая, что может быть после включения устройства до прихода первого входного импульса, или, в случае, когда величина задержки меньше периода входных импульсов, на выходе empty соответствующего ОЗУ вырабатывается сигнал "1", который через элементы И 13, 22 и ИЛИ 15, 24 поступает на вход rd ОЗУ 11 или 20, что обеспечивает чтение соответствующего ОЗУ сразу же после поступления первого фронта входного импульса. Таким образом, на выходе D-триггера 16 формируются фронты импульсов, задержка которых равна текущей задержке импульсов цели, поступающей с регистра 9, а на выходе D-триггера 25 формируются фронты импульсов, задержка которых равна текущей задержке импульсов уводящей помехи, поступающей с регистра 18.

В прототипе величина текущей задержки поступала на сумматор 10 непосредственно с шины управления 2 и для плавности ее изменения необходимо было передавать величину задержки с достаточно высокой частотой, особенно при высоких скоростях изменения задержки. В предлагаемом устройстве по шине управления 2 в регистры 9 и 18 записываются лишь начальные значения задержек, а изменения их происходит за счет поступления импульсов на счетные входы регистров 9 и 18 соответственно с ДПКД 8 и 17. Каждый входной импульс увеличивает или уменьшает, в зависимости от установленного режима направления счета соответствующего регистра 9 или 18, величину задержки на единицу младшего разряда, соответствующую периоду тактовых импульсов ТГТИ, что обеспечивает плавность ее изменения при любой скорости изменения задержки и максимально приближает характеристики формируемых импульсов к импульсам, отраженных от движущейся цели, и импульсам уводящей помехи. Скорость изменения задержки V (мкс/с) определяется частотой импульсов FДПКД, поступающих на счетный вход регистра 9 или 18 с ДПКД 8 или 17 в соответствии со следующей формулой:

FДПКД в свою очередь определяется коэффициентом деления NДКПД ДПКД 8 или 17 и равна:

Таким образом

Значения начальной задержки и NДКПД передаются по шине управления 2 в регистр 9 и в ДПКД 8 для импульсов цели и в регистр 18 и в ДПКД 17 для импульсов уводящей помехи.

Импульсы уводящей помехи с выхода D-триггера 25 поступают на устройство регулировки амплитуды импульсов 26 для изменения уровня импульсов уводящей помехи относительно уровня импульсов цели, и далее на второй вход аналогового сумматора 27, на первый вход которого поступают импульсы цели с выхода D-триггера 16. Аналоговый сумматор 27 суммирует импульсы цели и уводящей помехи и передает их на информационный выход 28 устройства.

Таким образом, введение новых элементов с указанными связями позволяет расширить область применения предлагаемого устройства за счет обеспечения имитации импульсных сигналов уводящей помехи и плавности изменения величин задержек импульсов цели и уводящей помехи.

Устройство задержки импульсов, содержащее генератор тактовых импульсов, счетчик времени, вход которого соединен с первым выходом генератора тактовых импульсов, формирователь одиночного импульса по переднему фронту импульса и формирователь одиночного импульса по заднему фронту импульса, первые входы которых объединены и являются информационным входом устройства, а вторые входы подключены к первому выходу генератора тактовых импульсов, первый элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами формирователя одиночного импульса по переднему фронту импульса и формирователя одиночного импульса по заднему фронту импульса, шину управления, первый сумматор, первая группа входов которого соединена с информационными выходами счетчика времени, первое оперативное запоминающее устройство, N разрядов шины входных данных которого соединены с группой выходов первого сумматора, (N+1)-й разряд шины входных данных первого оперативного запоминающего устройства соединен с выходом формирователя одиночного импульса по переднему фронту импульса, вход записи первого оперативного запоминающего устройства соединен с выходом первого элемента ИЛИ, а входы синхронизации записи и чтения подключены соответственно к первому и второму выходам генератора тактовых импульсов, первый компаратор, первая группа входов которого соединена с информационными выходами счетчика времени, а вторая группа - с N разрядами шины выходных данных первого оперативного запоминающего устройства, первый элемент И, первый вход которого подключен к выходу признака пустой памяти первого оперативного запоминающего устройства, второй вход - к выходу первого элемента ИЛИ, второй элемент ИЛИ, первый вход которого соединен с выходом первого элемента И, а выход - со входом чтения первого оперативного запоминающего устройства, второй элемент И, первый вход которого соединен с выходом первого компаратора и со вторым входом второго элемента ИЛИ, а второй вход - с первым выходом генератора тактовых импульсов, и первый D-триггер, информационный вход которого подключен к (N+1)-ому разряду шины выходных данных первого оперативного запоминающего устройства, а вход синхронизации - к выходу второго элемента И, отличающееся тем, что в него введены второй сумматор, первая группа входов которого соединена с информационными выходами счетчика времени, второе оперативное запоминающее устройство, N разрядов шины входных данных которого соединены с группой выходов второго сумматора, (N+1)-й разряд шины входных данных и входы записи, синхронизации записи и синхронизации чтения второго оперативного запоминающего устройства объединены с соответствующими входами первого оперативного запоминающего устройства, второй компаратор, первая группа входов которого соединена с информационными выходами счетчика времени, а вторая группа - с N разрядами шины выходных данных второго оперативного запоминающего устройства, третий элемент И, первый вход которого подключен к выходу признака пустой памяти второго оперативного запоминающего устройства, а второй вход - к выходу первого элемента ИЛИ, третий элемент ИЛИ, первый вход которого соединен с выходом третьего элемента И, а выход - со входом чтения второго оперативного запоминающего устройства, четвертый элемент И, первый вход которого соединен с выходом второго компаратора и со вторым входом третьего элемента ИЛИ, а второй вход - с первым выходом генератора тактовых импульсов, второй D-триггер, информационный вход которого подключен к (N+1)-ому разряду шины выходных данных второго оперативного запоминающего устройства, а вход синхронизации - к выходу четвертого элемента И, первый и второй делители частоты с переменным коэффициентом деления, тактовые входы которых подключены к первому выходу генератора тактовых импульсов, а группы входов управления - к шине управления, первый и второй регистры, счетные входы которых подключены соответственно к выходам первого и второго делителей частоты с переменным коэффициентом деления, группы входов управления и записи - к шине управления, а группы выходов регистров подключены соответственно к вторым группам входов первого и второго сумматоров, устройство регулировки амплитуды импульсов, вход которого подключен к выходу второго D-триггера, а группа входов управления - к шине управления, и аналоговый сумматор, первый вход которого соединен с выходом первого D-триггера, второй вход - с выходом устройства регулировки амплитуды импульсов, а выход аналогового сумматора является информационным выходом устройства.